- •Индивидуальное задание на кп Вариант 15

- •Содержание

- •Введение

- •Компаратор

- •Аналоговые компараторы.

- •Аналоговый интегральный компаратор

- •Стробируемый двухпороговый компаратор.

- •Двухпороговый компаратор на одном операционном усилителе.

- •Триггер.

- •Классификация триггеров.

- •Выводы по литературному обзору.

- •Двухпороговый компаратор.

- •Двухпороговый компаратор-индикатор температуры.

- •Стробируемый компаратор (индикатор температуры).

- •Новый двухпороговый компаратор Texas Instruments для контроля напряжения питания.

- •Расчет широкополосного дифференциального усилителя (компаратор на оу).

- •Построение лачх и лфчх.

- •Заключение.

- •Список использованной литературы.

- •Приложение а.

Стробируемый двухпороговый компаратор.

Компаратор называется стробируемым, если выходной сигнал при отсутствии стробирующего импульса сохраняет значение, которое было при наличии стробирующегоимпульса.

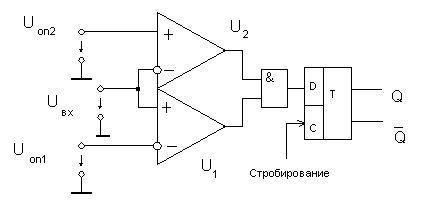

Выполняется на основе двухпорогового компаратора (состояшего из двух компараторов с индивидуальным порогом срабатывания и схемы логисеского умножения) и D-триггера (Приложение Б), устанавливающего новое состояние по фронту или срезу синхроимпульса.

Данный компаратор фиксирует, находится ли входное напряжение между двумя заданными пороговыми напряжениями или вне этого диапазона. Для реализации такой функции выходные сигналы двух компараторов необходимо подвергнуть операции логического умножения.Из-за инвертирования сигнала на выходе логического элемента единичный уровень сигнала будет иметь место тогда, когда выполняется условие UBX>UВТО , UBX<UНТО. UВТО верхний порог срабатывания, UНТО- нижний порог срабатывания.

Вход стробирования может использоваться для сохранения данных на выходах компаратора. При появлении в момент времени t0 напряжения высокого уровня на входе стробирования компаратор перестает реагировать на изменения сигналов на аналоговых входах и сохраняет выходные уровни , действовавшие на момент t0. Для уверенного запоминания и сохранения данных на выходе входной разностный сигнал должен находиться в определенном (ненулевом) состоянии, по крайней мере, в течении времени tС до момента t0 и должен оставаться таковым в течении времени tН после указанного момента. После подачи на вход стробирования низкого уровня новые выходные данные появляются примерно через 5-8 нс.

Рисунок 10 – Схема стробируемого двухпорогового компаратора

Двухпороговый компаратор на одном операционном усилителе.

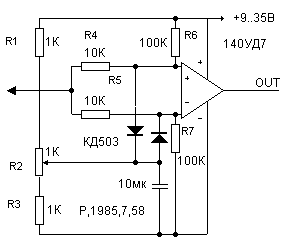

Наиболее часто двухпороговый компаратор строят на двух ОУ и логического элемента «И». На Рисунок 9 приведена схема, позволяющая обойтись всего одним ОУ.

Рисунок 9 - Двухпороговый компаратор на одном ОУ

Необходимые уровни срабатывания компаратора устанавливают резистором R2. При этомдиод VD2 открыт, а VD1 остается закрытым до тех пор, пока входное напряжение меньше напряжения на движке резистора R2. Так как напряжение на инвертирующем входе ОУ в этом случае выше, чем на неинвертирующем, на выходе ОУ устанавливается уровень логического 0. При приближении входного напряжения к уровню, заданному резистором R2, диод VD2 закрывается, полярность напряжения между входами ОУ становится противоположной и на выходе ОУ появляется напряжение логической 1, близкое к напряжению питания.

Диод VD1 открывается в тот момент, когда входное напряжение превысит заданное примерно на 0,7 В. Поскольку напряжение на неинвертирующем входе после этого увеличиваться не может, а на инвертирующем продолжает расти, полярность напряжения между входами ОУ изменяется снова и на его выходе вновь возникает сигнал логического 0.

При указанных на схеме номиналах элементов и напряжении питания +9 В интервал входных напряжений, соответствующих логической 1 на выходе – примерно 2..2,5 В, нижний порог срабатывания можно установить в пределах 1,5..5 В, верхний – в пределах 4..7,5 В. Уровни логического 0 и 1равны соответственно 1,9 и 8,5 В, что позволяет использовать компаратор для управления КМОП-микросхемами.