- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.5. Комбінаційні цифрові пристрої.

Як вже зазначалось, комбінаційними називаються такі логічні пристрої, вихідні сигнали яких однозначно визначаються вхідними сигналами (комбінацією вхідних сигналів) в даний момент часу. Такі пристрої ще називають елементами із жорсткою логікою.

4.5.1 Дешифратор.

Дешифратором називається комбінаційна схема, яка має n входів і до 2n виходів, і, яка перетворює n–розрядний двійковий код слова у сигнал, який виникає тільки на одному відповідному поданому коду певному виході.

Дешифратор

уявляє собою сукупність схем І,

на входи яких подаються комбінації

прямих і інверсних значень двійкових

змінних – х1,

![]() ,

х2,

,

х2,

![]() ,

…, хn,

,

…, хn,

![]() ,

кожна з яких може мати значення 0 або 1.

Вихідний сигнал 1 з’являється на виході

тільки однієї з схем, в той час як на

виходах інших схем дешифратора

зберігається вихідний сигнал 0. В таблиці

4.5 відображені можливі стани дешифратора

на три входи (n = 3)

і вісім (23)

виходів.

,

кожна з яких може мати значення 0 або 1.

Вихідний сигнал 1 з’являється на виході

тільки однієї з схем, в той час як на

виходах інших схем дешифратора

зберігається вихідний сигнал 0. В таблиці

4.5 відображені можливі стани дешифратора

на три входи (n = 3)

і вісім (23)

виходів.

Таблиця 4.5.

Таблиця станів дешифратора на три входи і вісім виходів.

Комбінації вхідних сигналів |

Комбінації вихідних сигналів |

|||||||||

х1 |

х2 |

х3 |

y0 |

y1 |

y2 |

y3 |

y4 |

y5 |

y6 |

y7 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Виходи

дешифратора мають нумерацію, яка

співпадає з десятковим уявленням

двійкового числа від 0 до (n – 1).

Якщо, наприклад, слово на вході має код

101 (табл. 4.5), то одиничний сигнал буде

тільки на п’ятому виході дешифратора,

тобто y5 = 1.

Це досягається тим, що на відповідну

схему І5

надходить код х1 ![]() х3

(х1

= 1,

= 1,

х3 = 1),

тобто всі сигнали дорівнюють 1, в той

час як інші схеми І

такої одиничної вхідної комбінації не

мають і на їх виходах утворюються логічні

0.

х3

(х1

= 1,

= 1,

х3 = 1),

тобто всі сигнали дорівнюють 1, в той

час як інші схеми І

такої одиничної вхідної комбінації не

мають і на їх виходах утворюються логічні

0.

Ч исло

елементів І

одноступеневого дешифратора визначається

числом виходів.

исло

елементів І

одноступеневого дешифратора визначається

числом виходів.

На рис. 4.32 показані умовні позначення лінійних дешифраторів: а) – дешифратор з прямими входами; б) – дешифратор з парафазними входами.

За способом організації дешифрації слова дешифратори поділяються на одноступіневі (лінійні) та багатоступіневі (прямокутні, пірамідальні).

За типом елементів, що використовуються розрізняють дешифратори діодні, транзисторні, магнітні. На цих елементах будуються схеми І, які і використовуються в дешифраторах.

Схеми дешифраторів можуть бути у вигляді окремих інтегральних схем або входити до структури деяких ВІС, наприклад, інтегральних схем постійної та оперативної пам’яті. Повний дешифратор – дешифратор, що має стільки виходів m, скільки різних значень може мати n-розрядне двійкове число на його входах, тобто m = 2n.

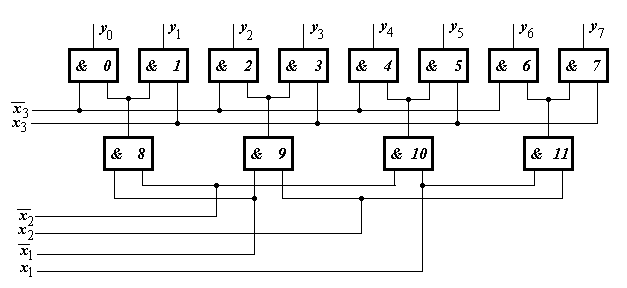

Рис. 4.33.

На рис. 4.33 наведена схема одноступеневого лінійного дешифратора на три входи, у якого число виходів m = 23 = 8.

Для

схемної реалізації кожного виходу

дешифратора достатньо мати один логічний

елемент І

з числом входів, рівним числу розрядів

слова, що надходить на дешифратор (числу

змінних). Прямі та інверсні значення

змінних, як правило, надходять на входи

дешифратора з прямих та інверсних

виходів тригерів регістра (далі буде),

на якому записана вхідна комбінація

змінних. Кожний вихід дешифратора

набуває значення 1 (збудження) тільки

при одній певній комбінації вхідних

змінних х1÷

х3

та їх інверсних значень

![]() .

.

Якщо довжина двійкового слова, що дешифрується, більше можливого числа входів елементів І, то використовують багатоступеневу (каскадну) будову дешифратора.

Каскадне включення елементів І можна здійснити двома способами. В залежності від вибраного способу каскадування дешифратори поділяються на прямокутні та пірамідальні.

В прямокутному (матричному) дешифраторі слово, що дешифрується, розділене на кілька підслів. Підслова дешифруються на окремих лінійних дешифраторах, утворюючи вихідні значення, які називають частковими. Ця група лінійних дешифраторів уявляє собою перший каскад прямокутного дешифратора. В будь-якому наступному каскаді виконується операція кон’юнкції часткових вихідних значень, утворених лінійними дешифраторами попереднього каскаду.

Рис. 4.34.

Приклад

схемної реалізації двоступеневого

матричного дешифратора на чотири входи

і шістнадцять виходів наведена на рис.

4.34. Тут дешифратори, на входи яких

безпосередньо надходять сигнали змінних

х0,

х1

![]() та х2,

х3

та х2,

х3

![]() ,

утворюють перший каскад дешифрації.

Шістнадцять схем І,

на виходах яких утворюються сигнали

у0,

у1,

…, у15

складають матрицю другого каскаду.

,

утворюють перший каскад дешифрації.

Шістнадцять схем І,

на виходах яких утворюються сигнали

у0,

у1,

…, у15

складають матрицю другого каскаду.

Схема матричного дешифратора на 1024 виходи наведена на рис. 4.35, де ЛД, МД – лінійні і матричні дешифратори відповідно. Припустимо, що необхідно дешифрувати 10-розрядне слово n = 10. Це слово розділяється на три групи: n1 = 4, n2 = 4, n3 = 2. Тоді кожний з трьох лінійних дешифраторів першого каскаду дешифрації, буде мати 2n1 = 16, 2n2 = 16, 2n3 = 4 виходів відповідно.

Рис. 4.35.

Виходи першого і другого лінійних дешифраторів подаються на двовхідні схеми І другої ступені прямокутного дешифратора, які утворюють його підсхему на 256 виходів. Кількість виходів другої ступені визначається за формулою m2 = 2n1 2n2 = 2n1+n2.

Виходи другої ступені матричного дешифратора і першої ступені третього лінійного дешифратора подаються на двовхідні схеми третьої ступені матричного дешифратора, які утворюють його підсхему на 1024 виходів. Кількість виходів третьої ступені визначається за формулою m3 = m22n3 = 2n1+n2+n3 = 1024.

Пірамідальний дешифратор в кожному каскаді утворює часткові вихідні значення як кон’юнкції часткових вихідних значень попередніх каскадів і цифри одного з розрядів, що ще не брали участі в утворені попередніх часткових значень. Приклад схеми пірамідального дешифратора на три входи і вісім виходів наведена на рис. 4.36, а схеми синхронного1 пірамідального дешифратора на чотири входи, побудованого на окремих ІС наведена на рис. 4.37.

Рис. 4.36.

Першу ступінь дешифратора (рис. 4.37) складає дешифратор з двома входами (х0, х1) і відповідно чотирма виходами. Другу ступінь – чотири дешифратора, кожний з яких також має по два входи і по чотири виходи. Перша група розрядів дешифрується на дешифраторі першої ступені під дією сигналу синхронізації С. Вихідні сигнали з дешифратора першої ступені використовуються як синхронізуючі сигнали для дешифраторів другої ступені. На кожний дешифратор другої ступені подається одна і та ж група розрядів (х2, х3), але дешифрується тільки на тому дешифраторі, на який надійшов сигнал синхронізації від першої ступені.

Рис. 4.37.

Якщо вхідне слово складається з більшого числа розрядів, то виходи дешифратора другої ступені можуть бути використані для синхронізації дешифраторів наступної ступені і т.д.