- •Глава 1. Введение в информатику

- •1.1. Что такое инфоpматика?

- •1.2. Что такое информация?

- •1.3. В каком виде существует информация?

- •1.4. Как передаётся информация?

- •1.5. Как измеряется количество информации?

- •1.6. Что можно делать с информацией?

- •1.7. Какими свойствами обладает информация?

- •1.8. Что такое обработка информации?

- •1.9. Что такое информационные ресурсы и информационные технологии?

- •1.10. Что понимают под информатизацией общества?

- •1.11. Вопросы для самоконтроля

- •1.12. Упражнения

- •Ответы — Раздел 1. Введение в информатику

- •Глава 2. Общие принципы организации и работы компьютеров

- •Глава 2. Общие принципы организации и работы компьютеров

- •2.1. Что такое компьютер?

- •2.2. Как устроен компьютер?

- •2.3. На каких принципах построены компьютеры?

- •1. Принцип программного управления. Из него следует, что программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности.

- •2.4. Что такое команда?

- •2.5. Как выполняется команда?

- •2.6. Что такое архитектура и структура компьютера?

- •2.7. Что такое центральный процессор?

- •2.8. Как устроена память?

- •2.9. Какие устройства образуют внутреннюю память?

- •1. Оперативная память

- •3. Специальная память

- •2.10. Какие устройства образуют внешнюю память?

- •1. Накопители на гибких магнитных дисках

- •2. Накопители на жестких магнитных дисках

- •3. Накопители на компакт-дисках

- •4. Записывающие оптические и магнитооптические накопители

- •5. Накопители на магнитной ленте (стримеры) и накопители на сменных дисках

- •2.11. Что такое аудиоадаптер?

- •2.12. Что такое видеоадаптер и графический акселератор?

- •2.13. Что такое клавиатура?

- •2.14. Что такое видеосистема компьютера?

- •1. Монитор на базе электронно-лучевой трубки

- •2. Жидкокристаллические мониторы

- •3. Сенсорный экран

- •2.15. Что такое принтер, плоттер, сканер?

- •2.16. Что такое модем и факс-модем?

- •2.17. Что такое манипуляторы?

- •2.18. Как устроен компьютер?

- •2.19. Какие основные блоки входят в состав компьютера?

- •2.20. Что собой представляет системная плата?

- •2.21. Как организуется межкомпьютерная связь?

- •2.22. Что такое компьютерная сеть?

- •Наиболее распространенные виды топологий сетей:

- •2.23. Как соединяются между собой устройства сети?

- •2.24. Как классифицируют компьютерные сети по степени географического распространения?

- •2.25. Как соединяются между собой локальные сети?

- •2.26. Как работают беспроводные сети?

- •2.27. Что такое сеть Интернет и как она работает?

- •Как можно связаться с Интернет ?

- •Как связываются между собой сети в Интернет?

- •Каким образом пакет находит своего получателя ?

- •2.28. Основные возможности, предоставляемые сетью Интернет

- •1. World Wide Web — главный информационный сервис.

- •2. Электронная почта.

- •3. Cистема телеконференций Usenet (от Users Network).

- •4. Системы информационного поиска сети Интернет.

- •Системы, основанные на предметных каталогах.

- •Автоматические индексы.

- •5. Программа пересылки файлов Ftp.

- •6. Программа удалённого доступа Telnet.

- •2.29. Что такое мультимедиа и мультимедиа-компьютер?

- •2.30. Вопросы для самоконтроля

- •Глава 3. Классификация компьютеров

- •3.1. По каким критериям классифицируют компьютеры?

- •3.2. На чем основана классификация по поколениям?

- •3.3. Краткая историческая справка

- •3.4. Какие компьютеры относятcя в первому поколению?

- •3.5. Какие компьютеры относятся ко второму поколению?

- •3.6. В чем особенности компьютеров третьего поколения?

- •3.7. Что характерно для машин четвёртого поколения?

- •3.8. Какими должны быть компьютеры пятого поколения?

- •3.9. На какие типы делятся компьютеры по условиям эксплуатации?

- •3.10. На какие типы делятся компьютеры по производительности и характеру использования?

- •3.11. Какие существуют типы портативных компьютеров?

- •3.12. Вопросы для самоконтроля

- •Глава 4. Арифметические основы компьютеров

- •4.1. Что такое система счисления?

- •4.2. Как порождаются целые числа в позиционных системах счисления?

- •4.3. Какие системы счисления используют специалисты для общения с компьютером?

- •4.4. Почему люди пользуются десятичной системой, а компьютеры — двоичной?

- •4.5. Почему в компьютерах используются также восьмеричная и шестнадцатеричная системы счисления?

- •4.6. Как перевести целое число из десятичной системы в любую другую позиционную систему счисления?

- •4.7. Как пеpевести пpавильную десятичную дpобь в любую другую позиционную систему счисления?

- •4.8. Как пеpевести число из двоичной (восьмеpичной, шестнадцатеpичной) системы в десятичную?

- •4.9. Сводная таблица переводов целых чисел из одной системы счисления в другую

- •4.10. Как производятся арифметические операции в позиционных системах счисления?

- •4.11. Как представляются в компьютере целые числа?

- •4.12. Как компьютер выполняет арифметические действия над целыми числами? Сложение и вычитание

- •Умножение и деление

- •4.13. Как представляются в компьютере вещественные числа?

- •4.14. Как компьютер выполняет арифметические действия над нормализованными числами?

- •Сложение и вычитание

- •Умножение

- •Деление

- •4.15. Упражнения

- •Ответы — Раздел 4. Арифметические основы компьютеров

- •Глава 5. Логические основы компьютеров

- •5.1. Что такое алгебра логики?

- •5.2. Что такое логическая формула?

- •5.3. Какая связь между алгеброй логики и двоичным кодированием?

- •5.4. В каком виде записываются в памяти компьютера и в регистрах процессора данные и команды?

- •5.5. Что такое логический элемент компьютера?

- •5.6. Что такое схемы и, или, не, и—не, или—не?

- •5.7. Что такое триггер?

- •5.8. Что такое сумматор?

- •5.9. Какие основные законы выполняются в алгебре логики?

- •Основные законы алгебры логики

- •5.10. Как составить таблицу истинности?

- •5.11. Как упростить логическую формулу?

- •5.12. Что такое переключательная схема?

- •5.13. Как решать логические задачи?

- •I. Решение логических задач средствами алгебры логики

- •II. Решение логических задач табличным способом

- •III. Решение логических задач с помощью рассуждений

- •5.14. Упражнения

- •Ответы — Раздел 5. Логические основы компьютеров

- •5.5. Являются отрицаниями друг друга: б), г), д), к); не являются отрицаниями друг друга: а), в), е), ж), з), и).

- •5.6. Истинны: б), в), г), з), к), и); ложны: а), д), е), ж).

- •5.13. Тождественно истинные: а), в), е); тождественно ложные: г), д), ж).

- •Глава 6. Программное обеспечение компьютеров

- •6.1. Что такое программное обеспечение?

- •6.2. Как классифицируется программное обеспечение?

- •6.3. Какие программы называют прикладными?

- •6.4. Какова роль и назначение системных программ?

- •6.5. Что такое операционная система?

- •6.6. Что такое файловая система ос?

- •6.7. Какова структура операционной системы ms dos?

- •6.8. Что такое программы-оболочки?

- •6.9. Что собой представляют операционные системы Windows, Unix, Linux? Операционные системы Windows

- •Операционная система Unix

- •Операционная система Linux

- •6.10. Что такое транслятор, компилятор, интерпретатор?

- •6.11. Что такое системы программирования?

- •6.12. Для чего нужны инструментальные программы?

- •6.13. Что такое текстовый редактор?

- •6.14. Что такое графический редактор?

- •6.15. Каковы возможности систем деловой и научной графики?

- •6.16. Что такое табличный процессор?

- •6.17. Что такое системы управления базами данных?

- •6.18. Что такое библиотеки стандартных подпрограмм?

- •6.19. Что такое пакеты прикладных программ?

- •6.20. Что такое интегрированные пакеты программ?

- •6.21. Что такое органайзеры?

- •6.22. Что такое сетевое программное обеспечение?

- •Функции и характеристики сетевых операционных систем (ос)

- •6.23. Вопросы для самоконтроля.

- •Глава 7. Алгоритмы. Алгоритмизация. Алгоритмические языки

- •7.1. Что такое алгоритм?

- •7.2. Что такое "Исполнитель алгоритма"?

- •7.3. Какими свойствами обладают алгоpитмы?

- •7.4. В какой форме записываются алгоритмы?

- •7.5. Что такое словесный способ записи алгоритмов?

- •7.6. Что такое графический способ записи алгоритмов?

- •7.7. Что такое псевдокод?

- •7.8. Как записываются алгоритмы на школьном алгоритмическом языке? Основные служебные слова

- •Команды школьного ая

- •Пример записи алгоритма на школьном ая

- •7.9. Что такое базовые алгоритмические структуры?

- •7.10. Какие циклы называют итерационными?

- •7.11. Что такое вложенные циклы?

- •Пример вложенных циклов для

- •Пример вложенных циклов пока

- •7.12. Чем отличается программный способ записи алгоритмов от других?

- •7.13.Что такое уровень языка программирования?

- •7.14. Какие у машинных языков достоинства и недостатки?

- •7.15. Что такое язык ассемблера?

- •7.16. В чем преимущества алгоритмических языков перед машинными?

- •7.17. Какие компоненты образуют алгоритмический язык?

- •7.18. Какие понятия используют алгоритмические языки?

- •7.19. Что такое стандартная функция?

- •7.20. Как записываются арифметические выражения?

- •Примеры записи арифметических выражений

- •7.21. Как записываются логические выражения?

- •Примеры записи логических выражений, истинных при выполнении указанных условий.

- •7.22. Упражнения

- •Ответы — Раздел 7. Алгоритмы. Алгоритмизация. Алгоритмические языки

- •Глава 8. Технология подготовки и решения задач с помощью компьютера

- •8.1. Какие этапы включает в себя решение задач с помощью компьютера?

- •8.2. Что называют математической моделью?

- •8.3. Какие основные этапы содержит процесс разработки программ?

- •8.4. Как проконтролировать текст программы до выхода на компьютер?

- •8.5. Для чего нужны отладка и тестирование?

- •8.6. В чем заключается отладка?

- •8.7. Что такое тест и тестирование?

- •8.8. Какими должны быть тестовые данные?

- •8.9. Из каких этапов состоит процесс тестирования?

- •8.10. Каковы характерные ошибки программирования?

- •8.11. Является ли отсутствие синтаксических ошибок свидетельством правильности программы?

- •8.12. Какие ошибки не обнаруживаются транслятором?

- •8.13. В чем заключается сопровождение программы?

- •8.14. Вопросы для самоконтроля

- •8.15. Упражнения

- •Глава 9. Применения информатики и компьютерной техники

- •9.1. Как используются компьютеры в быту?

- •9.2. Что такое системы автоматизированного проектирования (сапр)?

- •9.3. Что такое автоматизированные системы научных исследований (асни)?

- •9.4. Какая взаимосвязь между асни и сапр?

- •9.5. Что такое базы знаний и экспертные системы?

- •9.6. Как используются компьютеры в административном управлении?

- •9.7. Какую роль играют компьютеры в обучении?

- •9.8. Какую роль играют компьютеры в управлении технологическими процессами?

- •9.9. Какую роль играют компьютеры в медицине?

- •9.10. Как используются компьютеры в торговле?

- •9.11. Что такое электронные деньги?

- •9.12. Как применяются компьютеры в сельском хозяйстве?

- •9.13. Вопросы для самоконтроля

- •Числовое кодирование

- •Лекция 11 "компьютерные вирусы"...……………………………………………………....133 Лекция 9.1 основы числового кодирования

- •Схемы кодирования

- •Аналоговое кодирование

- •Табличное кодирование

- •Числовое кодирование

- •Системы счисления

- •Кодирование чисел и текстов

- •Кодирование положительных целых чисел

- •Кодирование целых чисел со знаком

- •Кодирование действительных чисел

- •Кодирование текстов

- •Система кодирования windows 1251

- •Кодирование изображений математическая модель изображения

- •Разрешение изображения

- •Психофизиологи ческие модели изображения

- •Форматы записи изображений

- •Кодирование и запись видео

- •Кодирование и запись звука

- •Лекция 9.2 Файлы и каталоги.

- •Лекция 10 Сжатие данных

- •Лекция 11 "Компьютерные вирусы"

- •Словарь основных понятий и терминов

- •Литературные источники Учебные издания для средних школ

- •Справочные издания

- •Научно-популярные издания

- •Учебные пособия для студентов вузов

- •Другие издания

- •Информатика. Практика алгоритмизации и программирования Интернет-версия издания: Шауцукова л.З. Информатика 10-11. — м.: Просвещение, 2000 г.

- •Предисловие

- •Настройки

- •Алгоритмы линейной и разветвляющейся структуры

- •Input "Введите высоту цилиндра : ", h

- •Пример 1.4. Найти произведение цифр заданного целого четырехзначного числа. Система тестов

- •Демонстрация

- •Var Number, {заданное число}

- •I, j, k, l, {цифры числа}

- •Input "Введите четырехзначное число : ", Number

- •Система тестов

- •Демонстрация

- •Var a, b, c : Real; {a, b, c - коэффициенты уравнения}

- •X1, x2 : Real; {x1, x2 - корни }

- •Input "Введите количество тестов : ", nTest

- •Результаты работы qBasic-программы (фрагмент):

- •Демонстрация

- •Var a1, b1, c1, {коэффициенты уравнения первой прямой}

- •X, y : Real; {координаты точки пересечения }

- •Результаты работы Pascal-программы:

- •Input "Введите количество тестов : ", nTest

- •Input ". Введите a1, b1, c1 : ", a1, b1, c1

- •Input " Введите a2, b2, c2 : ", a2, b2, c2

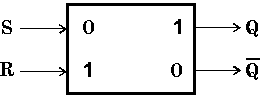

5.7. Что такое триггер?

|

Триггер— это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

Термин триггерпроисходит от английского словаtrigger— защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется терминflip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set— установка, иreset— сброс). Условное обозначение триггера — на рис. 5.6.

Рис.

5.6

Рис.

5.6

Он имеет два симметричных входа S и R и

два симметричных выхода Q и

![]() ,

причем выходной сигнал Q является

логическим отрицанием сигнала

,

причем выходной сигнал Q является

логическим отрицанием сигнала![]() .

.

На каждый из двух входов S и R могут

подаваться входные сигналы в виде

кратковременных импульсов (

![]() ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

Рис.

5.7

Рис.

5.7

|

S |

R |

Q |

|

|

0 |

0 |

запрещено | |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

хранение бита | |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход

станет

равным “1”.

станет

равным “1”.Точно так же при подаче “0” на вход S и “1” на вход R на выходе

появится

“0”, а на Q — “1”.

появится

“0”, а на Q — “1”.Если на входы R и S подана логическая “1”, то состояние Q и

не

меняется.

не

меняется.Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210= 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

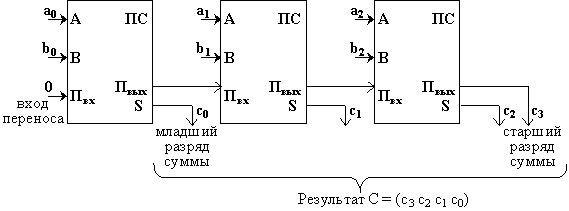

5.8. Что такое сумматор?

|

Сумматор— это электронная логическая схема, выполняющая суммирование двоичных чисел. |

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

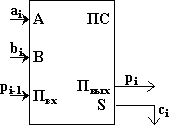

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел,представляет собой комбинацию одноразрядных сумматоров,с рассмотрения которых мы и начнём. Условное обозначение одноразрядного сумматора на рис. 5.8.

Рис.

5.8

Рис.

5.8

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1.цифра aiпервого слагаемого;

2.цифра biвторого слагаемого;

3.перенос pi–1из младшего разряда.

В результате сложения получаются две цифры:

1.цифра ciдля суммы;

2.перенос piиз данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

|

Входы |

Выходы | |||

|

Первое слагаемое |

Второе слагаемое |

Перенос |

Сумма |

Перенос |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3c2c1c0) двух двоичных трехразрядных чисел A = (a2a1a0) и B = (b2b1b0) может иметь вид: