- •2. Системное по

- •9. Уровень автоматического распараллеливания (4-й уровень)

- •8.Временная диаграмма работы шины (циклы чтения)

- •10. Подключение портов ввода/вывода

- •1.Структура 8-ми разрядных цп

- •1.Общая структура цсп процессоров

- •8.Гарвардская архитектура цсп

- •9.Архитектура с5510(общий вид)

- •13.Свертка для с5510

- •19.Ресурсы памяти c5510

- •14.Временная диаграмма работы асинхронного интерфейса

- •24.Работа основного конвейера с5510

- •25.Определение секций данных для языка с

- •28.Дополнительные функции работы с памятью

- •1.Основы управления энергопотреблением

- •4.Регистр управления холостым ходом микропроцессора с55хх

- •5.Способы отключения

- •10. Автоматическая система управления энергопотреблением (apm)

- •11.Система фазовой подстройки частоты (pll)

- •Глобальное разрешение прерываний в с5510

- •Действия при возникновении прерывания

- •1.Структура связи dma с памятью/периферией

- •3.Прямой доступ к памяти

- •4.Прямой доступ к памяти

- •5.Ресурсы, регистры канала контроллера dma

- •6.Ресурсы, регистры канала контроллера dma

- •Описание пропускной способности dma

- •10.6 Шагов программирования dma1

- •17.Конфиг.Структура dma

- •19.Программирование адресов источника и приемника

- •1.Основное место расположения McBsp в системе

- •3.Структурная схема McBsp

- •4.Структурная схема McBsp(продолжение)

- •5.Определения бита и слова

- •6.Определение кадра

- •7.Формат данных передаваемых кодеком aic23

- •16.Многоканальность McBsp

- •22.Сортировка принимаемых каналов

1.Структура 8-ми разрядных цп

Основные характеристики:

Длина слова -8 бит (байт)

Адресуемое пространство памяти –64К байта

Операционные блок с аккумулятором

Равенство длинны слова и разрядность АЛУ, аккумулятора, регистров (данная характеристика условна, т.к. существуют исключения в виде разрядности аккумулятора, АЛУ и т.д., разрядность которых может быть больше 8).

Восьмиразрядные ЦП могут иметь возможность оперировать с 16-ти разрядными числами, если в них реализовано 16-ти разрядное АЛУ.

Архитектура процессора с аккумуляторам

Внутренняя шина данных – осуществляет передачу данных.

Шина данных – внешняя шина.

РОН – регистры общего назначения.

АЛУ – арифметико-логическое устройство, выполняет основные действия.

Для выполнения действий в АЛУ нужно два операнда, но т.к. внутренняя шина данных только одна (по ней можно подать один из операндов), то для подачи второго операнда в АЛУ необходим аккумулятор, находящийся максимально близко к АЛУ. Операнд из РОН сначала попадает в аккумулятор, а уже затем в АЛУ.

К примеру, если выполняется сложение: один операнд передают в аккумулятор, а другой подается на вход АЛУ по внутренней шине данных. Второй операнд может поступать на внутреннюю шину данных либо из РОН, либо по внешней шине данных, если он находился во внешней памяти. Затем операнды синхронно загружаются в АЛУ. Результат выполнения операции может быть сохранен в РОН либо во внешнюю память. Это зависит от выполняемых действий.

Способы выполнения операций:

ADD {src1},{src2},{dst|POHy} //сложение двух операндов

src1 – источник1 в памяти, src2 – источник2 в памяти, dst – приемник в памяти

способ реализации:

LDA{src1} //загрузка первого операнда src1 в аккумулятор

ADDA{src2} //сложение аккумулятора с ячейкой памяти src2, результат находится в аккумуляторе

STA{dst|POHy} //сохранение аккумулятора в ячейку памяти dst или в РОНу

SUB {src},{POHx},{dst|POHy} //операция вычитания

способ реализации:

LDA{src}

SUBA{POHx} // вычитание значения РОНу из значения аккумулятора

STA{dst|POHy}

Способы выполнения операций:

ADD {POH1},{POH2},{dst|POHy}//источники операндов – РОНы

способ реализации:

LDA{POH1}

ADDA{POH2}

STA{dst|POHy}

В данном случае может быть выигрыш времени выполнения операции сложения по сравнению с ADD {src1},{src2},{dst|POHy} из-за более близкого расположения РОНов к АЛУ, нежели ячеек памяти.

SUB {POHx},{src},{dst|POHy}//данная операция достаточно медленна, поэтому используется редко

способ реализации:

LDA{POHx}

SUBA{src}

STA{dst|POHy}

Вывод: Вне зависимости от того, где расположены операнды, для выполнения операции потребуется 3 команды. Но, возможно, в зависимости от того, где находятся операнды, команды выполнятся за меньшее количество тактов.

16-Введение в С5510

1.Общая структура цсп процессоров

Процессор С5510 обеспечивает высокую производительность при сравнительно низком потреблении.

Внутренняя периферия позволяет ускорить процесс обработки.

Различия в ЦСП состоят в видах используемой памяти, периферии, скорости обиена данными, характеристик ЦП и др.

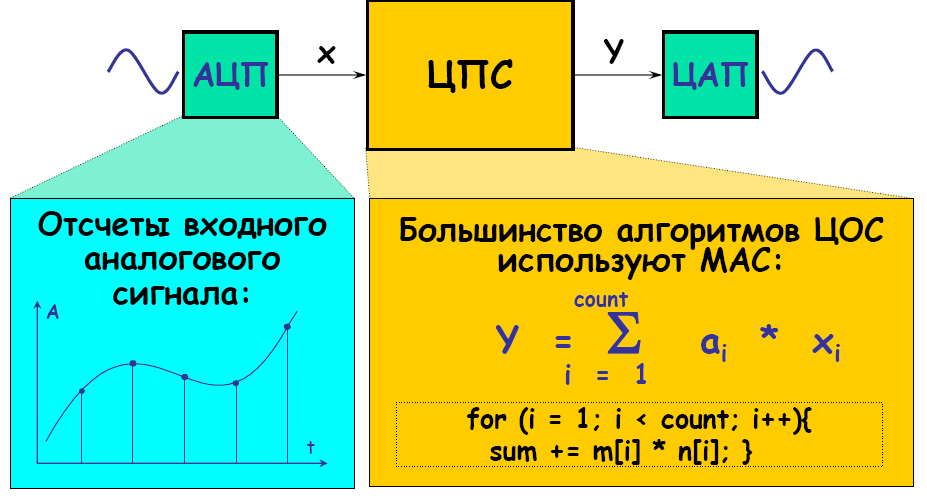

2.Основные задачи, решаемые ЦСП процессорами

ЦПС работает непосредственно с цифровыми данными. Для него основное – иметь возможность выполнять умножение с накоплением с максимальной скоростью.

АЦП характеризуется частотой дискретизации, разрешающей способностью (количество бит для кодирования аналогового сигнала).

Если ограничить a или x, получим фильтр.

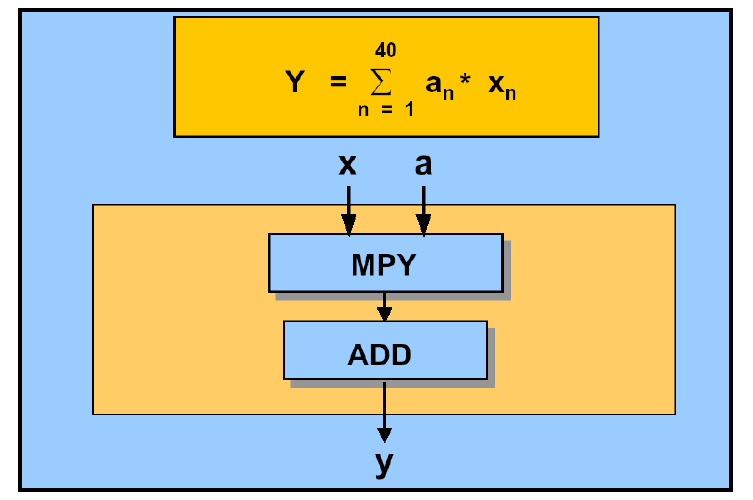

3.ЦОС требует умножителя и сумматора

Ф актически

выполняется свертка во временной

области.

актически

выполняется свертка во временной

области.

MPY – умножение

ADD – сложение

Существует необходимость ввода/вывода данных в/из основного модуля появляется множество внутренних шин.

4.Многошинная архитектура ЦСП

Необходимо иметь дополнительную память (ПЗУ, ОЗУ), которая позволит выполнять одновременно действия со всеми шинами. Таким образом, можно задействовать практически все ресурсы системы, что позволит повысить ее производительность.

5.Внутренняя память для быстрого доступа к данным

DARAM – память с двойным доступом, не требует дополнительных циклов чтения, снижающих производительность.

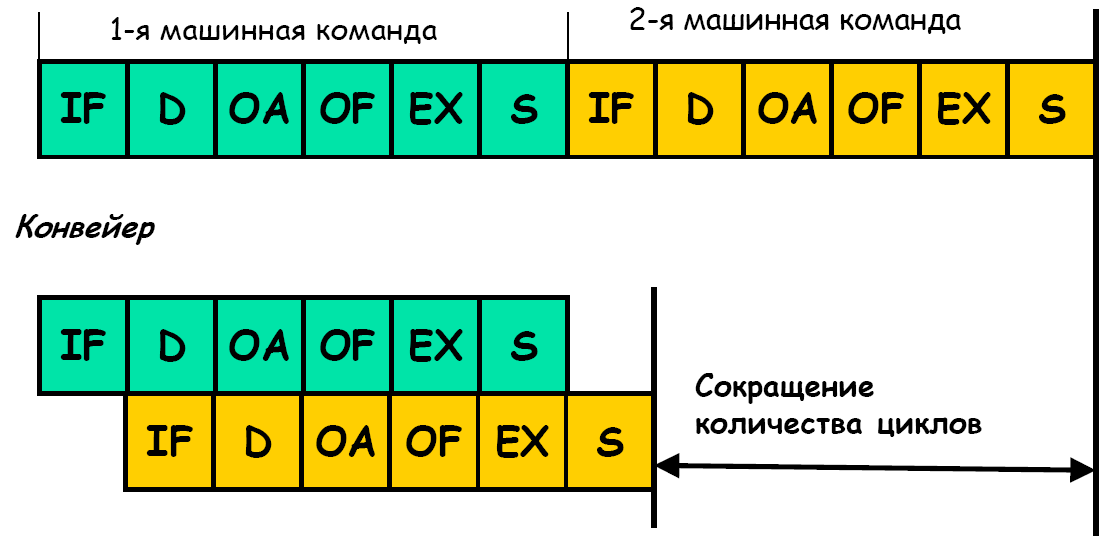

6-7.Применение конвейера для ускорения процесса вычисления

П ри

применении конвейера сокращается время

вычисления (если последовательно

выполнять 2 команды потребуется 12 тактов

для получения результата второй команда,

при применении конвейера результата

получаем на каждом такте – результат

второй команды получим через 7 тактов).

Однако если следующая операция требует

результата предыдущей либо происходит

условный переход, выигрыша нет.

ри

применении конвейера сокращается время

вычисления (если последовательно

выполнять 2 команды потребуется 12 тактов

для получения результата второй команда,

при применении конвейера результата

получаем на каждом такте – результат

второй команды получим через 7 тактов).

Однако если следующая операция требует

результата предыдущей либо происходит

условный переход, выигрыша нет.