- •2. Системное по

- •9. Уровень автоматического распараллеливания (4-й уровень)

- •8.Временная диаграмма работы шины (циклы чтения)

- •10. Подключение портов ввода/вывода

- •1.Структура 8-ми разрядных цп

- •1.Общая структура цсп процессоров

- •8.Гарвардская архитектура цсп

- •9.Архитектура с5510(общий вид)

- •13.Свертка для с5510

- •19.Ресурсы памяти c5510

- •14.Временная диаграмма работы асинхронного интерфейса

- •24.Работа основного конвейера с5510

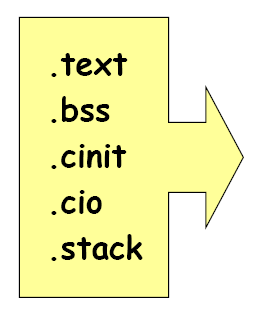

- •25.Определение секций данных для языка с

- •28.Дополнительные функции работы с памятью

- •1.Основы управления энергопотреблением

- •4.Регистр управления холостым ходом микропроцессора с55хх

- •5.Способы отключения

- •10. Автоматическая система управления энергопотреблением (apm)

- •11.Система фазовой подстройки частоты (pll)

- •Глобальное разрешение прерываний в с5510

- •Действия при возникновении прерывания

- •1.Структура связи dma с памятью/периферией

- •3.Прямой доступ к памяти

- •4.Прямой доступ к памяти

- •5.Ресурсы, регистры канала контроллера dma

- •6.Ресурсы, регистры канала контроллера dma

- •Описание пропускной способности dma

- •10.6 Шагов программирования dma1

- •17.Конфиг.Структура dma

- •19.Программирование адресов источника и приемника

- •1.Основное место расположения McBsp в системе

- •3.Структурная схема McBsp

- •4.Структурная схема McBsp(продолжение)

- •5.Определения бита и слова

- •6.Определение кадра

- •7.Формат данных передаваемых кодеком aic23

- •16.Многоканальность McBsp

- •22.Сортировка принимаемых каналов

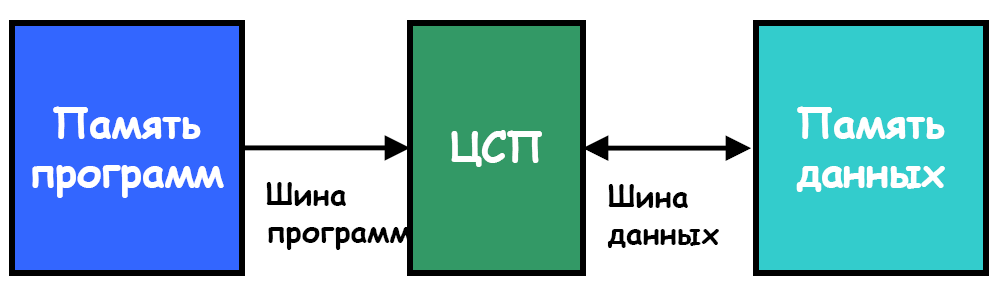

8.Гарвардская архитектура цсп

И спользуя

ШД, мы можем изменять память, а ШП

позволяет только считывать данные

спользуя

ШД, мы можем изменять память, а ШП

позволяет только считывать данные

С5510 – модифицированная гарвардская архитектура. Память данных и память программ едины, но шины для доступа к данным и программам различны. Соответственно, через шину данных нельзя получить доступ к программам.

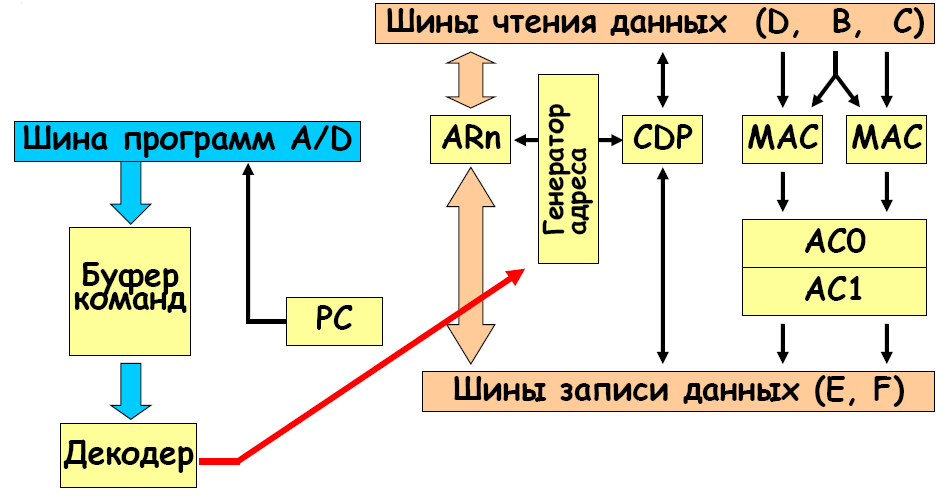

9.Архитектура с5510(общий вид)

A Rn,

CDP

– регистры общего назначения.

Rn,

CDP

– регистры общего назначения.

Шина В имеет доступ только ко внутренней памяти.

Буфер команд позволяет разгрузить процессор и избежать остановки процессор в случае нехватки исполняемых команд.

A – адрес программ

D – данные программ

10-11.Основные характеристики микропроцессора C5510

Память программ адресуется байтами, память данных – словами.

Адресуемое пространство –16Мх8

C5510 –160Kслов ОЗУ (внутренняя память)

23-бит адресные регистры(ARx)

Два АЛУ (16-, 40 бит) – одно основное, второе – для формирования адресов

Dual-MAC (Два MACмодуля)

4х40-бит аккумулятора(ACx)

4 временных регистра (T)

Переменная длинная команды(1-6 байт)

64х8 буфер команд (При циклическом повторении команд, которые находятся в буфере, происходит экономия энергии, т.к. эти команды не требуется перезагружать)

Выполнение параллельных инструкций (сложение, сдвоенное умножение с накоплением, загрузка и пр.)

Аппаратная защита конвейера

Аппаратная поддержка двух вложенных циклов (при поиске мин и макс значений)

12 независимых шин

3 шины чтения данных (BD,CD,DD) (16-ти разрядные)

2 шины записи данных(ED, FD) (16-ти разрядные)

5 шин адреса данных(BA,CA,DA,EA,FA) (24-х разрядные)

1 шина чтения программ(PD) (32-х разрядная)

1 шина адреса чтения программ(PA) (24-х разрядная)

13.Свертка для с5510

Инкремент CDP выполняется только один раз, несмотря на сдвоенную операцию умножения с накоплением (:: -- обозначают сдвоенную операцию).

15.P-Mодуль и I-Модуль

I-Модуль – блок буфера инструкций. В течение каждого цикла ЦП принимает 4 байта программного кода в буфер инструкций и затем декодирует один из шести байтов, полученных ранее. Все константы, которые были закодированы в команде, извлекаются в данном блоке, а затем пересылаются другим блокам.

Когда ЦП готов, декодер считывает из буфера 6 байт, определяет нужно ли выполнять инструкции параллельно.

ЦП осуществляет единовременно 32-х разрядную выборку из памяти программ.

Р-Модуль – блок операций с адресами команд. Котролирует последовательность инструкций при аппаратном зацикливании, условном переходе и т.п.

16.A-Модуль

А-Модуль – блок операций с адресами данных, генерирует адреса пространства данных.

Вся память делится на страницы по 16Кслов (128 страниц).

АЛУ осуществляет операции сдвига, насыщения, логические и арифметические операции.

17.D-Модуль

D-Модуль – содержит основные вычислительные блоки.

При использовании двух шин записи выполняется запись 32 бит за один цикл.

19.Ресурсы памяти c5510

Все шины, имеющие доступ к внешней памяти мультиплексированы, кроме шины D.

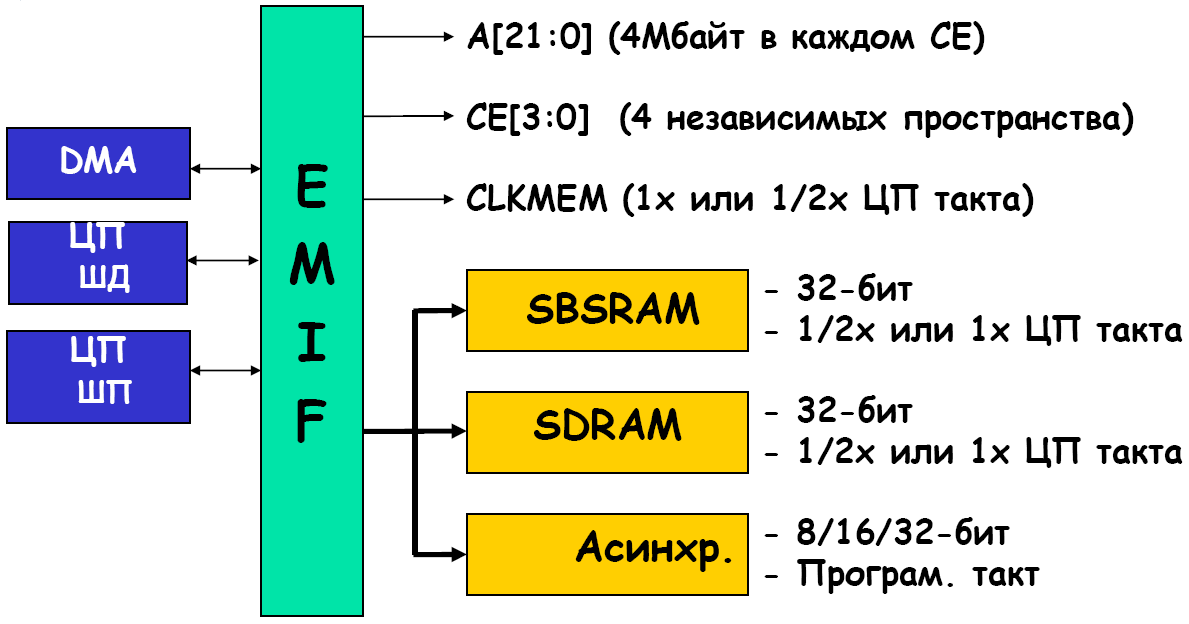

2 0.Расширенный

интерфейс к памяти (EMIF)

0.Расширенный

интерфейс к памяти (EMIF)

SBSRAM – синхронная буферизированная память

SDRAM - синхронная динамическая память

DMA – обмен данными в обход ЦП

CLKMEM – тактирование

Большинство устройств подключаются как асинхронная память, т.к. такой вид памяти обеспечивает большую гибкость.

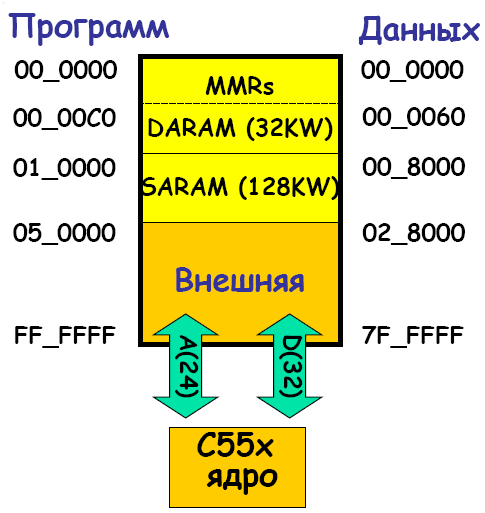

21.Карта памяти микропроцессора С5510

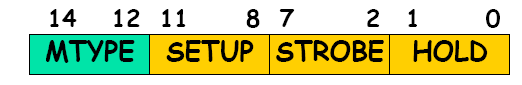

MTYPE – тип подключаемой памяти.

Синхронная память требует настроек, потому она имеет возможность подстройки к любой схеме.

22.Периферия микропроцессора С5510

McBSP – многоканальный буферизированный передатчик.

GPIO - выводы общего назначения

Power – расширенная система энергосбережения

DMA – взаимодействует со всеми устройствами и памятью для передачи информации

Timers – могут использоваться для тактирования

Cashe – отвечает за хранение промежуточных данных

23.Работа микропроцессора в режиме реального времени

Используется схема двойной буферизации (применяется в системах реального времени), время обработки кратно времени заполнения буфера.

18-Основы управления памятью

1.Унифицированная память микропроцессора С5510

MMRs – область памяти регистров, отображаемых на память.

DARAM – ОЗУ с двойным доступом.

SARAM – ОЗУ с одинарным доступом.

Эти три области составляют внутреннюю память микропроцессора С5510.

2.Распределение ПО между секциями памяти

Секция глобальных переменных (.bss) определяет область в памяти для глобальных переменных.

Printf() – нештатная функция, выполняемая МП и возвращающая результат в среду. Секция .cio отвечает за нештатные функции, соответственно, если в программе не будет нештатных функций, то и области памяти этой секции также не будет.

3.Имена секции компилятора

Для секций, чья память не инициализируется (.bss или .far, .stack, .sysmem, .cio), в адресном пространстве выделяется область, но значения в ней не инициализируются. Значения в памяти будут случайны.

4 .Размещение

секций в памяти процессора

.Размещение

секций в памяти процессора

Данные области необходимо правильно разместить в памяти. Чтобы программа работала правильно и автономно, эти области часто размещают во FLASH, а затем загружают во внутреннюю память. Иногда, если нужно разместить большой массив данных, эти области помещают во внешнюю память.

7.Генерируемые CDB файлы средствами конфигурирования

CDB – файл компоновки.

В разделе MEMORY указывается автоматическое расположение памяти. В параметре org указывается начало той или иной памяти, а в параметре len – ее длина.

SECTIONS содержит описание размещения в памяти различных секций программы. Указанные в примере секции будут размещены: .bss в DARAM, .text в SARAM.

8.Командный файл компоновщика

Компоновщик получает исполняемый файл. Для этого ему необходимы указанные файлы. Данные лучше размещать в DARAM, если её не хватает, то оставлять в FLASH.

9.Размещение программ и данных во внешней и внутренней памяти

В пользовательском файле .cmd

для массив coeff_sect

помещается в специально выделенное

адресное пространство SARAM_A.

пользовательском файле .cmd

для массив coeff_sect

помещается в специально выделенное

адресное пространство SARAM_A.

Данные лучше размещать в DARAM, т.к. к ним может требоваться неоднократное параллельное обращение, если же данных слишком много и памяти не хватает, то их можно оставить во FLASH. Память с одиночным доступом используют для размещения программ, а с двойным доступом – для размещения неизменных констант.

10.Расширенный интерфейс к памяти (EMIF)

Интерфейс EMIF обеспечивает связь между внутренней памятью (блоками) и внешней памятью.

К каждому из четырех независимых пространств через EMIF могут подключаться: SBSRAM – синхронная буферизируемая память, SDRAM – синхронное динамическое ОЗУ и Асинхронная память. SBSRAM и SDRAM поддерживаются автоматически.

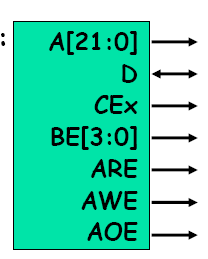

12.Асинхронная память

SRAM – статическое ОЗУ, не требующее обновления.

C Ex

– сигнал, определяющий, к какому

подпространству будет происходить

обращение.

Ex

– сигнал, определяющий, к какому

подпространству будет происходить

обращение.

BE[3:0] – определяет чтение слова, двух слов или байта из памяти.

D – 8-ми, 16-ти, 32-ух разрядная шина данных.

10 нс достаточно для качественной записи данных.

13.Асинхронная память

SETUP – время установки.

STROBE – основной строб.

HOLD – режим захвата (дополнительные такты для выполнения правильного чтения или записи).

Даже если в STROBE и SETUP поместить «0», автоматически добавиться «1».

Максимальная задержка в регистрах SCR1 и SCR2 составляет 255 тактов. После задержки в 255 тактов дальнейшая задержка воспринимается как зависание и процессор сбрасывается. Чтобы получить задержку более 255 тактов можно расширить поля SETUP, STROBE, HOLD за счет сигнала готовности.

Максимальная задержка говорит о том, что чтение будет идти наиболее медленно данные будут гарантированно прочитаны.

В С5510 тактовая частота составляет 200МГц. Соответственно один такт длиться 5нс. Значит, подключать память быстрее 10нс нет необходимости.