- •2. Системное по

- •9. Уровень автоматического распараллеливания (4-й уровень)

- •8.Временная диаграмма работы шины (циклы чтения)

- •10. Подключение портов ввода/вывода

- •1.Структура 8-ми разрядных цп

- •1.Общая структура цсп процессоров

- •8.Гарвардская архитектура цсп

- •9.Архитектура с5510(общий вид)

- •13.Свертка для с5510

- •19.Ресурсы памяти c5510

- •14.Временная диаграмма работы асинхронного интерфейса

- •24.Работа основного конвейера с5510

- •25.Определение секций данных для языка с

- •28.Дополнительные функции работы с памятью

- •1.Основы управления энергопотреблением

- •4.Регистр управления холостым ходом микропроцессора с55хх

- •5.Способы отключения

- •10. Автоматическая система управления энергопотреблением (apm)

- •11.Система фазовой подстройки частоты (pll)

- •Глобальное разрешение прерываний в с5510

- •Действия при возникновении прерывания

- •1.Структура связи dma с памятью/периферией

- •3.Прямой доступ к памяти

- •4.Прямой доступ к памяти

- •5.Ресурсы, регистры канала контроллера dma

- •6.Ресурсы, регистры канала контроллера dma

- •Описание пропускной способности dma

- •10.6 Шагов программирования dma1

- •17.Конфиг.Структура dma

- •19.Программирование адресов источника и приемника

- •1.Основное место расположения McBsp в системе

- •3.Структурная схема McBsp

- •4.Структурная схема McBsp(продолжение)

- •5.Определения бита и слова

- •6.Определение кадра

- •7.Формат данных передаваемых кодеком aic23

- •16.Многоканальность McBsp

- •22.Сортировка принимаемых каналов

Глобальное разрешение прерываний в с5510

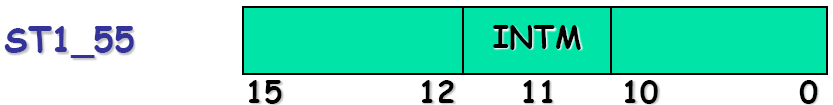

ST1_55 – регистр статуса/

INTM – все прерывания разрешены (все сигналы прерываний будут доходить до ядра процессора, и он их будет обрабатывать).

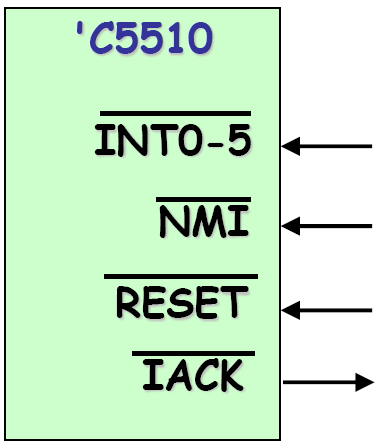

В нешние

прерывания С5510

нешние

прерывания С5510

6 маскируемых внешних прерываний(INT0-5) – должны быть в «1»

2 два не маскируемых внешних прерывания(NMI, RESET)

Сигнал подтверждения прерывания низкий уровень (IACK)

Если внешние прерывания не используются, то нужно гарантированно исключить приход сигналов (помехи) на эти выводы.

EHPI – Enhanced Host Port Interface – расширенный хост-порт интерфейс.

Регистр флагов прерывания(IFR) – регистрирует события (прерывания), т.е. после того как прерывание произошло, оно выставляет флаг в IFR, который уже потом пропускается или не пропускается через IER.

Флаг прерывания в регистре IFR будет равен «1» до тех пор, пока прерывание не будет обработано.

Прерывание можно упустить, так как по IFR не видно сколько раз происходило прерывание.

Чтобы работать с прерыванием необходимо выполнение следующих условий:

INT(прерывание) генерируется.

Локальное разрешение есть.

Глобальное разрешение есть.

Регистры флагов прерываний IFR0 и IFR1 аналогичны регистрам IER0 и IER1.

Данный регистр нельзя изменить программно.

Действия при возникновении прерывания

|

Прерывания PC -> Стек (16 либо 32 бита в зависимости от конфигурации стека) |

Копирование PC в стек |

|

Регистры -> Стек |

Сохранение регистров в стек |

|

1 -> INTM |

Глобальное запрещение прерываний |

|

ISR адрес -> PC |

Загрузка в PC адреса ISR |

|

0 -> IACK вывод

|

Перевод IACK сигнала в «0» (подтверждение прерывания) |

|

0 -> IFR0/1 (n)

|

Очищение соответствующего флага прерываний |

!!!Изначально все прерывания запрещены.

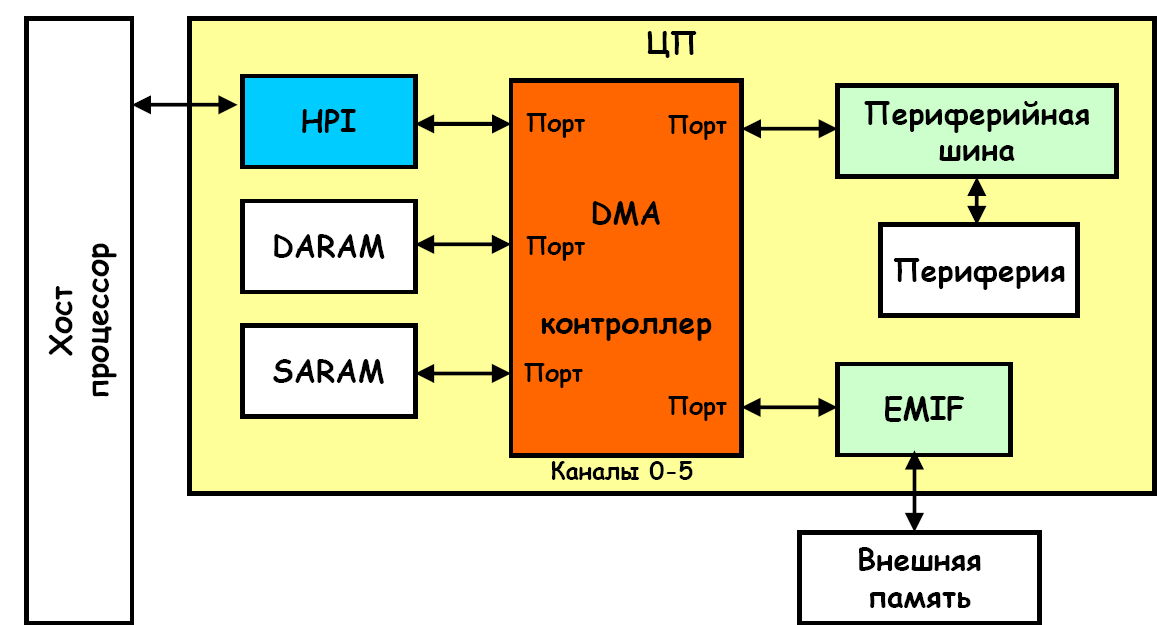

21-Контроллер прямого доступа к памяти

1.Структура связи dma с памятью/периферией

Чтобы сократить загруженность ЦП применяется DMA. В нем существуют 6 каналов, которые обеспечивают пересылку данных между 3 основными модулями, а также свободу доступа к периферии.

Имеется доступ к SARAM, DARAM, EMIF (обеспечивает связь с внешней памятью), Периферии.

ЦП имеет больший приоритет, чем каналы DMA. Если попытаться передавать одновременно данные с DMA и без него, то может возникнуть конфликт между ЦП и контроллером DMA.

У каждого канала имеется внутренний FIFO буфер, который позволяет уменьшить количество конфликтов.

3.Прямой доступ к памяти

•Элемент: 1, 2, или 4 байта (канал DMA имеет возможность упаковки: байт, слово, двойное слово)

•Кадр: группа из 1 до 64K элементов

•Блок: группа из 1 до 64K кадров

•Макс. возможность: 2 16-бит передач (R/W) за цикл

Счетчики, которые инкрементируют адрес, 16-тиразрядные. Следовательно, 216 = 64К. Это и есть максимальный размер кадра. Максимальное количество информации, которое можно передать = 4*64К*64К.

В DMA имеется возможность манипулирования количеством принимаемых и предаваемых кадров. Для передачи и приема необходимо знать адреса передатчика и приемника. В приемнике может осуществляться сортировка данных.

Можно предавать два 16-ти битных числа (чтение/запись) за один цикл работы.