shpora

.docx|

1. В системе управления, в общем случае, объединены две подсистемы: Управляющая; Управляемая.

Микропроцессором принято называть полупроводниковый кристалл (комплект кристаллов), который выполняет автоматизированную обработку информации. В минимальном варианте микропроцессор состоит из o Регистров; o АЛУ (вычислителя); o Схемы управления (дешифраторы, буферы, мультиплексоры и т.д.). При этом характеризуется прежде всего: Архитектурой (гарвардская или принстонская). Разрядностью (как правило, от 8 до 64 разрядов); Тактовой частотой; Набором команд (универсальный: CISC –, сокращённый: RISC); Поддерживаемыми режимами адресации; Типами (форматами) обрабатываемых данных. Для выполнения именно управляющих функций (связь с объектом) в состав МПСУ на уровне периферийных (внешних) устройств, как правило, входят преобразователи (АЦП, ЦАП). Поскольку процесс управления можно представить, как последовательность этапов движения и преобразования данных, информацию часто называют универсальным атрибутом управления. Информация существует в виде сигналов. Сигнал может быть определён, как технически различимый параметр некоторого физического процесса. По природе сигналы делятся на два типа аналоговые (или непрерывные) и цифровые (или дискретные). Для аналоговых сигналов (АС) характерно следующее: большой объем информации (теоретически – бесконечный); ограниченная точность сигнала (погрешность) вследствие внешних (наводки) и внутренних (дрейфы, помехи) факторов; ограниченность диапазона изменения параметра (частотные свойства, мощностной диапазон); неидеальность передаточных функций (преобразователей). Представление информации в форме цифровых сигналов прежде всего, решает проблемы размерности информации. Кроме этого, цифровой сигнал обладает большей помехоустойчивостью, идеален для обработки, а погрешность преобразования определяется сложностью и, соответственно стоимостью системы. Процедура аналого-цифрового преобразования, в общем случае, состоит из следующих этапов: дискретизация. На этом этапе входной сигнал преобразуется из функции непрерывного времени в набор значений в фиксированные моменты времени. fmax – максимальная частота в спектре исходного аналогового сигнала. квантование по уровню. При этом диапазон значений исходного сигнала (шкала) делится на (как правило) равные части – кванты с шагом h. Преобразование сигнала сводится, по сути, к сведению значений сигнала в дискретные моменты времени к разрешённым.

Более двух разрешённых уровней имеется только у преобразователей. Остальные цифровые устройства и системы работают в системе двух разрешённых уровней. Наиболее удобным способом формализации при этом является кодирование в канонической двоичной системе

Кроме

разрешённых уровней сигналов

классифицирующими параметрами для

логик являются

следующие характеристики: Uпитания;

Нагрузочная способность (Rmin нагр);

Быстродействие (f max); Потребляемая

мощность; Степень интеграции Кроме

разрешённых уровней сигналов

классифицирующими параметрами для

логик являются

следующие характеристики: Uпитания;

Нагрузочная способность (Rmin нагр);

Быстродействие (f max); Потребляемая

мощность; Степень интеграции

|

2. Основой полупроводниковой техники на сегодняшний день остается кремний, природный полупроводник. Полупроводники- это класс веществ, по своему удельному сопротивлению (от 10-8 до 106 Ом*см) занимающих промежуточное место между проводниками и диэлектриками (изоляторами). Различие электрических свойств у металлов, полупроводников и диэлектриков обеспечивается разной величиной энергии, которая необходима для освобождения валентных электронов от связей с атомами, расположенными в узлах кристаллической решётки. Электрическая проводимость полупроводников обусловлена наличием одновременно свободных носителей заряда разных знаков вследствие теплового заброса части электронов (концентрация которых очень велика, 1023 см-3) из валентной зоны в зону проводимости вследствие сравнительной небольшой ширины т.н. энергетической щели между этими зонами (0,1 – 3 эв). При этом концентрации электронов и дырок в объёме полупроводника оказываются равными ni = pi (ni = pi = 0 при Т = 0К). Дыркой, как известно, называют вакантное, не занятое электроном место в ковалентной связи (т.н. квазичастица), с помощью которой описывают коллективное движение электронов. Существовать дырки могут только внутри объёма полупроводника, в то время как электрон может быть инжектирован из полупроводника наружу. Для изготовления интегральных схем используют химически чистый кремний (один атом примеси приходится не менее чем на 1013 атомов вещества). Технологией легирования получают примесный полупроводник или n – типа (примесь - донор) или p – типа (примесь - акцептор). В частности, если в 1 кг расплавленного кремния (Si) добавить 20 мкг фосфора (P), концентрация свободных электронов в нём вырастет в 105 раз. По способу управления проводимостью примесных полупроводников и различают биполярную (электрическим током) и полевую (электрическим полем) логики. Биполярная логика основана на свойствах pn – перехода. Неуправляемый pn – переход представляет собой устройство из двух разнопроводящих объёмов полупроводника, в приграничных областях которых за счёт диффузионного потока электронов образуются обеднённые слои, имеющие большое удельное сопротивление и нескомпенсированный объёмный заряд. Напряжённость поля объёмного заряда (Еграницы) препятствует дальнейшему взаимному проникновению электронов и дырок из приграничных зон, обеспечивая т.н. дрейфовый поток:

Основные параметры логических элементов (на примере инвертора) 1. Токи (инвертор работает на элемент ДТЛ) I«1» max << I «0» max

2.Напряжения Для повышения помехоустойчивости выдерживаются следующие соотношения (для ТТЛ-уровней): 2В <= Uвх «1» min < Uвых «1» min Uвых «0» max < Uвх «0» max <= 0,8 В Говорят, что «выходные» напряжения должны быть «лучше» входных, т.е. интервал выходных напряжений является охватывающим для интервала входных напряжений.

|

|

3. Быстродействие Предельно абстрактно работу цифрового элемента можно рассматривать, как прохождение через него П-образного прямоугольного импульса напряжения. В реальности и входные и выходные кривые напряжений имеют профиль, заметно отличающийся от прямоугольного. Некоторым компромиссным решением являются т.н. диаграммы в измерительных уровнях, на которых кривые напряжений апроксимируются трапециями.

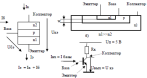

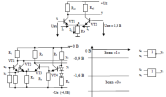

Таким образом, частотные свойства цифрового элемента определяют, в-основном, по времени задержки. РТЛ - инвертор Инвертор резисторно-транзисторной логики содержит один npn – транзистор по схеме с общим эмиттером. РТЛ элемент 2ИЛИ-НЕ Базисный

элемент 2ИЛИ-НЕ (стрелка Пирса)

резисторно-транзисторной логики

содержит два npn

–

транзистора.

РТЛ элемент 2И-НЕ Базисный элемент 2И-НЕ (штрих Шеффера) резисторно-транзисторной логики также содержит два npn – транзистора. ДТЛ элемент 2И-НЕ В ДТЛ – элементе 2И-НЕ при подаче на оба входа высоких уровней напряжения делителем R1-Rсм формируется Uб > 0,6 В, обеспечивая открытое и насыщенное состояние транзистора. При подаче низкого уровня сигнала на один или оба входа напряжением смещения формируется Uб < 0,6В, что надёжно удерживает транзистор в режиме отсечки. Переключающим в ДТЛ – логике является сигнал низкого уровня, который характеризуется меньшим «дребезгом контактов» (удобно представить переключение ключевого транзистора из состояния хх входного сигнала).

Упрощенная ДТЛ 2И-НЕ.Модифицированный элемент ДТЛ два изменения: дополнительный последовательный диод в цепи базы и сопротивление в 1 К, шунтирующее база – эмиттерный переход. Для ориентации приведены номиналы резисторов. Особенность транзистора Дарлингтона в том, что напряжение между базой и эмиттером (в открытом состоянии) в два раза больше обычного, а напряжение насыщения равно, по крайней мере, падению напряжения на диоде (так как потенциал эмиттера транзистора VТ1 должен превышать потенциал эмиттера транзистора VТ2, на величину падения напряжения на диоде). |

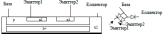

3. ТТЛ элемент 2И-НЕ Если в конструкции биполярного транзистора предусмотреть не один, а несколько эмиттеров (обычно 5-8), появляется возможность использовать его в качестве входного каскада. Этим существенно упрощается и удешевляется схема логических элементов, использующих такого рода многоэмиттерный транзистор (МЭТ).

Для исключения паразитных горизонтальных цепочек эмиттер1-база-эмиттер2 расстояния между соседними эмиттерами выполняют больше, чем диффузионная длина носителей заряда в базовом слое.

Быстродействие логического элемента в значительной степени определяется продолжительностью t01 – переключения транзистора из открытого режима в режим отсечки. В действительности транзистор начинает закрываться в тот момент, когда по внешней цепи осуществится рассасывание избыточного заряда в области базы. А время задержки в закрывании напрямую связано с концентрацией электронов в области базы, т.е. со степенью насыщения база – эмиттерного (в – первую очередь) и база– коллекторного (во – вторую) переходов. Улучшить частотные свойства элемента позволяет включение т.н. добавочного транзистора.

Особенностью схемы является подбор сопротивлений R3 >> R4. При увеличении напряжения на коллекторе VT1(на всех входах высокий уровень) первым открывается транзистор VT2 (в его базу втекает весь ток и поэтому задержки в открытии из-за дополнительной цепи R3, б-э VT3 не происходит). Затем открывается дополнительный транзистор и цепью R4(относительно малого номинала), к-э VT3 шунтирует б-э переход ключевого транзистора, тем самым ограничивая его насыщение. Дальнейшим развитием ТТЛ - элемента является схема со сложным инвертором или двуполярный ключ.Структурно схема состоит из трёх блоков: входной МЭТ (VT1), фазорасщепительный блок (VT2), двухтактный выходной каскад (VT3, VT4). При подаче 0В хотя бы на один из входов, VT1 открывается и на его базе формируется напряжение Uб VT1 ~ 0,8 В. Этого напряжения не хватает, чтобы открыть три последовательно включённых p-n перехода: б-к VT1, б-э VT2, б-э VT4 (для этого нужно не менее 0,6 х 3 = 1,8 В). Следовательно, транзистор VT2 закрыт, на базе транзистора VT4 потенциал земли (0 В) и он также закрыт. При этом на коллекторе VT2 (и базе VT3) напряжение, близкое источнику питания Uп = 5В, поэтому транзистор VT3 и диод VD открыты, обеспечивая выходной ток и выходное напряжение Uвых1 > Uвых1 min. При подаче на все входы Uвх1 увеличивается напряжение на базе VT1 и при его значении в районе 1,2 В открывается б-к переход VT1 и б-э переход VT2. Ток на резисторе R2 увеличивается, снижая напряжение на базе VT3. При этом увеличивающийся ток на резисторе R3 поднимает напряжение на базе VT4 и он открывается. Открывшийся транзистор VT4 шунтирует R3 и ещё больше увеличивает ток через R2. Транзистор VT3 начинает закрываться. В промежуток времени, когда открыты оба транзистора (VT4 и VT3) ток короткого замыкания ограничивается R4 и сопротивлениями VT3, VD, VT4. Затем VT2 и VT4 достигают стадии насыщения. В этом режиме разности напряжений коллектора VT2 (менее 1,2 В ) и коллектора VT4 (около 0,3 В) ΔU< 0,9 В не хватает, чтобы открыть б-э переход VT3 и VD. По этой причине VT3 надёжно заперт и на выходе Uвых0 ~ 0,3 В. Таким образом, формирование прямого (VT3) и обратного(VT4) фронтов выходного сигнала выполняется путём открытия разных транзисторов и задержки в формировании фронтов связаны. |

|

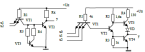

4. ТТЛШ – элемент Диод Шоттки — полупроводниковый диод с малым падением напряжения при прямом включении. Способом увеличения рабочей частоты элемента является ограничение процесса открытия транзистора только первой стадией: открытием перехода база – эмиттер. Для этого между базой и коллектором транзистора выходного (формирующего) каскада элемента ТТЛ подключают особого вида вентиль - диод Шоттки (иначе его называют выпрямляющим контактом). По той причине, что диод Шоттки при нарастании положительной разности потенциала база-коллектор отрывается первым, он своим током ограничивает превышение потенциала базы над потенциалом коллектора уровнем 0,2-0,3 В. Очевидно, что такого напряжения недостаточно для отпирания база-коллекторного pn – перехода. Схема, полученная таким образом, получила аббревиатуру ТТЛШ.

Конструкция, основные параметры, вольт-амперная характеристика и условное обозначение диода Шоттки

Схема шунтирования база – коллекторного перехода ключевого транзистора Упрощенная схема базового элемента ТТЛШ Отмечают, что энергопотребление схем ТТЛШ не менее, чем в 5 раз ниже, чем ТТЛ, что позволяет только за счёт этого значительно повысить степень интеграции ИИЛ элемент Наличие в схеме резисторов определяет достаточно серьёзные проблемы при изготовлении интегральных схем, т.к. напыление металла или сплава технологически сложно и достаточно дорого. Решением проблемы может стать замена резисторов нормально открытыми транзисторами. Процесс подобной модернизации схемы рассмотрим на примере РТЛ – инвертора. Резисторы Rк и Rб можно рассматривать, как источники, соответственно базового и коллекторного тока. Вместо них в данном случае в схему включают pnp – транзисторы.

Для входных линий в элементах ИИЛ обычно используются диоды Шоттки, а транзисторы, выполняющие роль источников тока, объединяют в один: Конструктивно многоколлекторный транзистор подобен многоэмиттерному, включенному по инверсной схеме. Однако при его изготовлении принимаются специальные меры для увеличения коэффициента усиления в расчёте на каждый коллектор до требуемого уровня (сокращение расстояния между коллекторами, приближение скрытого слоя повышенной концентрации в области эмиттера к слою базы).

Инвертор и базисный элемент эмиттерно-связной логики Иной вариант удерживания транзистора, формирующего выходной сигнал, на границе насыщенного состояния реализован, в так называемой, эмиттерно-связной логике (ЭСЛ). В основе её лежит дифференциальная схема включения npn – транзисторов (токовый ключ). Транзисторы VT1 и VT2 выполняют с максимально близкими параметрами. Опорное напряжение (Uоп) ключа подбирается такого номинала, при котором за вычетом падения напряжения на Rэ (Uа), оставшееся (Uбэ2) соответствовало бы начальной стадии открытия база-коллекторного перехода (0,6 В). Пока напряжение Uвх = Uбэ1+ Uа < Uоп = Uбэ2+ Uа; Uбэ1 < Uбэ2 . |

Но напряжение Uбэ2 определено как раз на границе начальной стадии открывания транзистора, следовательно, транзистор VT1 остаётся в отсечке, а VT2 – открытым. Напряжение на выходе формируется по цепи +Uп , Rк1 и соответствует высокому уровню. Режим, когда Uвх = Uоп , для идеально подобранных транзисторов соответствует открытому состоянию их обоих в начальной стадии насыщения. Как самостоятельный, в цифровых схемах данный режим не используется. Для переключения схемы в нулевое состояние необходимо обеспечить Uвх > Uоп . По мере роста входного напряжения будет увеличиваться ток I1 , суммарный ток IΣ = I1 + I2 и напряжение точки «а» Uа = IΣ* Rэ . При этом начнёт уменьшаться напряжение Uбэ2 = Uоп - Uа и станет меньше порогового уровня, необходимого для открытого состояния транзистора VT2, после чего транзистор закроется. Можно также указать, что сопротивление общего резистора - около 1кОм, резисторов в коллекторных цепях - несколько сотен Ом. По соотношению u1 и u0 это также положительная(позитивная) логика, т.к. u1 > u0.

|

|

5. Полевые транзисторы относятся к группе униполярных, т.к. электрическая проводимость обеспечивается носителями заряда одного знака, а управление осуществляется электрическим полем. Из многочисленных вариантов этих транзисторов в цифровой технике наибольшее распространение получили транзисторы с изолированным затвором обогащённого типа. При отсутствии напряжения на управляющем электроде эти транзисторы находятся в закрытом состоянии (нормально закрытые). Полевые транзисторы этого типа в соответствии с их конструкцией получили аббревиатуру МОП: металл-оксид-полупроводник МОП – транзистор обогащенного типа:

Наиболее распространённой является схема включения полевого транзистора с общим истоком.

Уровни сигналов МОП (и КМОП) элементов приняты следующими: U0<=0,5 U1>=0,8Uп затвора относительно подложки), при котором индуцируется канал составляет от 0,3 до 3В (среднее 1,65В). Для p – канального транзистора затвор должен быть отрицательнее подложки, а для n- канального – положительнее. Для формирования единичного уровня сигнала на выходе в схемах МОП – ключа (рисунок 29, а) необходимо дополнительное сопротивление R. Его значение можно оценить из следующих предположений. Пусть при Uпит = 5В необходимо обеспечить уровень U1 = 0,8 Uпит = 4В, считая сопротивление открытого канала равным 10 кОм (в различных вариантах от 1 до 15 кОм). Выходное напряжение в открытом состоянии транзистора формируется резистивным делителем: При переключении в закрытое состояние это сопротивление входит в цепь, по которой стекает отрицательный заряд затвора, ограничивает значение разрядного тока и увеличивает продолжительность формирования нулевого сигнала на выходе элемента. По этой причине максимальная частота МОП – элемента ограничивается значением в несколько сотен кГц.

Состояния

КМОП-И

|

В схемах базисных элементов одна пара транзисторов включена параллельно, а другая - ярусно. Комплементарное включение полевых транзисторов используется также в схеме буферного элемента с высокоимпедансным состоянием. Данный элемент используется для объединения на некоторой общей шине произвольного количества отдельных устройств. Буферный элемент с высокоимпедансным состоянием:

|

|

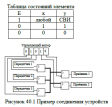

6. Объединение логических элементов в схему для преобразования цифровой информации называется логической схемой. По специфике функционирования логические схемы делятся на: Комбинационные схемы; Цифровые автоматы; В комбинационных схемах (КС) сигнал на каждом из выходов однозначно зависит от состояния соответствующих входов (yi = f (x0, x1, … xn-1), где f – булевая функция. К наиболее используемым КС относятся сумматор, дешифратор, мультиплексор, компаратор, мажоритарный элемент. Закон функционирования комбинационной схемы задают или семейством передаточных функций в аналитическом виде или таблицей состояний. Иногда комбинационные схемы называют автоматами без памяти или примитивными автоматами.

В структуре цифровых автоматов (ЦА) имеется блок запоминающих элементов (ЗЭ). По этой причине цифровые автоматы обладают конечным набором внутренних состояний (в данном случае, 2к). Внутренние состояния ЗЭ могут изменяться под действием входных сигналов. Выходной сигнал цифрового автомата формируется на основе входных сигналов и внутреннего состояния ЦА. Зачастую в качестве входных и выходных каскадов ЦА применяются соответствующие комбинационные схемы. Элементарными ЦА являются триггеры. Многочисленные устройства памяти также относятся к цифровым автоматам. Закон функционирования ЦА может быть также задан аналитически, но чаще для этого используются операционные таблицы (похожи на таблицы состояний КС) или временные диаграммы. Комбинационные схемы Знакомство с комбинационными схемами будет иллюстрироваться созданием их с помощью технологии цифрового синтеза на базе карт Карно. Как известно, картой Карно называется двумерная таблица логических функций, в каждой клетке которой находится произведение входных переменных или их инверсий. Сами переменные идентифицируют строки и столбцы этой таблицы. Используется карта Карно при числе переменных до 6. Алгебраически карта Карно соответствует записи логической (передаточной) функции в совершенной дизъюнктивной нормальной форме (СДНФ) : F = Σfi mi для i = 0,1 …, q-1, где fi - значение (требуемое) передаточной функции, mi - минтерм или конъюнкция переменных q = 2k - количество минтермов, k – количество входных переменных Иначе говоря, минтермы представляет собой все возможные комбинации входных сигналов, а с помощью fi выделяются те сочетания, которые должны формировать единичный результат. Полученную передаточную функцию, как правило, оптимизируют с целью сокращения операций. При этом могут быть использованы, как аналитические выражения для основных логических функций |

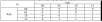

Полный одноразрядный последовательный сумматор Сумматором называют разновидность комбинационных схем, имеющих как самостоятельное значение, так и являющихся обязательной частью более сложных схем, например контроллеров, процессоров. Назначение сумматоров – выполнять арифметическое сложение двоичных данных. Как известно, остальные арифметические команды (вычитание, умножение и деление) можно выполнить через суммирование. Правда, в этом случае необходимы такие вспомогательные действия, как инверсия и сдвиг. Выполним синтез сумматора для использования в простейшей схеме последовательного суммирования:

Карта Карно одноразразрядного сумматора для выхода s

Передаточная функция до преобразования:

Передаточная функция после преобразования:

При этом выражение в первой скобке соответствует логической функции «исключающее ИЛИ», а во второй - «исключающее ИЛИ-НЕ». Таким образом, относительно входа с и результата операции «исключающее ИЛИ» для входов a и b передаточная функция представляет собой ещё одну операцию «исключающее ИЛИ».

Достоинством схемы последовательного суммирования является простота и наглядность, недостатком - достаточно существенная задержка в формировании результата, равная n tзад , где tзад - время задержки выходных сигналов одноразрядного сумматора. Иначе данную схему называют сложением с переносом вдоль разрядной сетки. Сумматор с параллельным переносом Для увеличения быстродействия могут быть использована схема суммирования с параллельным переносом, в которой переносы определяются одновременно для всех разрядов с помощью специальных формирователей. При этом сами сумматоры выполняются упрощенно, так как формируют только сумму. Формирователем

переноса для нулевых разрядов слагаемых

(с0), фактически, служит элемент «И»

(рисунок). Каждый последующий

формирователь имеет на два входа

больше и, соответственно, более сложную

схему. Самый старший формирователь

(сn-2) для n- разрядных слагаемых имеет

2*(n-1) входов. Время задержки определяется

по его задержке + по задержке упрощенного

сумматора.

Как

следует из схемы, в качестве разрядных

сумматоров могут быть использованы

одноразрядные сумматоры, из которых

исключены цепи, формирующие сигнал

переноса Формирователь переноса с0 для сумматора в первом разряде имеет два входа и представляет собой обычный элемент «И». Однако для каждого последующего разряда число входных линий увеличивается на 2 и, соответственно, усложняется схема. В частности, схема формирователя с1 может быть получена обычным образом:

Сумматор с условным переносом Обычно в качестве 4-х разрядных сумматоров используются схемы последовательного переноса. В таком случае цепь переносов укорачивается вдвое. |

схемой

с простым

инвертором и

обладает существенными недостатками:

низкая помехоустойчивость; малая

нагрузочная способность; ограниченное

быстродействие при работе на емкостную

нагрузку.

схемой

с простым

инвертором и

обладает существенными недостатками:

низкая помехоустойчивость; малая

нагрузочная способность; ограниченное

быстродействие при работе на емкостную

нагрузку.

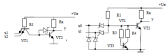

Базисные

элементы pМОП – логики в несколько

упрощенном варианте представлены на

рисунке 37. Роль дополнительного

сопротивления выполняют в данном

случае постоянно открытые транзисторы

VT3.

Для

повышения быстродействия схемы

используют пару разноканальных

(взаимно дополняющих, т.е. комплементарных)

МОП – транзисторов. Подобная схема

включения положена в основу КМОП –

логики.

Базисные

элементы pМОП – логики в несколько

упрощенном варианте представлены на

рисунке 37. Роль дополнительного

сопротивления выполняют в данном

случае постоянно открытые транзисторы

VT3.

Для

повышения быстродействия схемы

используют пару разноканальных

(взаимно дополняющих, т.е. комплементарных)

МОП – транзисторов. Подобная схема

включения положена в основу КМОП –

логики.

В

схеме КМОП – инвертора единичный

уровень сигнала формируется

сопротивлением канала VT1 (и сопротивлением

нагрузки, конечно), а нулевой уровень

обеспечивается открытым транзистором

VT2. В момент переключения один из

транзисторов обеспечивает путь с

меньшим сопротивлением для стекания

заряда с затвора другого. Переключение

происходит быстрее и поэтому рабочая

частота КМОП - элементов находится в

мегагерцовом диапазоне.

В

схеме КМОП – инвертора единичный

уровень сигнала формируется

сопротивлением канала VT1 (и сопротивлением

нагрузки, конечно), а нулевой уровень

обеспечивается открытым транзистором

VT2. В момент переключения один из

транзисторов обеспечивает путь с

меньшим сопротивлением для стекания

заряда с затвора другого. Переключение

происходит быстрее и поэтому рабочая

частота КМОП - элементов находится в

мегагерцовом диапазоне. Базисные

элементы КМОП – Л

Базисные

элементы КМОП – Л

После

небольших преобразований передаточной

функции, записанной по карте Карно,

реализующая её схема выглядит следующим

образом.

После

небольших преобразований передаточной

функции, записанной по карте Карно,

реализующая её схема выглядит следующим

образом.