- •Схемотехника эвм

- •Часть 1

- •Содержание

- •Предисловие

- •Введение

- •1. Основные определения и характеристики схем цифровых устройств

- •1.1. Основные определения в области микросхемотехники

- •1.2. Основные обозначения на схемах

- •1.3. Основные положения модели поведения полупроводниковых приборов

- •1.3.1. Полупроводниковый p-n-переход.

- •1.3.2. Полупроводниковый диод

- •1.3.3. Биполярный транзистор

- •1.3.4. Полевой транзистор

- •2. Основные понятия алгебры логики

- •Введение в алгебру логики

- •Булевый базис

- •2.3. Произвольные функции и логические схемы

- •Законы булевой алгебры

- •2.5. Положительная и отрицательная логика

- •3. Цифровые интегральные микросхемы

- •3.1. Параметры микросхем

- •3.2. Особенности логических элементов различных логик

- •3.2.1. Диодно-транзисторная логика

- •3.2.2. Высокопороговая логика

- •3.2.3. Транзисторно-транзисторная логика

- •Универсальные (стандартные) серии ттл

- •Микромощные микросхемы ттл

- •Микросхемы ттл повышенного быстродействия

- •Микросхемы ттл с транзисторами Шотки

- •Способ увеличения числа входов и, или

- •Исключающее или

- •Соединение входов и выходов микросхем ттл

- •Неиспользуемые логические элементы ттл

- •Неиспользуемые входы ттл

- •Совместное применение разных серий ттл

- •3.2.4. Типы выходных каскадов Микросхемы с открытым коллектором

- •3.2.5. Микросхемы с тремя логическими состояниями

- •4. Логические элементы на кмоп-транзисторах

- •4.1. Логические элементы на моп-транзисторах

- •4.2. Цифровые микросхемы кмоп

- •4.3. Микросхемы с буферными выходами

- •Основные логические элементы кмоп

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •5.1. Схемы с непосредственными связями

- •5.2. Схемотехника ис инжекционной логики и2л

- •5.3. Эмиттерно-связанная логика

- •6. Триггеры

- •6.1. Общие сведения о триггерных устройствах

- •6.2. Асинхронный rs-триггер

- •6.3. Триггерные системы

- •6.3.1. Синхронный rs-триггер

- •6.4. Тактируемый d-триггер

- •6.5. Счетный т-триггер

- •6.6. Двухступенчатые триггеры

- •7. Счетчики

- •7.1. Общие положения

- •7.2. Классификация счетчиков

- •7.2.1. Асинхронные суммирующие счетчики с последовательным переносом

- •7.2.2. Асинхронные вычитающие счетчики с последовательным переносом

- •7.2.3. Асинхронные реверсивные счетчики с последовательным переносом

- •7.3. Параллельное соединение счетчиков

- •7.4. Последовательное соединение счетчиков

- •7.5.Синхронные двоичные счетчики со сквозным переносом.

- •7.6.Синхронные двоичные счетчики с параллельным переносом.

- •Библиографический список

Исключающее или

Интересна микросхема 155ЛП5, содержащая в одном корпусе 4 элемента исключающее ИЛИ. Действие каждого из элементов описывается выражением

Т![]() аблица

истинности элемента исключающее ИЛИ,

его структура и условное графическое

обозначение представлены на рис.

3.24.

аблица

истинности элемента исключающее ИЛИ,

его структура и условное графическое

обозначение представлены на рис.

3.24.

а б в

Рис. 3.24. Исключающее ИЛИ: а – структурная схема;

б – условное графическое обозначение; в – таблица истинности

Из таблицы истинности и уравнения следует, что 0 на выходе будет, когда сигналы на входах одинаковы. Операция исключающее ИЛИ соответствует арифметическому сложению двух двоичных чисел, если не учитывать единицу старшего разряда, возникающую в сумме 1 + 1 = 10. Отсюда второе название операции – сложение по модулю два.

Е![]() сли

на одном из входов элемента исключающее

ИЛИ, напримерx1,

поддерживать логическую 1, то

сли

на одном из входов элемента исключающее

ИЛИ, напримерx1,

поддерживать логическую 1, то

В этом случае элемент выполняет функцию инвертора. Если x1 = 0, то элемент выполняет функцию повторителя.

Элементы исключающее ИЛИ используются в арифметических устройствах (для выявления неравенства двух двоичных разрядов), для формирования и генерации импульсных сигналов, в качестве удвоителей частоты, для определения фазового сдвига двух импульсных последовательностей.

На рис. 3.25 приведено условное графическое обозначение микросхемы 155ЛП5, пример ее применения для формирования коротких импульсов из переднего и заднего фронтов входного сигнала и временная диаграмма. Схема формирователя содержит две цепи передачи входного сигнала: непосредственно на вход элемента DD4 и через три последовательно включенных элемента исключающее ИЛИ (DD1 – DD3), на один из входов которых подан нулевой потенциал. В этом режиме исключающее ИЛИ выполняет функцию повторителя.

Формирователь работает следующим образом. В установившемся режиме при Uвх = 0 на обоих входах элемента DD4 действует нулевой потенциал. В это время выходной сигнал DD4 равен нулю, так как входные сигналы равны. При появлении входного импульса на одном из входов DD4 логическая единица устанавливается сразу после появления переднего фронта, на другом – через 3tзд.р (длительности фронтов здесь не учитываются). В течение этого интервала времени сигналы на входах элемента DD4 различны (на одном входе 1, на другом 0) и на выходе будет высокий уровень. Через 3tзд.р сигналы на обоих входах становятся одинаковыми, равными 1. На выходе DD4 снова установится 0. Короткий импульс высокого уровня будет вырабатываться и в процессе изменения входного сигнала с 1 на 0 ( по заднему фронту входного импульса).

а б в

Рис. 3.25. Микросхема сумматора по модулю 2: а – условное обозначение;

б – пример применения; в – временная диаграмма

Соединение входов и выходов микросхем ттл

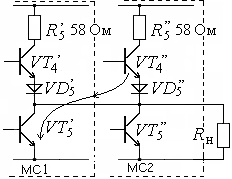

К одному выходу микросхемы можно подключать от 10 до 30 входов микросхем ТТЛ той же серии. Для увеличения выходной мощности микросхемы, казалось бы, можно соединить выходы двух – трех микросхем (рис. 3.26). Если микросхемы работают синхронно, то такое соединение допустимо. Однако, в общем случае, когда микросхемы выполняют различные функции или имеют различные входные сигналы, такое соединение недопустимо. Это связано с тем, что если в одной микросхеме открыт нижний транзистор выходного каскада, а в другой – верхний, в цепи потечет ток, ограниченный только резистором R5 (~50 Oм).

Это около 100 мА. Такой ток опасен для транзистора. По этой причине соединять выходы между собой нельзя. В качестве исключения допускается параллельное соединение входов и выходов двух логических элементов одного корпуса при соответствующей логике работы. Сведения о способах увеличения отдаваемой в нагрузку мощности будут рассмотрены далее.

Рис. 3.26. Схема соединения выходов двух микросхем на общую нагрузку