- •Схемотехника эвм

- •Часть 1

- •Содержание

- •Предисловие

- •Введение

- •1. Основные определения и характеристики схем цифровых устройств

- •1.1. Основные определения в области микросхемотехники

- •1.2. Основные обозначения на схемах

- •1.3. Основные положения модели поведения полупроводниковых приборов

- •1.3.1. Полупроводниковый p-n-переход.

- •1.3.2. Полупроводниковый диод

- •1.3.3. Биполярный транзистор

- •1.3.4. Полевой транзистор

- •2. Основные понятия алгебры логики

- •Введение в алгебру логики

- •Булевый базис

- •2.3. Произвольные функции и логические схемы

- •Законы булевой алгебры

- •2.5. Положительная и отрицательная логика

- •3. Цифровые интегральные микросхемы

- •3.1. Параметры микросхем

- •3.2. Особенности логических элементов различных логик

- •3.2.1. Диодно-транзисторная логика

- •3.2.2. Высокопороговая логика

- •3.2.3. Транзисторно-транзисторная логика

- •Универсальные (стандартные) серии ттл

- •Микромощные микросхемы ттл

- •Микросхемы ттл повышенного быстродействия

- •Микросхемы ттл с транзисторами Шотки

- •Способ увеличения числа входов и, или

- •Исключающее или

- •Соединение входов и выходов микросхем ттл

- •Неиспользуемые логические элементы ттл

- •Неиспользуемые входы ттл

- •Совместное применение разных серий ттл

- •3.2.4. Типы выходных каскадов Микросхемы с открытым коллектором

- •3.2.5. Микросхемы с тремя логическими состояниями

- •4. Логические элементы на кмоп-транзисторах

- •4.1. Логические элементы на моп-транзисторах

- •4.2. Цифровые микросхемы кмоп

- •4.3. Микросхемы с буферными выходами

- •Основные логические элементы кмоп

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •5.1. Схемы с непосредственными связями

- •5.2. Схемотехника ис инжекционной логики и2л

- •5.3. Эмиттерно-связанная логика

- •6. Триггеры

- •6.1. Общие сведения о триггерных устройствах

- •6.2. Асинхронный rs-триггер

- •6.3. Триггерные системы

- •6.3.1. Синхронный rs-триггер

- •6.4. Тактируемый d-триггер

- •6.5. Счетный т-триггер

- •6.6. Двухступенчатые триггеры

- •7. Счетчики

- •7.1. Общие положения

- •7.2. Классификация счетчиков

- •7.2.1. Асинхронные суммирующие счетчики с последовательным переносом

- •7.2.2. Асинхронные вычитающие счетчики с последовательным переносом

- •7.2.3. Асинхронные реверсивные счетчики с последовательным переносом

- •7.3. Параллельное соединение счетчиков

- •7.4. Последовательное соединение счетчиков

- •7.5.Синхронные двоичные счетчики со сквозным переносом.

- •7.6.Синхронные двоичные счетчики с параллельным переносом.

- •Библиографический список

4.3. Микросхемы с буферными выходами

Путем подключения к выходу инвертора дополнительных – одного или двух – инверторов можно улучшить переключательные характеристики устройств КМОП (рис. 4.6). Повышение крутизны переходного участка характеристики здесь обеспечивается за счет дополнительного усиления сигналов. Каждый инвертор имеет свой коэффициент усиления.

Общий коэффициент усиления устройства определяется произведением коэффициентов усиления каскадов.

Рис. 4.6. Принципиальная схема инвертора КМОП с буферными каскадами

Большое усиление позволяет формировать импульсы с большой крутизной фронтов независимо от формы входных импульсов. В микросхемах с буферными выходами транзисторы, выполняющие логические функции, – маломощные, а выходные транзисторы обладают повышенной мощностью. В настоящее время выпускаются микросхемы как с простыми, так и с буферными выходными каскадами.

Основные логические элементы кмоп

На рис. 4.7–4.9 приведены схемы логических элементов КМОП И-НЕ, ИЛИ-НЕ и инвертора с тремя состояниями. Проследить работу соответствующих элементов при наличии тех или иных входных сигналов легко, если учесть, что p-канальный транзистор открывается низким потенциалом (нулем – L), а n-канальный – высоким (единицей – Н). Таблицы истинности (электрических состояний) приведены на соответствующих рисунках.

На рис. 4.7 представлена схема логического элемента И-НЕ КМОП.

В этой схеме входные n-канальные транзисторы VT3 и VT4 включены последовательно, а нагрузочные VT1 и VT2 – параллельно. Если на затворы входных транзисторов одновременно поступают сигналы высокого уровня, то транзисторы VT3 и VT4 открываются, на выходе устанавливается потенциал низкого уровня, нагрузочные транзисторы VT1 и VT2 закрыты, ток в цепи не протекает.

а б в

Рис. 4.7. Логический элемент И–НЕ КМОП: а – принципиальная схема;

б – таблица истинности; в – условное обозначение

Если хотя бы на одном из входов уровень напряжения низкий, то транзисторы VT3 и VT4 закрыты и открывается один из нагрузочных транзисторов VT1 или VT2. На выходе устанавливается высокий уровень и в нагрузку может протекать ток. Следует уточнить, что в этом случае закрываются не оба транзистора VT3 и VT4, а только один, на затворе которого низкий уровень. Второй транзистор остается открытым. Однако, транзисторы включены последовательно и ток по цепи VT3, VT4 не проходит. Именно это и имеется ввиду, когда говорится, что оба транзистора VT3 и VT4 закрыты.

На рис. 4.8 представлена схема логического элемента ИЛИ–НЕ, в которой входные транзисторы VT1 и VT4 включены параллельно, а нагрузочные VT2 и VT3 – последовательно. Если хотя бы на одном из входов имеется высокий уровень напряжения, то данный транзистор открывается, на выходе устанавливается уровень нуля, нагрузочные транзисторы закрыты, ток в цепи не протекает. Если на обоих входах имеется уровень нуля, то транзисторы VT1 и VT4 закрыты, а VT2 и VT3 – открыты, на выходе устанавливается высокий уровень и в нагрузку может протекать ток.

а б в

Рис. 4.8. Логический элемент ИЛИ–НЕ КМОП: а – принципиальная схема;

б – таблица истинности; в – условное обозначение

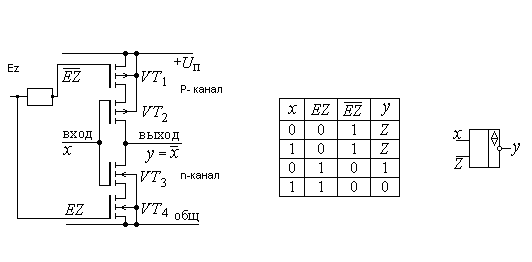

На рис. 4.9 представлена схема инвертора с тремя состояниями.

а б в

Рис. 4.9. Инвертор КМОП с тремя состояниями: а – принципиальная схема;

б – таблица истинности; в – условное обозначение

Собственно

инвертор составляют транзисторы VT2

и VT3,

а транзисторы VT1

и VT4

служат для управления третьим состоянием.

Если ЕZ

= 1 (![]() = 0) , то схема в состоянии 2С. ЕслиЕZ

= 0, то схема в состоянии 3С, выход отключен

и от + Uп,

и от нуля.

= 0) , то схема в состоянии 2С. ЕслиЕZ

= 0, то схема в состоянии 3С, выход отключен

и от + Uп,

и от нуля.