- •Схемотехника эвм

- •Часть 1

- •Содержание

- •Предисловие

- •Введение

- •1. Основные определения и характеристики схем цифровых устройств

- •1.1. Основные определения в области микросхемотехники

- •1.2. Основные обозначения на схемах

- •1.3. Основные положения модели поведения полупроводниковых приборов

- •1.3.1. Полупроводниковый p-n-переход.

- •1.3.2. Полупроводниковый диод

- •1.3.3. Биполярный транзистор

- •1.3.4. Полевой транзистор

- •2. Основные понятия алгебры логики

- •Введение в алгебру логики

- •Булевый базис

- •2.3. Произвольные функции и логические схемы

- •Законы булевой алгебры

- •2.5. Положительная и отрицательная логика

- •3. Цифровые интегральные микросхемы

- •3.1. Параметры микросхем

- •3.2. Особенности логических элементов различных логик

- •3.2.1. Диодно-транзисторная логика

- •3.2.2. Высокопороговая логика

- •3.2.3. Транзисторно-транзисторная логика

- •Универсальные (стандартные) серии ттл

- •Микромощные микросхемы ттл

- •Микросхемы ттл повышенного быстродействия

- •Микросхемы ттл с транзисторами Шотки

- •Способ увеличения числа входов и, или

- •Исключающее или

- •Соединение входов и выходов микросхем ттл

- •Неиспользуемые логические элементы ттл

- •Неиспользуемые входы ттл

- •Совместное применение разных серий ттл

- •3.2.4. Типы выходных каскадов Микросхемы с открытым коллектором

- •3.2.5. Микросхемы с тремя логическими состояниями

- •4. Логические элементы на кмоп-транзисторах

- •4.1. Логические элементы на моп-транзисторах

- •4.2. Цифровые микросхемы кмоп

- •4.3. Микросхемы с буферными выходами

- •Основные логические элементы кмоп

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •5.1. Схемы с непосредственными связями

- •5.2. Схемотехника ис инжекционной логики и2л

- •5.3. Эмиттерно-связанная логика

- •6. Триггеры

- •6.1. Общие сведения о триггерных устройствах

- •6.2. Асинхронный rs-триггер

- •6.3. Триггерные системы

- •6.3.1. Синхронный rs-триггер

- •6.4. Тактируемый d-триггер

- •6.5. Счетный т-триггер

- •6.6. Двухступенчатые триггеры

- •7. Счетчики

- •7.1. Общие положения

- •7.2. Классификация счетчиков

- •7.2.1. Асинхронные суммирующие счетчики с последовательным переносом

- •7.2.2. Асинхронные вычитающие счетчики с последовательным переносом

- •7.2.3. Асинхронные реверсивные счетчики с последовательным переносом

- •7.3. Параллельное соединение счетчиков

- •7.4. Последовательное соединение счетчиков

- •7.5.Синхронные двоичные счетчики со сквозным переносом.

- •7.6.Синхронные двоичные счетчики с параллельным переносом.

- •Библиографический список

6.3. Триггерные системы

В современной микроэлектронике триггеры используются, как правило, в виде системы, состоящей из собственно триггера, играющего роль ячейки памяти (ЯП), и устройства управления (УУ). УУ представляет собой устройство, преобразующее входную информацию в комбинацию сигналов, под воздействием которых собственно триггер принимает одно из двух устойчивых состояний. Собственно триггер (ЯП) и устройство управления (УУ) – единый функциональный узел.

Рис. 6.4. Триггерная система

Главная роль в формировании свойств триггерной системы принадлежит управляющим устройствам, которые в схемном отношении отличаются большим разнообразием. Структура управляющего устройства, число и назначение входов, обратные связи с выхода ЯП на входы – все это и определяет функциональные свойства триггерной системы. Примером такой системы является синхронный RS-триггер.

6.3.1. Синхронный rs-триггер

Синхронный (тактируемый) RS-триггер (рис. 6.5) получается из асинхронного путем подключения к его входам схемы управления (УУ).

а б

Рис. 6.5 Синхронный (тактируемый) RS-триггер: а – принципиальная схема;

б – условное графическое обозначение

На рис. 6.5 инверсные входы Sа и Rа – асинхронные входы, а S и R – информационные входы. Вход С – тактовый (синхронизирующий), q1 и q2 – внутренние сигналы, управляющие собственно триггером, который, как его асинхронный аналог на элементах И-НЕ, переключается сигналами нулевого уровня. Состояния синхронного RS-триггера представлены в табл. 6.5.

Таблица 6.5

|

Такт n |

Такт n+1 | ||

|

С |

Rn |

Sn |

Qn+1 |

|

0 |

0 |

0 |

Qn |

|

0 |

1 |

0 |

Qn |

|

0 |

0 |

1 |

Qn |

|

0 |

1 |

1 |

Qn |

|

1 |

0 |

0 |

Qn |

|

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

* |

Видно, что при С = 0 действие сигналов по входам R и S заблокировано, а при С = 1 состояния аналогичны состояниям асинхронного RS-триггера на элементах ИЛИ-НЕ.

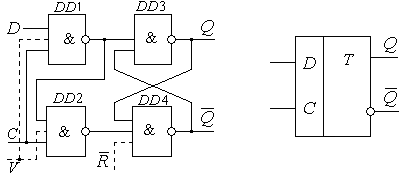

6.4. Тактируемый d-триггер

Тактируемый D-триггер имеет информационный вход D и вход синхронизации. Одна из возможных схем тактируемого D-триггера и его условное обозначение приведены на рис. 6.6.

а б

Рис. 6.6. Тактируемый D-триггер: а –принципиальная схема;

б – условное графическое обозначение

D-триггер отличается от синхронного RS-триггера тем, что у него один информационный вход. Возможные состояния выходов тактируемого D-триггера представлены в табл. 6.6. Если С = 0, то состояние триггера устойчиво и не зависит от информационного сигнала на входе D. Если С = 1, то состояние триггера определяется уровнями на входе D. С-сигнал в этом случае играет роль команды записать в триггер.

Этот тип триггера исключительно широко используется в цифровых устройствах. Другие его названия: прозрачная защелка, прозрачный фиксатор, синхронный фиксатор, D-триггер, управляемый уровнем синхросигнала.

Таблица 6.6

|

D |

Qn |

Qn+1 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Часто используемое название «D-триггер» не отображает свойства прозрачности схемы по D-входу и не выделяет ее среди других типов D-триггеров. В специальной литературе укоренился термин защелка, иногда используется термин фиксатор. Эти термины хотя и не подчеркивают свойства прозрачности, но по крайней мере обозначают схемы только данного типа.

Особенности поведения прозрачной защелки иллюстрирует следующая диаграмма (рис. 6.7):

Рис. 6.7. Диаграмма работы D-триггера

Изменения D-входа при С = 0 (моменты t1, t2, t7) никак не влияют на состояние выхода Q: триггер заперт по С-входу и находится в режиме хранения. Фронт С-сигнала (момент t3) вызывает переключение триггера в то состояние, которое было к этому моменту на входе D. При С = 1 защелка прозрачна: любое изменение D-входа (t4 и t5) вызывает изменения выхода Q.

По срезу синхросигнала (момент t6) D-триггер-защелка фиксирует на выходе то состояние, которое было на D-входе непосредственно перед этим моментом. Следующее изменение выходного сигнала Q будет возможно только по фронту следующего синхроимпульса (момент t8).

Если на С-вход подать единичный уровень, то свойство запоминания защелки проявляться никак не будет и она будет выполнять функции обычного буферного усилителя мощности в тракте передачи данных.

Существуют D-триггеры, в которых параллельно С-сигналу на входные элементы DD1 и DD2 (см. рис. 6.6) заведен еще один разрешающий сигнал – V-сигнал. Такие триггеры называются DV-триггерами. Разрешением на прием D-уровня является конъюнкция сигналов на С- и V-входах.

Иногда

в триггер-защелку вводят дополнительный

вход

![]() сброса в нуль. Такой простейший вариант

входa

гашения имеет активный L-уровень,

и пользоваться им можно лишь при С

= 0.

сброса в нуль. Такой простейший вариант

входa

гашения имеет активный L-уровень,

и пользоваться им можно лишь при С

= 0.

Если сигнал сброса подавать при С = 1, то при D = 1 RS-триггер, образованный элементами DD 3 и DD 4 (см. рис. 6.6), окажется под воздействием сразу и S- и R-сигнала, после одновременного снятия которых состояние его станет неопределенным.

Существуют схемы D-триггеров, для которых активным является низкий уровень С-сигнала, т. е. триггер прозрачен при низком уровне на входе С.

Подробнее о временных характеристиках, об определении задержки сигналов можно посмотреть, например, в [4, 10].

Временными параметрами D-триггеров-защелок являются:

время задержки распространения по трактам вход С – выходы и вход D – выходы;

время подготовки по D-входу;

время выдержки по D-входу;

минимальная длительность С-импульса.

Для схем, в которых возможны гонки по входу, дополнительным параметром является максимальная длительность фиксирующего среза С-сигнала.