- •2. Преобразования входной информации

- •Буквенно-цифровой код

- •3.1 Двоично-десятичный код, двоично-десятичные числа.

- •3.2 Двоичная арифметика.

- •3.4Арифметика в дополнительном коде.

- •Основные элементы цифровой микропроцессорной техники.

- •Асинхронные триггеры

- •Rs-триггер с инверсными входами

- •Синхронные триггеры со статическим управлением

- •Триггеры с динамическим управлением

- •Мультиплексоры

- •Демультиплексор

- •Сдвиговый регистр

- •Суммирующие двоичные счетчики

- •Вычитающий и реверсивный счетчики

- •Кольцевой счетчик

- •Делители частоты импульсной последовательности

- •Одноразрядный двоичный сумматор

- •Многоразрядные двоичные сумматоры

- •Программная модель 32-разрядных процессоров

- •Процессоры р6

- •Устройство управления. Принципы построения арифметико-логического устройства. Микропроцессорная память, регистры. Команды, процедуры их выполнения и способы адресации.

- •1. Pentium II

- •4. Pentium III

- •5. Pentium IV

- •2. Термоустойчивый корпус

- •Организация интерфейса в микропроцессоре. Способы обмена информацией в микропроцессорных средствах. Интерфейсы – средства сопряжения модулей в систему.

- •Структура процессора

- •Два подхода к построению процессоров

- •Цифровые автоматы

- •Функционирование микро-эвм. Режимы работы эвм: однопрограммные и многопрограммные; прерывания.

Многоразрядные двоичные сумматоры

В зависимости от способа ввода кодов слагаемых сумматоры делятся на два типа: последовательного и параллельного действия. В сумматоры первого типа коды чисел вводятся в последовательной форме, т.e. разряд за разрядом (младшим разрядом вперед), в сумматоры второго типа каждое слагаемое подается в параллельной форме, т.е. одновременно всеми разрядами.

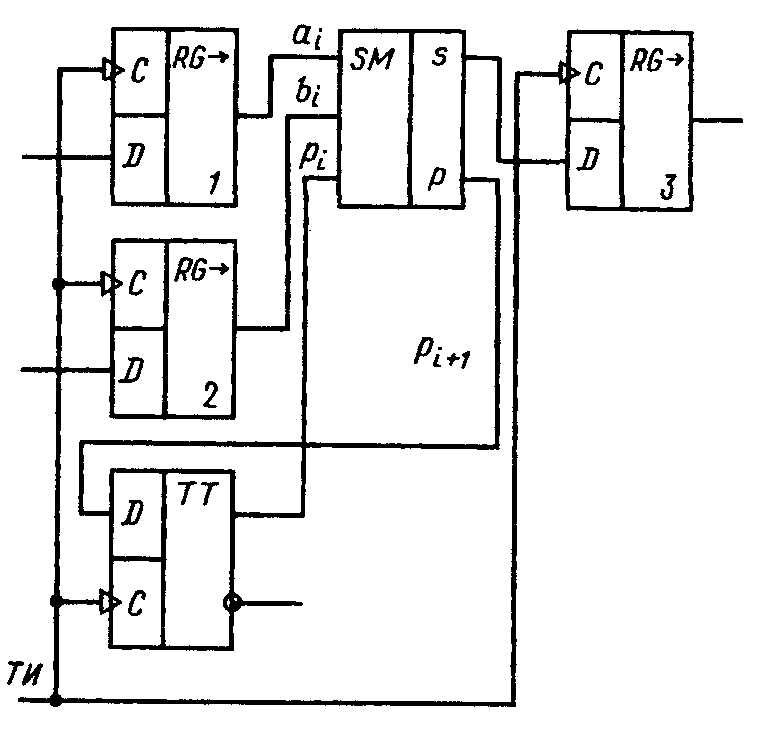

Сумматор последовательного действия (рис. 4.11).

Рис.

4.11

Рис.

4.11

4.9 Классификация и параметры запоминающих устройств

Для хранения небольших массивов кодовых слов могут использоваться регистры. Но уже при необходимости хранить десятки слов применение регистров приводит к неоправданно большим аппаратурным затратам. Для хранения больших массивов слов строят запоминающие устройства (ЗУ) с использованием специальных микросхем, в каждой из которых может храниться информация объемом в тысячи битов.

По выполняемым функциям различают следующие типы запоминающих устройств: оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ), перепрограммируемое постоянное запоминающее устройство (ППЗУ).

Оперативное ЗУ используется в условиях, когда необходимо выбирать и обновлять хранимую информацию в высоком темпе работы процессора цифрового устройства. Вследствие этого в ОЗУ предусматриваются три режима работы:

-режим хранения при отсутствии обращения к ЗУ;

-режим чтения хранимых слов;

-режим записи новых слов.

При этом в режимах чтения и записи ОЗУ должно функционировать с высоким быстродействием (обычно время чтения или записи слова в ОЗУ составляет доли микросекунды). В цифровых устройствах ОЗУ используются для хранения данных (исходных данных, промежуточных и конечных результатов обработки данных) и программ.

Постоянное ЗУ предназначено для хранения некоторой однажды записанной в него информации, не нарушаемой и при отключении источников питания. В ПЗУ предусматриваются два режима работы:

-режим хранения;

-режим чтения с высоким быстродействием.

Режим записи не предусматривается. Используются ПЗУ для хранения программ в таких специализированных цифровых устройствах, которые, функционируя длительное время, многократно выполняют действия по одному и тому же алгоритму при различных исходных данных.

Перепрограммируемое ПЗУ в процессе функционирования цифрового устройства используется как ПЗУ. Оно отличается от ПЗУ тем, что допускает обновление однажды занесенной информации, т.е. в нем предусматривается режим записи. Однако в отличие от ОЗУ запись информации требует отключения ППЗУ от цифрового устройства, производится с использованием специальных предназначенных для записи устройств (программаторов) и занимает длительное время, достигающее десятков минут. Перепрограммируемые ПЗУ дороже ПЗУ, и их применяют в процессе отладки программы, после чего их можно заменить более дешевым ПЗУ.

Запоминающее устройство содержит некоторое число N ячеек, в каждой из которых может храниться слово с определенным числом разрядов n. Ячейки последовательно нумеруются двоичными числами. Номер ячейки называется адресом. Если для представления адресов используются комбинации m-разрядного двоичного кода, то число ячеек в ЗУ может составить N=2m .

Количество информации, которое может храниться в ЗУ, определяет его емкость. Емкость можно выражать числом ячеек N с указанием разрядности n хранимых в них слов в форме Nхn, либо ее можно определять произведением N и n: М = N • n бит. Часто разрядность ячеек выбирают кратной байту (1 байт равен 8 битам). Тогда и емкость удобно представить в байтах. Большие значения емкости часто выражаются в единицах К = 210 = 1024. Например, М = 64 Кбайт означает емкость, равную М = 64 • 1024 • 8 бит.

Быстродействие ЗУ характеризуется двумя параметрами:

-временем выборки (tВ, представляющим собой интервал времени между моментом подачи сигнала выборки и появлением считанных данных на выходе;

- циклом записи (tЦЗ, определяемым минимально допустимым временем между моментом подачи сигнала выборки при записи и моментом, когда допустимо последующее обращение к памяти.

Запоминающие устройства строятся из набора однотипных микросхем ЗУ с определенным их соединением. Каждая микросхема ЗУ кроме времени обращения и емкости характеризуется потребляемой мощностью, набором питающих напряжений, типом корпуса (числом выводов). Микросхемы ППЗУ дополнительно характеризуются временем хранения записанной в них информации (по истечении которого хранящаяся в ячейках информация может самопроизвольно измениться), допустимым количеством циклов перезаписи (после чего микросхема считается негодной для использования).

4.10 Оперативное запоминающее устройство

На рис. 4.12 приведена типичная структура микросхемы ОЗУ. Информация хранится в накопителе. Он представляет собой матрицу, составленную из элементов памяти (ЭП), расположенных вдоль строк и столбцов. Элемент памяти может хранить 1 бит информации (лог. 0 либо лог.1). Кроме того, он снабжен управляющими цепями для установки элемента в любом из трех режимов: режиме хранения, в котором он отключается от входа и выхода микросхемы, режиме чтения, в котором содержащаяся в ЭП информация выдается на выход микросхемы, режиме записи, в котором в ЭП записывается новая поступающая с входа микросхемы информация.

Каждому ЭП приписан номер, называемый адресом элемента. Для поиска требуемого ЭП указывается строка и столбец, соответствующие положению ЭП в накопителе. Адрес ЭП в виде двоичного числа принимается по шине адреса в регистр адреса. Число разрядов адреса связано с емкостью накопителя. Число строк и число столбцов накопителя выбираются равными целой степени двух. И если число строк Nстр = 2n1 и число столбцов Nст = 2n2, то общее число ЭП (емкость накопителя):

![]()

где n=n1+n2 - число разрядов адреса, принимаемого в регистр адреса. Например, при емкости N = 210 = 1024 число разрядов адреса n=10; при этом выбирается n1= n2 = n/2= 5, в этом случае число строк и число столбцов накопителя 2n1 = 2n2 = 32.

Рис. 4.12 Типичная структура микросхемы ОЗУ

Разряды

регистра адреса делятся на две группы:

одна группа из n1

разрядов определяет двоичный номер

строки, в которой в накопителе расположен

ЭП, другая группа из n2

разрядов - двоичный номер столбца, в

котором расположен выбираемый ЭП. Каждая

группа разрядов адреса подается на

соответствующий дешифратор: дешифратор

строк и дешифратор столбцов. При этом

каждый из дешифраторов создает на одной

из своих выходных цепей уровень лог.1

(на остальных выходах дешифратора

устанавливается уровень лог.0),

выбранный ЭП оказывается под воздействием

уровня лог. 1 одновременно по цепям

строки и столбца. При чтении содержимое

ЭП выдается на усилитель чтения и с него

- на выходной триггер (Т) и выход микросхемы.

Режим записи устанавливается подачей

сигнала на вход разрешения записи ( ).

При уровне лог.0 на входе

).

При уровне лог.0 на входе открывается усилитель записи и бит

информации с входа данных поступает

в выбранный ЭП и запоминается в нем.

открывается усилитель записи и бит

информации с входа данных поступает

в выбранный ЭП и запоминается в нем.

Указанные

процессы происходят в том случае, если

на входе выбора кристалла ( )

действует активный уровень лог.0. При

уровне лог.1 на этом входе на всех выходах

дешифратора устанавливается уровень

лог.0 и ЗУ оказывается в режиме хранения.

)

действует активный уровень лог.0. При

уровне лог.1 на этом входе на всех выходах

дешифратора устанавливается уровень

лог.0 и ЗУ оказывается в режиме хранения.

Микросхемы ОЗУ допускают наращивание емкости памяти наращиванием разрядности (и, следовательно, разрядности хранимых слов) и наращиванием числа ячеек (и, значит, числа слов, которые можно хранить в памяти). Таким образом, используя соответствующее число микросхем в определенном их соединении, можно строить память с требуемой организацией.

4.11 Постоянные запоминающие устройства

Как и ОЗУ, ПЗУ состоит из ячеек, обратившись к которым можно вывести их содержимое. Отличие от ОЗУ заключается в том, что информация в ячейки записывается однократно, после чего в процессе эксплуатации используется лишь режим чтения.

По способу занесения информации ПЗУ делятся на два вида:

-ПЗУ, программируемые маской на предприятии-изготовителе;

-ПЗУ, программируемые пользователем.

В первые информация заносится в процессе изготовления микросхем с помощью соответствующего фотошаблона. Очевидно, такой способ записи пригоден в тех случаях, когда производится выпуск крупной партии ПЗУ с одной и той же записанной в них информацией. Промышленность выпускает такие ПЗУ, например, для использования в качестве преобразователя двоичного кода в определенные двоично-десятичные коды и других преобразователей. В них входная кодовая комбинация служит адресом ячейки, а содержимое ячейки - выходной кодовой комбинацией (являющейся, например, кодовой комбинацией двоично-десятичного кода).

В ПЗУ, программируемых пользователем, запись информации производится непосредственно пользователем с помощью специальных устройств, называемых программаторами. Программатор выдает в микросхему соответствующие напряжения для записи информации, набираемой на клавиатуре либо предварительно нанесенной путем пробивок на перфоленту. Этими напряжениями осуществляется прожигание плавких перемычек в элементах памяти. Очевидно, однажды записанная в ПЗУ информация в дальнейшем не может быть изменена. При необходимости изменить содержимое ПЗУ микросхемы с ранее записанной информацией заменяются новыми, в которые записываются новые данные.

На рис. 4.13 приведена структура ПЗУ, программируемого пользователем. Как и в ОЗУ, матрица-накопитель состоит из элементов памяти, образующих строки и столбцы, но в отличие от ОЗУ при считывании из накопителя выдается содержимое целой строки элементов памяти. Такая строка обычно содержит несколько слов. С помощью селектора из строки выделяется и передается на выход требуемое слово.

4.4 Перепрограммируемые постоянные запоминающие устройства

Перепрограммируемые ПЗУ обладают всеми достоинствами ПЗУ, храня записанную в них информацию неопределенно долго и при отключении питания. В то же время они допускают стирание записанной информации и запись новой информации. Однако если чтение осуществляется за доли микросекунды, то время записи на много порядков больше.

На рис. 4.14,а показан элемент памяти с электрической записью информации и стиранием ультрофиолетовым светом. На рис. 4.14,б приведена структура транзистора VТ2. Транзистор VТ1 служит для выборки элемента памяти, хранение информации осуществляется в транзисторе VТ2.

Стирание информации в одних микросхемах производится путем подачи соответствующих напряжений, в других – путем подачи ультрафиолетового излучения через прозрачную кварцевую крышку в корпусе микросхемы.

Рис. 4.13 Структура ПЗУ, программируемого пользователем

а) б)

Рис. 4.14

Перепрограммируемые ПЗУ дороже ПЗУ, и их применяют в процессе отладки цифровых устройств, когда необходимо уточнить информацию, которая должна храниться в памяти. После отладки ППЗУ можно заменить более дешевыми ПЗУ.

Основным устройством всех информационных систем является центральный процессор (ЦП). Из многочисленных ИС роль ЦП систем выполняют микропроцессоры. Обычно в технологии микроинформационной техники программную память, память данных, интерфейс ввода-вывода, дешифратор адресов выполняют на различных ИС.

Центральным устройством системы является микропроцессор, который содержит обычно элементы размещения данных, называемые регистрами, и устройство счета, называемое арифметико-логическим устройством (АЛУ).

Микропроцессор – программно - управляющее устройство, осуществляющее процесс обработки цифровой информации и управления им, построенное, как правило, на одной или нескольких интегральных микросхемах большой степени интеграции /из толкового терминологического словаря –справочника «Программные средства вычислительной техники», М.: Издательство стандартов, 1990 г/.

Микропроцессорная техника – совокупность технических и программных средств, используемых для построения различных микро-ЭВМ, микропроцессорных устройств и систем.

Микро-ЭВМ – вычислительная машина, созданная на основе микропроцессора и предназначенная в основном для встраивания в аппаратуру систем в качестве элементов, обеспечивающих логическую и арифметическую обработку информации.

Центральное устройство содержит также цепь декодирования команд и секцию управления и синхронизации. Оно снабжено также необходимыми соединениями с устройством ввода/вывода.

Основными функциями центрального устройства микроЭВМ являются следующие:

1) извлечение, декодирование и выполнение команд программы в указанном порядке;

2) передача данных из памяти и в память и из УВВ и в УВВ;

3) ответы на внешние прерывания;

4) установка общей синхронизации и сигналов управления для всей системы.

Большинство центральных устройств содержит, по меньшей мере, элементы, схематически представленные на рис. 4.15. Наиболее важные секции содержат различные регистры, АЛУ, дешифратор команд, устройства управления и синхронизации, а также УВВ. В настоящее время большинство микропроцессоров содержат множество дополнительных специальных регистров.

Арифметико-логическое устройство ЦП выполняет такие операции, как сложение, сдвиг/перестановка, сравнение, инкремент, декремент, отрицание, И, ИЛИ, ИЛИ ИСКЛЮЧАЮЩЕЕ, дополнение, сброс, инициализация.

Если АЛУ должно выполнить операцию сложения посредством команды ADD, процедура могла бы быть аналогичной представленной на рис. 4.16, а. Здесь содержимое аккумулятора ОАН складывается с содержимым регистра временного хранения данных 05Н. Сумма OFH помещена в аккумулятор.

На рис. 4.16, б приведены основные функциональные элементы типового АЛУ. Оно содержит сумматор и устройство сдвига, а результаты пересылаются в аккумулятор посредством внутренней шины данных. Регистр состояния слова в АЛУ является устройством чрезвычайно важным (его называют иногда регистром кода условий или индикатором)1. Этот регистр состоит из группы триггеров, которые могут быть установлены или сброшены исходя из результатов последней операции, выполненной АЛУ. Эти триггеры или индикаторы содержат указатели нуля, отрицательного результата, переноса и т. д. Индикаторы используются для принятия решений, когда вводятся команды ветвлений. Аккумулятор обычно используется в ходе большинства операций, выполняемых центральным устройством, например, передачи данных.

* Широко распространен термин флажковый регистр. Тогда соответствующие триггеры или индикаторы этого регистра называются флагами — флаг нуля, флаг знака и т. д.

Устройство управления и синхронизации (см. рис. 4.1)является наиболее сложным в центральном процессоре. Оно влияет на все события и управляет их протеканием внутри центрального устройства и во всей микро-ЭВМ. Мы упоминали в предыдущей теме, что каждая команда программы может быть разделена на этапы извлечения и выполнения. Каждый из них в свою очередь может быть разделен на элементарные микропрограммы. Микропрограммы каждой команды находятся в секции декодирования и выполняются блоком управления и синхронизации центрального устройства.

Шестнадцатиразрядный регистр, называемый счетчиком команд, представлен на рис. 4.1 как элемент, составляющий часть центрального устройства. Этот регистр служит для хранения адреса следующей команды, чтобы извлечь ее из памяти. Так как команды выполняются последовательно, счетчик команд считает прямым счетом, если только нет контрпорядка. Большая часть выпускаемых микропроцессоров имеет 16-разрядный счетчик команд, который может адресовать 64 К слов памяти посредством адресной шины. Нормальная последовательность выполнения команд программы может быть изменена специальными командами ветвления, вызова подпрограмм, возврата из подпрограмм или прерывания. Эти команды повлекут переход содержимого счетчика команд на другую величину, отличную от следующего старшего адреса. Чтобы вернуть программу в исходное состояние после последовательности ее запуска, оператор должен восстановить в счетчике команд номер первой команды программы.

Последовательность извлечение-декодирование-выполнение команд является основой функционирования вычислительной машины. Первая команда, извлеченная из памяти программы, определяет код операции первой команды и помещается в регистр команд устройством управления центральным процессором. Код операции истолковывается дешифратором команд, который указывает затем процессору процедуру управления и синхронизации, которой должна следовать программа для выполнения заданной команды.

Центральное устройство, показанное на рис. 4.1, является элементарным. Большая часть центральных устройств МП содержит, по меньшей мере, несколько дополнительных регистров (8 и 16 бит). Существуют очень большие различия в количестве и типе регистров в зависимости от типов МП.

Процессоры от 8088 до Pentium, применяемые в PC, являются однокристальными микропроцессорами — процессор располагается на одном кристалле в одном корпусе (микросхеме). Процессор Pentium II, однокристальным не является — здесь кристалл процессора и несколько кристаллов вторичного кэша собраны на общем картридже, хотя для потребителя это не так и существенно — все функции выполняет одно изделие. В зависимости от сложности процессора (числа выводов), его рассеиваемой мощности и назначения применяются различные типы корпусов:

DIP — Dual In-line Package, корпус с двухрядным расположением штырьковых выводов;

PGA — Pin Grid Array, керамический корпус с матрицей штырьковых выводов;

PQFP — Plastic Quad Flat Pack, пластиковый корпус с выводами по сторонам квадрата;

SPGA — Staggered PGA, корпус с шахматным расположением выводов;

SQFP — Small Quad Flat Pack, миниатюрный корпус с выводами по сторонам квадрата;

PPGA — Plastic Pin Grid Array, термоустойчивый пластмассовый корпус SPGA;

TCP — Таре Carrier Package, миниатюрный корпус с расположенными по периметру ленточными выводами;

S.E.C.C. — Single Edge Connector Cartridge, картридж процессора Pentium II — печатная плата с краевым разъемом, на которой смонтированы кристаллы процессора, кэш-памяти, охлаждающий радиатор и вентилятор.

Процессоры в корпусах DIP занимали много места, на их смену пришли компактные корпуса PGA, PPGA и SPGA, которые обычно устанавливаются в ZIF socket (Zero Insertion Force) — колодка (сокет) с нулевым усилием вставки. Корпуса PQFP, SQFP предназначены для установки в специальные колодки или припаивания к плате. Самые компактные из многоконтактных, корпуса TCP предназначены для припаивания, к системной плате портативных систем.

Таблица 4.1 Процессоры

|

Процессор |

Тип разъема |

Тактовая частота |

Объем КЭШ-памяти |

Частота шины данных |

Кодовое наименование, примечание |

|

Pentium II |

Slot1 |

233-400МГц |

512 Кбайт |

66-100МГц |

Deschutes |

|

Celeron |

Slot1 |

266-300МГц |

0 Кбайт |

66МГц |

Covington, построен на базе Deschutes |

|

Celeron |

Slot1 |

300-433 МГц |

128 Кбайт |

66МГц |

Mendocino, построен на базе Deschutes |

|

Celeron |

Socket 370 |

300-5300МГЦ |

128 Кбайт |

66МГц |

Mendocino, построен на базе Deschutes |

|

Pentium III |

Slot1 |

450МГц-1 ГГц |

256 Кбайт |

100-133 МГц |

Coppermine |

|

Pentium III |

Socket 370 |

500МГц-1,1 ГГц |

256 Кбайт |

100-133 МГц |

Coppermine |

|

Celeron |

Socket 370 |

533 МГц-1,1 ГГц |

128 Кбайт |

66-100 МГц |

Coppermine-128, построен на базе Pentium III Coppermine |

|

Pentium III |

Socket 370 |

1,133-1,4 ГГц |

256 или 512 Кбайт |

133 МГц |

Tualatin |

|

Celeron |

Socket 370 |

900 МГц-1,4 ГГц |

256 Кбайт |

100 МГц |

Tualatin-256, построен на базе Pentium III Tualatin |

|

Pentium VI |

Socket 423 |

1,3-1,8 ГГц |

256 Кбайт |

400 МГц |

Wilamette |

|

Pentium VI |

Socket 478 |

1,8-3,06 ГГц |

256 или 512 Кбайт |

400 или 533 или 800МГц |

Nortwood |

|

Celeron |

Socket 478 |

1,7-2,4 ГГц |

128 Кбайт |

400МГц |

Wilamette – 128, построен на базе Pentium VI Wilamette |

|

Celeron |

Socket 775 |

2930 МГц |

256 Кбайт L2 cashe |

533 МГц |

Prescott-256 |

|

Xeon DP |

Socket 604 |

3,2 ГГц |

2048 Кбайт L2 cashe |

533 МГц |

|

|

Процессоры фирмы AMD | |||||

|

Athlon XP 2600+ |

Socket A |

1917 МГц |

512 Кбайт |

333 МГц |

|

|

Athlon 64 3200+ |

Socket 754 |

2200МГц |

512 Кбайт |

333 МГц |

|

|

Sempron 3000+ |

Socket A |

2000МГц |

512 Кбайт |

333 МГц |

|

Процессор является основным «мозговым» узлом, в задачу которого входит исполнение находящегося в памяти программного кода. В настоящее время под словом «процессор» подразумевают микропроцессор — микросхему, которая, помимо собственно процессора, может содержать и другие узлы, например, кэш - память.

Программный код — это последовательность команд, или инструкций, каждая из которых определенным образом закодирована и расположена в целом числе смежных байт памяти.

Адрес (логический) текущей исполняемой инструкции хранится в специальном регистре — указателе инструкций IP (Instruction Pointer), который соответствует счетчику команд фон-неймановской машины. После исполнения так называемой линейной инструкции этот указатель увеличивает свое значение на ее длину, то есть он укажет на начало следующей инструкции. Линейная инструкция не нарушает порядок выполнения, определяемый последовательностью расположения инструкций в памяти (по нарастанию адреса). Кроме линейных инструкций существуют инструкции передачи управления, среди которых различают инструкции переходов и вызовов процедур. Эти инструкции в явном или неявном виде содержат информацию об адресе следующей выполняемой инструкции, который может указывать на относительно произвольную ячейку памяти. Инструкции переходов и вызовов могут быть безусловными (ни от чего не зависящими) и условными. Произойдет ли условный переход (вызов) или нет, зависит от состояния флагов (признаков) на момент исполнения данной инструкции. Если переход (вызов) не состоится, то исполняется инструкция, расположенная в памяти вслед за текущей. Вызов процедуры характерен тем, что перед ним процессор сохраняет в стеке (стек — это область ОЗУ) адрес следующей инструкции, и на этот адрес передается управление после завершения исполнения процедуры (этот адрес извлекается из стека при выполнении инструкции возврата). Переход выполняется безвозвратно.

Последовательность исполнения инструкций, предписанная программным кодом, может быть нарушена под воздействием внутренних или внешних (относительно процессора) причин. К внутренним причинам относятся исключения (exceptions) — особые ситуации, возникающие при выполнении инструкций. Наглядным примером исключения является попытка деления на ноль. При возникновении условия исключения процессор автоматически выполняет вызов процедуры обработки исключения, после которой он может вернуться к повторному исполнению инструкции, породившей исключение, или следующей за ней.

Внешними причинами изменения нормальной последовательности инструкций являются аппаратные прерывания — вызовы процедур под воздействием электрических сигналов на специальные выводы процессора. Эти сигналы могут подаваться совершенно неожиданно для исполняемой программы. Источниками аппаратных прерываний являются контроллеры и адаптеры периферийных устройств, генераторы меток времени, системы управления питанием и другие подсистемы.

В компьютере обязательно должен присутствовать центральный процессор (CPU — Central Processing Unit), который исполняет основную программу. В многопроцессорной системе функции центрального процессора распределяются между несколькими обычно идентичными процессорами для повышения общей производительности системы, а один из них назначается главным. В помощь центральному процессору в компьютер часто вводят сопроцессоры, ориентированные на эффективное исполнение каких-либо специфических функций. Широко распространены математические сопроцессоры, обрабатывающие числовые данные в формате с плавающей точкой; графические сопроцессоры, выполняющие геометрические построения и обработку графических изображений; сопроцессоры ввода-вывода, разгружающие центральный процессор от несложных, но многочисленных операций взаимодействия с устройствами.

Процессор фон-неймановской машины фактически может выполнять только один процесс, передавая управление от инструкции к инструкции согласно исполняемой программе.

Чем сложнее программа и больше объем обрабатываемых ею данных, тем больше ее потребности в памяти. В первых процессорах семейства память предоставлялась в виде сегментов с размером по 64 Кбайт, а суммарный объем программно адресуемой памяти не превышал значения в 1 Мбайт. Архитектура PC ограничивала размер оперативной памяти объемом в 640 Кбайт, начиная с нулевых адресов. Эта область называется стандартной памятью (conventional memory), и для прикладных программ из нее остается доступной область порядка 400-550 Кбайт (остальное «съедает» операционная система вместе с разными драйверами). Потребности решаемых задач довольно быстро переросли эти ограничения, и в процессоры ввели средства организации виртуальной памяти. Впервые они появились в 80286, но удобный для употребления вид приняли только в 32-разрядных процессорах (80386 и выше). Во-первых, было снято ограничение на 64-Кбайтный размер сегмента — теперь любой сегмент может иметь почти произвольный размер до 4 Гбайт. Во-вторых, был введен механизм страничной переадресации памяти (paging). Теперь любая страница (область фиксированного размера) виртуальной логической памяти (адресуемой программой в пределах выделенных ей сегментов) может отображаться на любую область физической памяти (реально установленной оперативной). Архитектура и микроархитектура процессоров

В IBM-совместимых ПК применяются процессоры, совместимые с семейством 80x86 фирмы Intel. В оригинальной машине IBM PC использовался процессор 8088 с 16-разрядными регистрами. Все следующие модели процессоров, в том числе 32-разрядные (386, 486, Pentium, Pentium Pro, Pentium II/III, Celeron, Pentium 4 от Intel, K5, Кб и К7 (Athlon и Duron) от AMD, MI, МП и Mill от Cyrix/ VIA) с расширениями ММХ, SSE и 3DNow!, включают в себя подмножество системы команд и архитектуры предыдущих моделей, обеспечивая совместимость с ранее написанным ПО. Далее в тексте знак + означает, что описание верно как для указанного процессора, так и для следующих за ним процессоров. При этом 286 означает процессор 80286, 386 — 80386, ..., Р5 означает Pentium, P6 — ряд процессоров 6-го поколения, включая Pentium Pro, Pentium I I/I II и Celeron. Например, P5+ означает применимость к процессорам Pentium, Pentium MMX, Pentium Pro, Pentium II, Celeron, Pentium III и Pentium 4.

Под архитектурой процессора понимается его программная модель, то есть программно-видимые свойства. Под микроархитектурой понимается внутренняя реализация этой программной модели. Для одной и той же архитектуры IA-32(Intel Architecture 32 bit) разными фирмами и в разных поколениях применяются существенно различающиеся микроархитектурные реализации, при этом, естественно, стремятся к максимальному повышению производительности (скорости исполнения программ).

В микроархитектуре процессоров 5-7 поколений — Pentium (MMX) и их близких аналогов, Pentium Pro, Pentium II/Ш, Celeron и, наконец, Pentium 4 и К7 — существенное значение имеет реализация различных способов конвейеризации и распараллеливания вычислительных процессов, а также других технологий, не свойственных процессорам прежних поколений.

Конвейеризация (pipelining) предполагает разбивку выполнения каждой инструкции на несколько этапов, причем каждый этап выполняется на своей ступени конвейера процессора. При выполнении инструкция продвигается по конвейеру по мере освобождения последующих ступеней. Таким образом, на конвейере одновременно может обрабатываться несколько последовательных инструкций, и производительность процессора можно оценивать темпом выхода выполненных инструкций со всех его конвейеров. Для достижения максимальной производительности процессора — обеспечения полной загрузки конвейеров с минимальным числом лишних штрафных циклов (penalty cycles) — программа должна составляться с учетом архитектурных особенностей процессора. Конечно, и код, сгенерированный обычным способом, будет исполняться на процессорах классов Pentium и Р6 достаточно быстро. Конвейер «классического» процессора Pentium имеет пять ступеней. Конвейеры процессоров с суперкоивейерной архитектурой (superpipelined) имеют большее число ступеней, что позволяет упростить каждую из них и, следовательно, сократить время пребывания в них инструкций. Гиперконвйер Pentium 4 имеет уже 20 ступеней.

Скалярным называют процессор с единственным конвейером, к этому типу относятся все процессоры Intel до 486 включительно. Суперскалярный (superscalar) процессор имеет более одного (Pentium — два) конвейера, способных обрабатывать инструкции параллельно. Pentium является двухпотоковым процессором (имеет два конвейера), Р6 — трехпотоковым.

Благодаря совершенствованию микроархитектуры от поколения к поколению возрастает производительность процессоров, причем этот рост обеспечивается двумя факторами. Во-первых, растет тактовая частота ядра. Каждая микроархитектура имеет свои пределы роста частоты. Здесь рекорд пока что у процессоров Р6, микроархитектура которых выдержала почти 10-кратное увеличение тактовой частоты, но для дальнейшего роста в Pentium 4 фирме Intel пришлось существенно удлинить конвейер. Во-вторых, сокращается число тактов процессорного ядра, требуемых на выполнение одной инструкции (в пересчете с темпа схода инструкций с конвейера). Так в среднем процессоры 1, 2, 3, 4, 5 и 6 поколений на одну инструкцию тратят 12, 5, 4, 2, 1 и 0,5 тактов.