- •Тема 1.1: Класифікація мікропроцесорів. Архітектура процесорів Intel 8086.

- •1.4. Структура вбудованого мікроконтролеру

- •1.5. Системна шина

- •Тема 2.2: Арифметичні операції над числами. Логічні операції над числами та строками. Умовні та безумовні переходи.

- •2.2.1 Додавання цілих чисел. Синтаксис команд

- •2.2.2 Віднімання цілих чисел. Синтаксис команд

- •2.2.3 Множення цілих чисел. Синтаксис команд.

- •2.2.4 Ділення цілих чисел. Синтаксис команд

- •2.2.5 Арифметичний зсув вліво і вправо. Синтаксис команд

- •2.2.6 Безумовний перехід та порівняння. Синтаксис команд.

- •2.3.3. Команди організації циклів. Синтаксис команд

- •3.1.2. Сегментні регістри. Состав шинного інтерфейсу.

- •3.1.3. Індексні регістри. Регістр флагів.

- •3.1.4. Функції алу. Призначення адресних входів алу

- •Тема 3.2: Система команд мікропроцесору i8080. Організація пам’яті та портів вводу/виводу.

- •Тема 5.1: Система команд i8086. Система переривів. Адресація пам’яті. Директиви передачі керування.

- •5.1.2. Команди перериву за переповненням. Синтаксис команд.

- •5.1.3. Повернення з переривів та підпрограм.

- •5.1.4. Сегментна організація пам’яті.

- •5.1.5. Фізична адреса байту в пам’яті.

- •5.1.6. Формування логічного адресу.

- •Тема 5.2: Сопроцесор і арифметичне розширення процесору. Синхронізація програми та керування таймером.

- •5.2.1. Функції та призначення сопроцесору.

- •5.2.4. Синхронізація сигналів таймеру.

- •Тема 5.3: Програмування вводу/виводу даних на зовнішні пристрої. Обмін даними в локальних мережах.

- •5.3.1. Функції інтерфейсу вводу/виводу.

- •5.3.2. Керування обміном даними. Програмний обмін.

- •5.3.3. Керування обміном даними. Обмін за переривом.

- •Тема 6.1: Архітектура мікроконтролеру i8086. Організація пам’яті і регістрів. Прямий доступ до пам’яті.

- •6.1.1. Організація пам’яті. Адресний простір.

- •6.1.2. Структура процесору i8086. Виконавчий модуль.

- •6.1.3. Структура процесору i8086. Шиний інтерфейс

- •6.1.4. Структура процесору i8086. Керування і таймінг.

- •6.1.5. Контролер динамічної пам'яті. Схема модуля.

- •Тема 6.2: Організація портів вводу/виводу. Інтерфейси зовнішніх пристроїв для взаємодії з технологічним обладнанням.

- •Тема 6.3: Тактовий генератор. Таймери. Лічильники. Внутрішня та зовнішня пам’ять. Шини адресу та даних.

- •6.3.1. Мікросхема тактового генератору.

- •6.3.2. Структурна схема програмованого таймеру.

- •6.3.3. Режими роботи програмованого таймеру.

- •6.3.4. Нарощування об’єму пам’яті.

- •Тема 6.4: Система переривів. Контролер переривів. Організація механізму переривів. Перериви таймеру.

- •6.4.1. Контролер переривів. Джерело переривів.

- •6.4.2. Запроси переривів. Типи векторів переривів.

- •6.4.3. Адреси функцій переривів. Приклад визову перериву.

- •Тема 7.1: Засоби організації обміну із зовнішніми приладами. Схема виводів. Програмовані виводи.

- •7.1.1. Схема виводів мікропроцесору i8086.

- •7.1.2. Адресація 8-бітного пристрою.

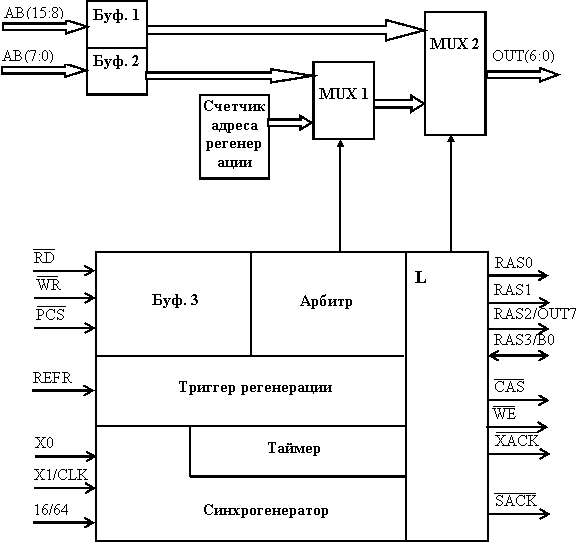

6.1.5. Контролер динамічної пам'яті. Схема модуля.

(КДП) обеспечивает мультиплексирование адреса системной шины, выработку управляющих сигналов CAS и RAS[3:0] (для селекции модулей ОЗУ), а также внутреннюю (по таймеру) или внешнюю (прозрачную) регенерацию. Структурная схема контроллера (Рис. 7.) включает в себя :

буферные схемы Буф.1,2,3 для подключения системной шины адреса и управления;

счетчик адреса регенерации;

мультиплексоры MUX1,2;

схему управления с тактовым генератором, таймером и триггером регенерации, арбитром и логической схемой L для формирования управляющих сигналов.

КДП обеспечивает преобразование сигналов системной шины МПС в сигналы управления динамическим ОЗУ (см. Рис. 7.16), причем может работать в двух режимах : "16/64" (на память 16K или 64K соответственно). В режиме "16" две старшие линии адреса используются для формирования одного из сигналов RAS\[0..3], в режиме "64" КДП может управлять двумя банками по 64K, причем сигнал RAS появляется на одном из выходов RAS0 или RAS1 - в зависимости от состояния линии RAS3\/B0, которая в режиме "64" становится входом, определяющим номер банка ОЗУ. Регенерация может осуществляться в двух режимах - внутреннем и внешнем. Если вход REFR остается неактивным 10..16 мкС, то формируется запрос на цикл регенерации от внутреннего таймера, причем в случае конфликта арбитр отдает предпочтение циклу памяти. Таким образом, и при регенерации по таймеру используются свободные такты шины. При внешней регенерации запрос должен быть сформирован на входе REFR. Сигнал PCS - "Защищенный выбор кристалла" отличается от традиционного CS тем, что если PCS сформирован, то цикл ЗУ аннулировать нельзя. RD, WR - запросы на циклы чтения и записи соответственно. X0, X1 - выводы для подключения кварцевого резонатора при работе с внутренним генератором. При работе с внешним генератором на вход X0 подается высокий потенциал, а на X1 - частота CLK внешнего генератора. Выходной сигнал SACK\ вырабатывается КДП в начале цикла обращения к памяти. Если запрос от МП приходится на цикл регенерации, то SACK\ задерживается до начала цикла чтения/записи. Выходной сигнал XACK\ ("Готовность данных") вырабатывается в конце цикла чтения/записи. Сигналы SACK\ и XACK\ можно использовать для управления потенциалом на входе READY микропроцессора.

Рис. 7.16. Контроллер динамического ОЗУ

Тема 6.2: Організація портів вводу/виводу. Інтерфейси зовнішніх пристроїв для взаємодії з технологічним обладнанням.

Адресация портов ввода-вывода. Для обращений к портам в пространстве ввода- вывода применяются два режима адресации. При прямой адресации фиксированный адрес порта находится непосредственно в команде, как ее второй байт, что обеспечивает. доступ к портам 0—255. При косвенной адресации номер порта находится в регистре DX и имеет диапазон от 0 до 65 535.

П.С. Каждое внешнее устройство должно быть связано с помощью интерфейса с шиной данных микропроцессорной системы так, чтобы данные могли быть переданы командами программы между этим устройством и микропроцессором. Каждый интерфейс устройства ввода/вывода должен быть адресуемым и отвечать на сигналы шины управления микропроцессора. Наиболее общий подход состоит в том, чтобы использовать один или большее количество регистров в интерфейсе устройства как буферы между устройством и процессором. Мы знаем эти буферные регистры как порты.

Програмування режиму вводу/виводу в порт. Приклад.

Работа с портами ввода/вывода в процессорах x86 возможна как с использованием специальных команд (IN, OUT), через отдельное адресное пространство ввода/вывода, так и по схеме с отображением регистров устройств на обычное адресное пространство. В последнем случае возможно использование обычных команд из системы команд процессора. Для адресации портов устройств в пространстве ввода/вывода, используется 16-разрядный адрес, обеспечивая доступ к 64K 8-битным портам с адресами от 0h до FFFFh. Адреса 0F8h – 0FFh– зарезервированы для системных целей. Порты с адресами 0h – 0FFh используются оборудованием системной платы ПК (таймер, контроллер прерываний и т.п.), адреса 0100h–03FFh используют различные контроллеры: дисков, видеомонитора, компьютерной сети.

Команды IN и OUT работают с прямой адресацией (адрес порта находится в команде) для портов с адресами 0h - 0F7h и с косвенной адресацией (адрес порта находится в регистре DX) для любых портов: 0h - FFFFh. Обмен данными происходит только через регистр-аккумулятор (AX, AL), например, чтение из порта: in al,dx , запись в порт: out dx,ax

ПРИМЕР: Ниже приведен фрагмент программы передачи одного байта данных на принтер. Интерфейс принтера представлен для микропроцессора двумя портами: регистром данных (Dat_Reg) и регистром состояния (Stat_Reg). Программа читает и проверяет младший бит регистра состояния устройства. Если этот бит – 1, устройство не готово принять данные от процессора, и программа ожидает в цикле, когда бит поменяет значение. Если бит – 0, устройство готово принимать данные и микропроцессор посылает информацию в регистр данных интерфейса устройства.

Check: IN AL,Stat_Reg ; чтение регистра состояния

AND AL, 00000001B ; проверка младшего бита

JNE Check ; регистра состояния

MOV AL,Data ;пересылка в регистр данных

OUT Dat_reg,AL ; интерфейса

Паралельний інтерфейс вводу/виводу.

Аппаратные средства и программное обеспечение, необходимые для связи периферийных устройств с микропроцессорной системой называются интерфейсом. Аппаратные средства интерфейса включают сигналы обмена данными а также оборудование, обеспечивающее этот обмен. Порядок следования сигналов во времени называется протоколом обмена.

По протоколу обмена интерфейсы делят на параллельные и последовательные. Стандартные интерфейсы общего применения обычно ориентированы на байтовый (восьмибитовый) обмен информацией. В параллельном интерфейсе байт данных передается по восьми линиям одновременно, а в последовательном по одной линии бит за битом последовательно. Естественно, под линией здесь понимается два провода (информационный и общий).

На рисунке показано подключение светодиода (VD1) к шинам микропроцессорной системы. Светодиод в данной схеме рассматривается как периферийное устройство. В качестве порта вывода используется D-триггер. Логическая схема определяет адрес этого порта. Информация, которая записывается в порт, стробируется сигналом IOWC. В данном примере использован параллельный способ адресации портов ввода/вывода.

\

\

Послідовний інтерфейс вводу/виводу.