- •Тема 1.1: Класифікація мікропроцесорів. Архітектура процесорів Intel 8086.

- •1.4. Структура вбудованого мікроконтролеру

- •1.5. Системна шина

- •Тема 2.2: Арифметичні операції над числами. Логічні операції над числами та строками. Умовні та безумовні переходи.

- •2.2.1 Додавання цілих чисел. Синтаксис команд

- •2.2.2 Віднімання цілих чисел. Синтаксис команд

- •2.2.3 Множення цілих чисел. Синтаксис команд.

- •2.2.4 Ділення цілих чисел. Синтаксис команд

- •2.2.5 Арифметичний зсув вліво і вправо. Синтаксис команд

- •2.2.6 Безумовний перехід та порівняння. Синтаксис команд.

- •2.3.3. Команди організації циклів. Синтаксис команд

- •3.1.2. Сегментні регістри. Состав шинного інтерфейсу.

- •3.1.3. Індексні регістри. Регістр флагів.

- •3.1.4. Функції алу. Призначення адресних входів алу

- •Тема 3.2: Система команд мікропроцесору i8080. Організація пам’яті та портів вводу/виводу.

- •Тема 5.1: Система команд i8086. Система переривів. Адресація пам’яті. Директиви передачі керування.

- •5.1.2. Команди перериву за переповненням. Синтаксис команд.

- •5.1.3. Повернення з переривів та підпрограм.

- •5.1.4. Сегментна організація пам’яті.

- •5.1.5. Фізична адреса байту в пам’яті.

- •5.1.6. Формування логічного адресу.

- •Тема 5.2: Сопроцесор і арифметичне розширення процесору. Синхронізація програми та керування таймером.

- •5.2.1. Функції та призначення сопроцесору.

- •5.2.4. Синхронізація сигналів таймеру.

- •Тема 5.3: Програмування вводу/виводу даних на зовнішні пристрої. Обмін даними в локальних мережах.

- •5.3.1. Функції інтерфейсу вводу/виводу.

- •5.3.2. Керування обміном даними. Програмний обмін.

- •5.3.3. Керування обміном даними. Обмін за переривом.

- •Тема 6.1: Архітектура мікроконтролеру i8086. Організація пам’яті і регістрів. Прямий доступ до пам’яті.

- •6.1.1. Організація пам’яті. Адресний простір.

- •6.1.2. Структура процесору i8086. Виконавчий модуль.

- •6.1.3. Структура процесору i8086. Шиний інтерфейс

- •6.1.4. Структура процесору i8086. Керування і таймінг.

- •6.1.5. Контролер динамічної пам'яті. Схема модуля.

- •Тема 6.2: Організація портів вводу/виводу. Інтерфейси зовнішніх пристроїв для взаємодії з технологічним обладнанням.

- •Тема 6.3: Тактовий генератор. Таймери. Лічильники. Внутрішня та зовнішня пам’ять. Шини адресу та даних.

- •6.3.1. Мікросхема тактового генератору.

- •6.3.2. Структурна схема програмованого таймеру.

- •6.3.3. Режими роботи програмованого таймеру.

- •6.3.4. Нарощування об’єму пам’яті.

- •Тема 6.4: Система переривів. Контролер переривів. Організація механізму переривів. Перериви таймеру.

- •6.4.1. Контролер переривів. Джерело переривів.

- •6.4.2. Запроси переривів. Типи векторів переривів.

- •6.4.3. Адреси функцій переривів. Приклад визову перериву.

- •Тема 7.1: Засоби організації обміну із зовнішніми приладами. Схема виводів. Програмовані виводи.

- •7.1.1. Схема виводів мікропроцесору i8086.

- •7.1.2. Адресація 8-бітного пристрою.

7.1.2. Адресація 8-бітного пристрою.

Имеется 8 регистров (АХ, СХ, DX, ВХ, SP, BP, SI, DI), которые можно использовать для хранения 16-разрядных данных; 8 регистров (AL, CL, DL, BL, АН, СН, DH, ВН), используемые для хранения 8-разрядных данных; 2 регистра \ВХ, BP), используемые в качестве базовых, и 2 регистра (SI, Р1) используемые в качестве индексных.

Таким образом, все регистры являются регистрами специального назначения, для адресации которых используются следующие восемь способов (универсальные для всех команд):

1) Непосредственный. Данное длинной 8 или 16 бит является частью команды. Например: выражение-константа: 12; 1010В; 08АH; ‘AB’; XX-YY-5.

2) Прямой. 16-битный эффективный адрес данного является частью команды. Например: переменная±выражение-константа: CNT; CNT+5; ARRAY-5.

3) Регистровый. Данное содержится в определяемом командой регистре (Аx, bx, cx, dx, si, di, sp, bp). Например: регистр: AX; BH; DL.

4) Регистровый косвенный. Эффективный адрес данного находится в базовом регистре BX или индексном SI,DI:

.

.

Например: [регистр]: [BX].

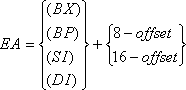

5) Регистровый относительный. Эффективный адрес равен сумме 8 или 16 битного смещения и содержимого базового или индексного регистров:

.

.

Например: переменная + [регистр±выражение константа]: CST[BX]; MES[SI+10H]; [BX-1].

6) Базовый индексный. Эффективный адрес равен сумме содержимого базового и индексного регистров, определяемых командой:

.

.

Например: [базовый регистр][индексный регистр] : [BX][DI].

7) Относительный базовый индексный. Эффективный адрес равен сумме 8 или 16 битного смещения и базово-индексного адреса:

.

.

Например: переменная + [базовый регистр±выражение константа] [индексный регистр±выражение константа] : E[BX+5][SI-2]; DATA[BX][SI]; [BX+2][SI].