- •Тема 1.1: Класифікація мікропроцесорів. Архітектура процесорів Intel 8086.

- •1.4. Структура вбудованого мікроконтролеру

- •1.5. Системна шина

- •Тема 2.2: Арифметичні операції над числами. Логічні операції над числами та строками. Умовні та безумовні переходи.

- •2.2.1 Додавання цілих чисел. Синтаксис команд

- •2.2.2 Віднімання цілих чисел. Синтаксис команд

- •2.2.3 Множення цілих чисел. Синтаксис команд.

- •2.2.4 Ділення цілих чисел. Синтаксис команд

- •2.2.5 Арифметичний зсув вліво і вправо. Синтаксис команд

- •2.2.6 Безумовний перехід та порівняння. Синтаксис команд.

- •2.3.3. Команди організації циклів. Синтаксис команд

- •3.1.2. Сегментні регістри. Состав шинного інтерфейсу.

- •3.1.3. Індексні регістри. Регістр флагів.

- •3.1.4. Функції алу. Призначення адресних входів алу

- •Тема 3.2: Система команд мікропроцесору i8080. Організація пам’яті та портів вводу/виводу.

- •Тема 5.1: Система команд i8086. Система переривів. Адресація пам’яті. Директиви передачі керування.

- •5.1.2. Команди перериву за переповненням. Синтаксис команд.

- •5.1.3. Повернення з переривів та підпрограм.

- •5.1.4. Сегментна організація пам’яті.

- •5.1.5. Фізична адреса байту в пам’яті.

- •5.1.6. Формування логічного адресу.

- •Тема 5.2: Сопроцесор і арифметичне розширення процесору. Синхронізація програми та керування таймером.

- •5.2.1. Функції та призначення сопроцесору.

- •5.2.4. Синхронізація сигналів таймеру.

- •Тема 5.3: Програмування вводу/виводу даних на зовнішні пристрої. Обмін даними в локальних мережах.

- •5.3.1. Функції інтерфейсу вводу/виводу.

- •5.3.2. Керування обміном даними. Програмний обмін.

- •5.3.3. Керування обміном даними. Обмін за переривом.

- •Тема 6.1: Архітектура мікроконтролеру i8086. Організація пам’яті і регістрів. Прямий доступ до пам’яті.

- •6.1.1. Організація пам’яті. Адресний простір.

- •6.1.2. Структура процесору i8086. Виконавчий модуль.

- •6.1.3. Структура процесору i8086. Шиний інтерфейс

- •6.1.4. Структура процесору i8086. Керування і таймінг.

- •6.1.5. Контролер динамічної пам'яті. Схема модуля.

- •Тема 6.2: Організація портів вводу/виводу. Інтерфейси зовнішніх пристроїв для взаємодії з технологічним обладнанням.

- •Тема 6.3: Тактовий генератор. Таймери. Лічильники. Внутрішня та зовнішня пам’ять. Шини адресу та даних.

- •6.3.1. Мікросхема тактового генератору.

- •6.3.2. Структурна схема програмованого таймеру.

- •6.3.3. Режими роботи програмованого таймеру.

- •6.3.4. Нарощування об’єму пам’яті.

- •Тема 6.4: Система переривів. Контролер переривів. Організація механізму переривів. Перериви таймеру.

- •6.4.1. Контролер переривів. Джерело переривів.

- •6.4.2. Запроси переривів. Типи векторів переривів.

- •6.4.3. Адреси функцій переривів. Приклад визову перериву.

- •Тема 7.1: Засоби організації обміну із зовнішніми приладами. Схема виводів. Програмовані виводи.

- •7.1.1. Схема виводів мікропроцесору i8086.

- •7.1.2. Адресація 8-бітного пристрою.

2.3.3. Команди організації циклів. Синтаксис команд

Структура циклов

<метка>:

Тело цикла

Loop <метка>

Команда loop выполняет уменьшение значения в регистре сх на единицу.

Пример

mov cx, 10

jcxz label;

cycle;

dec cx;

loop cycle;

label: ;

<метка>:

Loopne <метка> ; уменьшение значения сх на единицу; если zF=0 cx=cx-1

Переход на на <метку> внутри сегмента цикла

Если zF=1 переход на <метку> вне cегмента

2.3.4. Префікс повторення команд передачі даних. Приклад.

mov cx, 3

rep mov ax, bx

Команда повторяется сх раз.

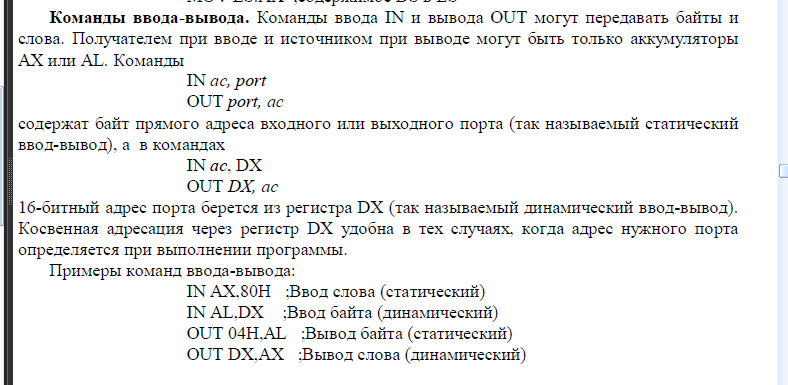

Тема 2.4: Організація обміну даними. Пересилка даних. Ввід/вивід даних в порт.

2.4.1 Команди передачы даних. Синтаксис команд

mov <операнд-источник>, <операнд-приемник>;

операнд-источник ->операнд-приемник

xchg <операнд 1>, <операнд 2>;

операнд 1<->операнд 2

xchg – команда двунаправленной пересылки

2.4.2. Команди встановлення та збросу флагів

Позволяет принудительно установить значение флагов.

STC; устанавливает CF=1

CLC; сбросить флаг в CF=0

Пример

STC; CF=1

jc label ; есть перенос перейти на label

2.4.3 Команди напрямку переміщення по строчці

STD - установка DF=1

CLD - установка DF=0

DF используется для указания направления движения при побитном анализе.

2.4.4 Загрузка адресу змінної в памяті

LEA – регистр, <операнд>

Загружает в регистр относительный адрес операнда.

MOV регистр, offset <операвнд>

Команда загружает в регистр относительный адрес операнда со смещением.

(оffset <начальный адрес> + <смещение>)

Тема 2.5: Структури даних. Операції з масивами. Використання підпрограм.

2.5.1. Пряма адресація. Доступ до змінної в памяті.

.data

mem 1 dw 1 Deh

.code

mov AX, mem 1; AX<- [1DFh]

lea SI, [AX+0Fh]; SI<-[1DFh+0Fh]

2.5.2. Базова адресація. Сегментна адреса.

Пример доступа к ячейке памяти с базовым адресом А020

mov si, A020h; si <- значение элемента

mov ax, [si]; ax<- значение по адресу А020h

2.5.3. Індексна адресація із зсувом. Ефективний адрес операнду

Используется для доступа к произвольным элементам массива.

.data

base dw 0Fh

shift dw 1DFFh

.code

mov bx, base; bx<-base

mov di, shift; di<- shift

lea si, [bx+di]; si<-[bx+di]

mov ax, [si]; ax<- значение по адресу si

2.5.4. Базово-індексна адресація. Формування адресу в памяті

Формирование адреса

.date

Mem dd EFFh

.code

Mov dx, mem

2.5.5. Використання ефективного адресу прироботі з масивами

Пример организации доступа к элементам массива

.data

mas db -1,0,3,-8,0

.code

lea ax, mas; получение относительного адреса первого элементав массива

mov bx, 2h; формируем смещение в 2 байта

mov dx, [ax+bx]

2.5.6. Використання підпрограм. Синтаксис команди.

Call <метка>

; точка выхода из подпрограммы

; конец сегмента данных

<metka>

; тело подпрограммы

ret

Тема 3.1: Структурна організація мікропроцесорів сімейства i8080.

3.1.1. Регістри даних загального призначення.

Ці вісім регістрів доступні для зберігання проміжних даних і вказівників. Вони є 16 – ти розрядними регістрами АХ, ВХ, СХ, ДХ, ВР, SI, SP.,DI.

Соответствуют типу даных dv , которые могут быть занесены в эти регистры. Эти регистры используются для выполнения арихметических и логических операций: сложение(add) вычисление(sub) сложение(and).

Типичным представителем 8-разрядного МП есть Intel8080, КР 580.

МП имеет 8-разрядную шину данных и 8-разрядное операционное устройство, 16-разрядную шину адреса. МП, выполненный на основе n-МОП технологий. Питание имеют уровни 12В, ±5В.

8080 является однокристальным микропроцессором, работающим с 8-разрядной шиной данных и 16-разрядной шиной адреса. Управляющие сигналы передаются по шине управления. Шины отделены друг от друга. Структура Intel 8080 приведена на рис. 1.