- •Исходные данные:

- •Задание

- •Минимизация фал

- •Схемная реализация клу в базисе 2и-не

- •Автоматический синтез схем

- •Проверка функционирования схемы

- •13-Й кодовой комбинации

- •Определение быстродействия

- •Определение потребляемого тока

- •Схемная реализация клу на мультиплексоре

- •Получение остаточной фал

- •Проверка функционирования

- •Сравнительный анализ схемных реализаций клу

Схемная реализация клу в базисе 2и-не

Автоматический синтез схем

В EWB имеется специальный «виртуальный» прибор Logic Converter (Логический преобразователь), преобразующий таблицу истинности в ФАЛ типа (2) и обратно, а также осуществляющий минимизацию ФАЛ. После этого можно автоматически синтезировать схему либо в базисе основных логических операций (И, ИЛИ, НЕ), либо в базисе 2И-НЕ. Можно выполнять и обратные операции, т.е. получать таблицы истинности и ФАЛ готовых схем. Максимальное количество логических переменных преобразователя равно восьми, что эквивалентно 28 = 256 кодовым комбинациям.

Рисунок 2 – ФАЛ в виде СДНФ (штрихи около символов означают инверсию) результат совпадает с примером 2.

Рисунок 3 – минимизированный ФАЛ совпадает с (3)

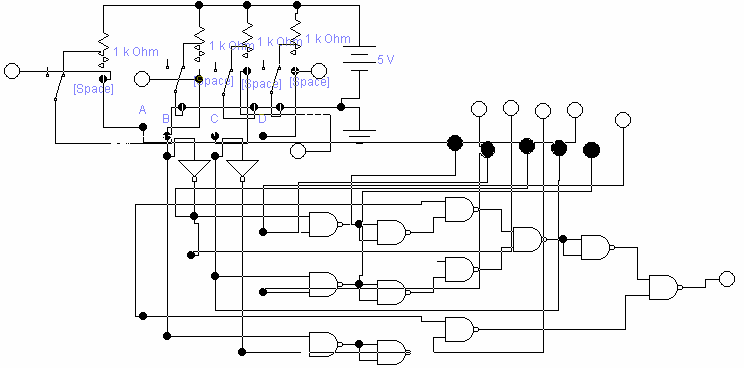

Рисунок 4 – Схема КЛУ, рализующая ФАЛ (3) в базисе 2И-НЕ

Проверка функционирования схемы

Проверим функционирование полученной схемы путем подачи на вход кодовых комбинаций из таблицы истинности. Используем схемы параллельных ключей для обеспечения сигналов положительной логики, соответствующих высокому (логическая единица) и низкому (логический нуль) уровням напряжения.

Рисунок 5 – Состояние Логических пробников при

13-Й кодовой комбинации

Определение быстродействия

Как известно, изменение состояния реальных логических элементов не происходит мгновенно, что ограничивает их быстродействие. Причиной этого являются переходные процессы, возникающие при переключении транзисторов и перезарядке паразитных емкостей. Быстродействие характеризуется двумя параметрами: средним временем задержки распространения импульса (или сигнала) tзр.ср и максимальной рабочей частотой Fмакс. При превышении Fмакс нарушается логика работы элемента, появляются ложные нули и единицы, т.е. теряется работоспособность.

Все сказанное распространяется и на КЛУ, состоящее из большого числа логических элементов. При этом под tзр.ср понимают суммарную задержку, возникающую в самой длинной цепи между входом и выходом. Эту цепь достаточно просто определить непосредственно по схеме, двигаясь от выхода к входу.

Рисунок 6 – Визуализация функционирования самой длиной цепи

Перебирая все возможные комбинации сигналов а, b, с, выясняем, при какой из них переключение ключа b приводит к изменению свечения рядов пробников. В рассматриваемом случае это имеет место при а = 1, b = 0, с = 0 (см. рисунок 6) Если ключ D разомкнуть, то нижний ряд пробников погаснет, а верхний

засветится.

Рисунок 7 – Входной (внизу) и выходной (вверху) сигналы

КЛУ при частоте 100 кГц

Установим частоту 100 кГц. Результат показан на рисунке 7. Запаздывание равно 201 нс, что составляет 5,5% периода. При частоте 200 кГц запаздывание составляет 10%. Поэтому принимаем Fмакс = 200 кГц в соответствии с указанным выше критерием для Fмакс.

Определение потребляемого тока

По условию количество корпусов микросхем должно быть минимальным. В связи с этим необходимо проанализировать состав заданной серии на предмет наличия микросхемы, содержащей наибольшее число элементов 2И-НЕ. В составе серии К561 имеется микросхема К561ЛА7, содержащая 4 элемента 2И-НЕ с общим питанием.

Потребляемый ток в статическом режиме составляет 0,5 мкА на корпус. Рассматриваемое КЛУ содержит 22 элемента 2И-НЕ. Следовательно, необходимо 6 корпусов, причем два элемента одного из них будут не задействованы. Таким образом, ток потребления КЛУ в статическом режиме составляет 3 мкА.