- •Министерство образования Российской Федерации

- •Самарский государственный технический университет

- •2. Оформление курсового проекта

- •3. Описание вариантов заданий

- •Перечень операций подлежащих программированию

- •4. Архитектура микропроцессоров

- •4.1. Микрокомпьютер

- •4.2. Структура микропроцессора

- •4.3. Блок управления и синхронизации

- •4.4. Система команд

- •4.4.1. Фаза выборки и дешифрации

- •Обозначения, используемые при описании команд,

- •Команды передач управления

- •Команды обращения к подпрограммам

- •Арифметические и логические команды

- •Команды ввода/вывода

- •Специальные команды

- •4.4.2. Фаза выполнения

- •Команды пересылки

- •Команды с непосредственным адресом

- •Команды обращения к памяти

- •Команды передачи управления

- •Команды обращения к подпрограммам

- •Арифметические и логические команды

- •Команды ввода/вывода

- •Специальные команды

- •4.5. Способы адресации

- •Прямая адресация

- •Непосредственная адресация

- •Индексная адресация

- •Косвенная адресация

- •Относительная адресация

- •Страничная адресация

- •4.6. Некоторые другие команды, специфичные для микропроцессоров

- •Арифметические и логические команды с операндами в главной памяти

- •Команды условных переходов

- •Команды обработки данных

- •5. Программирование для микропроцессоров

- •5.1. Программирование на машинном языке

- •Пример программы: «прибавить константу к числу в памяти и записать результат снова в память»

- •5.2. Разветвления в программах

- •5.3. Программирование циклов

- •Программа вычисления суммы десяти 8-битовых чисел без знаков

- •5.4. Программирование сложных разветвлений

- •Программа сложного разветвления, использующая таблицу переходов

- •5.5. Подпрограммы

- •Вход в подпрограмму и выход из подпрограммы

- •Параметры подпрограммы

- •Пример передачи параметров от главной программы в подпрограмму через общие регистры

- •Сложение с п-кратной точностью

- •Подпрограмма сложения чисел с двойной точностью

- •Умножение

- •5.6. Загрузка программ

- •Подпрограмма умножения целых положительных чисел Распределение общих регистров: r2: счетчик, r3: множимое y, r4: множитель X, r5: ст. Часть произведения Рн, r6:мл. Часть произведения pl

- •80 (Маска)

- •Программа-загрузчик

- •5.7. Программирование на языке ассемблера

- •Ассемблеры

- •Язык ассемблера

- •Программа на языке ассемблера, соответствующая программе табл. 5.3

- •Директивы ассемблера

- •Макрокоманда

- •Список команд иллюстрированного микропроцессора

- •Список команд иллюстративного микропроцессора

- •Условные графические обозначения в схемах

- •Продолжение Приложение п3

- •Продолжение Приложение п3

- •Продолжение Приложение п3

- •Список литературы

- •Содержание и объем курсового проекта …………………………….

- •Оформление курсового проекта ……………………………………...

- •Продолжение Приложение п2

- •Продолжение Приложение п2

- •Продолжение Приложение п2

- •Продолжение Приложение п2

- •Приложение п2

- •Приложение п2

- •Список литературы

4.4. Система команд

Обычно микропроцессор выполняет команды из некоторого фиксированного набора, называемого системой команд. Разные микропроцессоры имеют различные системы команд. Детальное описание системы команд нашего иллюстративного микропроцессора приведено в табл. 4.1 и 4.2. Для каждой команды приводится ее символическое обозначение, формат, а также символическое и словесное описание выполняемого действия. Никаких других команд наш микропроцессор выполнять не может, следовательно, решение любой задачи должно быть представлено в виде последовательности этих команд.

Формат каждой команды в табл. 4.2 полностью определяет представление команды в памяти компьютера. Таким образом, команда в памяти хранится как последовательность из нулей и единиц. С другой стороны, для человека много удобнее символические обозначения. Поэтому при написании программ можно пользоваться символической формой, преобразуя ее в машинный двоичный формат непосредственно перед вводом в машину. Во всех наших описаниях мы также для удобства будем пользоваться символической формой представления команд.

4.4.1. Фаза выборки и дешифрации

Обычно команды выполняются в последовательном порядке. Будем предполагать, что все программы начинаются с команды в ячейке 000016. Время, нужное, чтобы прочитать команду из памяти, декодировать ее и выполнить, называется командным циклом. Ввиду того что команды могут состоять из одного, двух и трех байтов и что время их выполнения может быть разным, командный цикл не является постоянной величиной. Следовательно, нам необходима .некоторая меньшая единица времени. В предыдущем разделе такая единица была введена в виде машинного цикла, состоящего из трех тактов синхронизации.

Таблица 4.1

Обозначения, используемые при описании команд,

приведенных в таблице 2

Обозначение |

Комментарий |

(X) |

Содержимое Х |

r |

Код из 2 битов, обозначающий один из общих регистров 0000, 0001 и 0010 (т. е. Асс, Н и L) двухбитовыми комбинациями 00, 01 и 10 соответственно |

R |

Номер любого общего регистра от 0000 до 1111 |

d |

Указатель направления передачи. 0 соответствует «tо» 1 - «from» (т. e. «в» и «от») |

— > |

Передается на |

Асс |

Аккумулятор, т. е. общий регистр 0000 |

Ассi |

Разряд аккумулятора с номером i. Разряды нумеруются от младших к старшим, i = 0, 1, … ,7 |

С |

Триггер переноса |

Н |

Общий регистр 0001 |

L |

Общий регистр 0010 |

HL |

Пара регистров Н и L |

М |

Ячейка главной памяти с адресом (Н) (L); ссылка на нее задается как ссылка на общий регистр 1111 |

<В2> |

Второй байт команды |

<В3> |

Третий байт команды |

M[X] |

Ячейка главной памяти с адресом X |

PC |

Программный счетчик |

Stacki |

Регистр стека с номером i |

Stack L2 |

Младшая половина второго регистра стека |

Stack HO2 |

Младший разряд старшей половины второго регистра стека |

+ |

Арифметическое сложение |

|

Логическое умножение (И) |

|

Логическое сложение (ИЛИ) |

|

Логическое ИСКЛЮЧАЮЩЕЕ ИЛИ |

Таблица 4.2

Система команд иллюстративного микропроцессора

Замечание: При всех передачах содержимое регистра, из которого передаются данные, не изменяется, если это особо не оговорено.

Команды пересылки

Команда: MOVE (пересылка)

Символическая форма: MOVr to R или MOV r from R

![]()

d = 0 d = 1

Описание: (r) R или (R) r

Если d=0, то содержимое общего регистра r передается в общий регистр R.

Если d=l, то содержимое общего регистра R передается в общий регистр r.

Команды с непосредственной адресацией

Команда: LOAD REGISTER IMMEDIATE (загрузка регистра непосредственная) Символическая форма: LRI R

Описание: <В2> R

Второй байт команды передается в общий регистр R.

Команды обращения к памяти

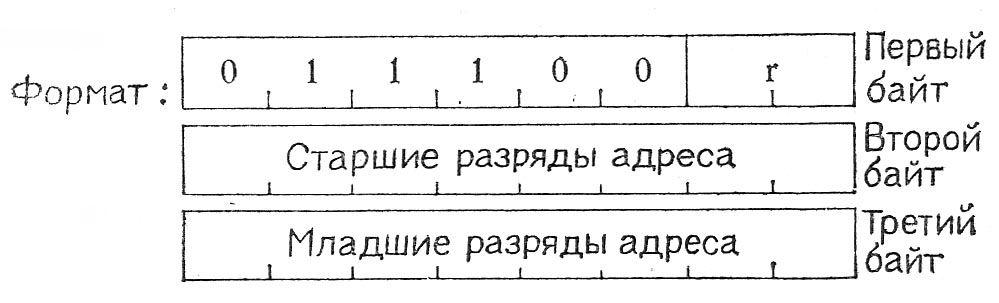

Команда: LOAD REGISTER (загрузка регистра)

Символическая форма: LDR r

Описание: (М [<В2> <В3>]) r

Содержимое ячейки памяти передается в общий регистр r.

Старшие 8 разрядов адреса ячейки берутся из второго байта команды, а младшие 8 разрядов — из третьего байта.

Команда: STORE REGISTER (запоминание регистра)

Символическая форма: STR r

Описание: (г) М [<В2> <В3>]

Содержимое общего регистра r передается в ячейку главной памяти.

Старшие 8 разрядов адреса ячейки указаны во втором байте команды, а младшие 8 разрядов—в третьем байте.