По способу действия

Последовательные (одноразрядные), в которых обработка разрядов чисел ведётся поочерёдно, разряд за разрядом, на одном и том же одноразрядном оборудовании;

Параллельные (многоразрядные), в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование;

Двоичный сумматор

В своей простейшей форме (на рисунке № 1) сумматор имеет 4 сигнальных линии: пара входов для сигналов, представляющих одноразрядные двоичные числа "А" и "В", выход "S" (сумма "А" и "В") и сигнал переноса "M". Эта схема, которая обеспечивает складывание однобитных чисел "А" и "В", при этом "S" наименее значимый бит, "M" наиболее значимый бит, называется "полусумматор".

Задействовав дополнительную схему "ИЛИ" (на рисунке зелёного цвета), можно подключить две этих "половинки" вместе (на рисунке № 2) и создать новую схему с дополнительным входом, "m", который принимает сигнал переноса старшего бита из предыдущей схемы. Такое составление двух "полусумматоров" даёт полный сумматор.

Схема полного сумматора может быть использована в качестве "строительных блоков" для построения схем, путём добавления двоичных чисел с неограниченным числом бит, как показано на рисунке № 3. Для каждой цифры, которую схема должна быть в состоянии обрабатывать, используется один полный сумматор и сигнал переноса "M" от предыдущего сумматора на вход последующего.

Двоичный одноразрядный полный сумматор является полной тринарной (трёхоперандной) двоичной логической функцией с бинарным (двухразрядным) выходом. Все три операнда и оба выходных разряда однобитные.

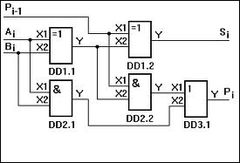

Может быть построен как тринарная (трёхоперандная) двоичная функция с бинарным выходом, но, для уменьшения аппаратных затрат, обычно строится трёхступенчатым, состоящим из трёх узлов: двух полусумматоров, которые являются полными бинарными (двухоперандными) двоичными логическими функциями с унарным выходом и логического элемента «2ИЛИ».

Троичный сумматор

Так как возможно несколько видов физической реализации троичных систем: трёхуровневая однопроводная, двухуровневая двухразрядная двухпроводная, двухуровневая трёхразрядная одноединичная трёхпроводная, двухуровневая трёхразрядная однонулевая и др., то возможны и несколько видов троичных сумматоров.

Кроме этого, сумматоры в несимметричной троичной системе счисления отличаются логикой работы от сумматоров в симметричной троичной системе счисления.

Троичный одноразрядный полный сумматор в троичной несимметричной системе счисления является неполной тринарной (трёхоперандной) троичной логической функцией. Два операнда — два слагаемых — полные, третий операнд — троичный разряд переноса — неполный и имеет только два значения 0 и 1 из трёх.

Троичный полный тринарный одноразрядный сумматор, работающий в троичной симметричной системе счисления Фибоначчи, является полной тринарной троичной логической функцией с двухразрядным результатом

Компараторы кодов

Компаратор (аналоговых сигналов) (англ. comparator — сравнивающее устройство) — электронная схема, принимающая на свои входы два аналоговых сигнала и выдающая логическую «1», если сигнал на прямом входе («+») больше чем на инверсном входе («−»), и логический «0», если сигнал на прямом входе меньше, чем на инверсном входе.

Простейший компаратор представляет собой дифференциальный усилитель. Компаратор отличается от линейного операционного усилителя (ОУ) устройством и входного, и выходного каскадов:

Входной каскад компаратора должен выдерживать широкий диапазон входных напряжений между инвертирующим и неинвертирующим входами, вплоть до размаха питающих напряжений, и быстро восстанавливаться при изменении знака этого напряжения. В ОУ, охваченном обратной связью, это требование некритично, так как дифференциальное входное напряжение измеряется милливольтами и микровольтами.

Выходной каскад компаратора выполняется совместимым по уровням и токам с конкретным типом логических схем (ТТЛ, ЭСЛ и т. п.). Возможны выходные каскады на одиночном транзисторе с открытым коллектором (совместимость с ТТЛ и КМОП логикой).

При подаче эталонного напряжения на инвертирующий вход, входной сигнал подаётся на неинвертирующий вход и компаратор является неинвертирующим (повторителем, буфером).

При подаче эталонного напряжения на неинвертирующий вход, входной сигнал подаётся на инвертирующий вход и компаратор является инвертирующим (инвертором).

Несколько реже применяются компараторы на основе логических элементов, охваченных обратной связью (см., например, триггер Шмитта — не компаратор по своей природе, но устройство с очень схожей областью применения).