- •1 Технология разработки систем на кристалле. Преимущества языка vhdl.

- •2 Архитектура плис фирмы Xilinx.

- •3 Модели вычислителей vhdl.

- •4 Объекты и типы языка vhdl.

- •5 Интерфейс и архитектура объекта в языке vhdl.

- •6 Использование нескольких архитектурных тел для одного объекта в языке vhdl.

- •7 Выражения языка vhdl.

- •8 Последовательные операторы языка vhdl.

- •9 Операторы цикла в языке vhdl.

- •10 Операторы процесса языка vhdl.

- •11 Процедуры и функции в языке vhdl. Атрибуты.

- •12 Параллельные операторы языка vhdl.

- •14 Повторное использование подсхем в языке vhdl.

- •15 Использование оператора generate в языке vhdl.

- •16 Проектирование комбинационных схем на языке vhdl.

- •17 Проектирование схем с памятью на языке vhdl.

- •18 Требования к проектированию плис и сбис.

- •19 Принципы однотактной и двухтактной синхронизации.

- •20 Состав и назначение библиотеки ieee.

- •2.Пакеты numeric_bit и numeric_std.

- •3. Пакеты math_real, math_complex.

- •1 Исп. Компон. Элемента «и» и оператор конструкции компонента

- •2 Исп комп эл «и» и «и-не»

- •3 Используйте генератор generate

- •4 Каждый логический элемент д б описан как отдельный объект, т. Е. Описание в целом д. Б. Выполнено в структурном стиле

- •5 В поведенческом стиле

- •6 Исп комп эл «или»

- •7 Исп комп эл «или» и «или-не»

- •8 Оператор generate

- •9 Каждый логический элемент д б описан как отдельный объект, т. Е. Описание в целом д б выполнено в структурном стиле

- •10 В поведенческом стиле

4 Каждый логический элемент д б описан как отдельный объект, т. Е. Описание в целом д. Б. Выполнено в структурном стиле

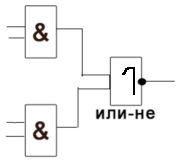

Задача №4

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. Каждый логический элемент д.б. описан как отдельный объект, т.е. описание в целом д.б. выполнено в структурном стиле.

Решение

-- Интерфейс "И"

entity entity_and is port (in1, in2: in BIT; q: out BIT); end entity_and;

-- Архитектура "И"

architecture architecture_and of entity_and is begin

q<=in1 and in2;

end architecture_and;

-- Интерфейс "И-НЕ"

entity entity_and_not is port (in1, in2: in BIT; q: out BIT); end entity_and_not;

-- Архитектура "И-НЕ"

architecture architecture_and_not of entity_and_not is begin

q<= not (in1 and in2);

end architecture_and_not;

-- Интерфейс компонента "ИЛИ"

entity entity_or is port (in1, in2: in bit; q: out bit); end entity_or;

-- Архитектура компонента "ИЛИ"

architecture architecture_or of entity_or is begin

q<=in1 or in2;

end architecture_or;

-- Интерфейс основного компонента

entity entity_main is port (i1,i2,i3,i4:in bit; QQ: out BIT); end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_and port (in1, in2 : in BIT; q: out BIT); end component;

component entity_and_not port (in1, in2 : in BIT; q: out BIT); end component;

component entity_or port (in1, in2: in BIT; q:out BIT); end component;

signal q1,q2: BIT;

begin

label1: entity_and_not port map (i1,i2,q1);

label2: entity_and port map (i3,i4,q2);

label3: entity_or port map (q1,q2,QQ);

end architecture_main;

5 В поведенческом стиле

Задача №5

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. Описание в целом д.б. выполнено в поведенческом стиле.

Решение

-- Интерф основного компонента

entity entity_main is

port (i1, i2, i3, i4 : in BIT;

QQ: out BIT);

end entity_main;

-- Архитектура осн.компонента-

architecture architecture_main of entity_main is

begin

QQ<=not((i1 and i2) or (i3 and i4));

end architecture_main;

6 Исп комп эл «или»

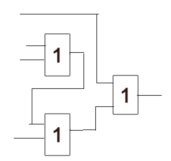

Задача №6

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте компонент элемента “ИЛИ” и оператор конкретизации компонента.

Решение

-- Интерфейс компонента “ИЛИ”

entity entity_or is

port (in1, in2: in bit;

q: out bit);

end entity_or;

-- Архитектура компонента “ИЛИ”

architecture architecture_or of entity_or is begin

q<=in1 or in2;

end architecture_or;

-- Интерфейс основного компонента

entity entity_main is

port (i1, i2, i3, i4 : in BIT;

QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_or

port (in1, in2 : in BIT;

q: out BIT);

end component;

signal q1,q2: BIT;

begin

label1: entity_or

port map (i2, i3, q1);

label2: entity_or

port map (q1, i4, q2);

label3: entity_or

port map (i1, q2, QQ);

end architecture_main;