- •1.Параметры усилителей

- •4. Основные характеристики усилителей

- •5 .Способы задания режимов по пост. Току ус-ых каскадов на бт

- •6. Способы задания режимов по пост. Току ус-ых каскадов на пт

- •11. Влияние ос на коэфф. Усилителя и стабильность

- •12. Усилительный каскад в схеме с ок (эмиттерный габарит)

- •13. Усилители постоянного тока (упт)

- •14. Методы борьбы с дрейфом нуля

- •17,18.Мостовые схемы. Дифференциальные усилители.

- •18. Дифференциальные усилители

- •19. Метод модуляции, демодуляции

- •22. Операционные усилители

- •2 3. Инвертируемый усилитель

- •24. Неинвертирующий усилитель

- •27. Основные параметры ключей

- •28. Простейший ключ на бт.

- •31.Ключи на полевых транзисторах (пт)

- •32. Ключи на комплементарных тр-рах.

- •33. Параметры логических элементов

- •Преимущества и недостатки

- •Резисторно-емкостная транзисторная логика (ретл)

- •Достоинства и недостатки ртл и ретл

- •37. Элемент эсл

- •38.Логический элемент ттлш(35. Транзисторно-транзисторная логика с барьером Шотки)

- •39. Логический элемент n-моп логики

- •40. Логический элемент p-моп логики

- •41. Логический элемент k-моп логики

- •42. Основные элементы

- •43. Простейшие коды (двоичный, двоично-десятичный, код с приоритетом)

- •44. Триггерная ячейка

- •45. Триггер с разделённым входом

- •46. Триггер со счётным входом

- •48. Синхронизируемые rs-триггеры

- •49. Двухтактные триггеры

39. Логический элемент n-моп логики

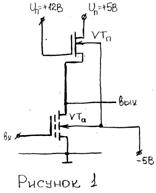

Помимо биполярных транзисторов для построения логических элементов применяются полевые транзисторы. Распространены логические элементы на МОП-транзисторах. n-МОП-транзисторы более быстродействующие, поэтому логические элементы на n-МОП транзисторах являются более распространенными. n-МОП транзисторы имеют две разновидности: активные – с индуцированным каналом; пассивные – со встроенным каналом. Элементы n-МОП имеют вид представленный на рисунке 1.

Т ранзистор

VTП – пассивный

транзистор, имеющий узкий длинный канал.

Транзистор VTA

– активный транзистор, имеет широкий

короткий канал. Сопротивление пассивного

транзистора на порядок выше, чем у

активного. В схеме используются несколько

источников питания: (-5 В) – для уменьшения

шумов схемы (удаление заряда в канале),

UП1 – задает режим

работы схемы, UП2 –

для смещения пассивного транзистора

VTП.

ранзистор

VTП – пассивный

транзистор, имеющий узкий длинный канал.

Транзистор VTA

– активный транзистор, имеет широкий

короткий канал. Сопротивление пассивного

транзистора на порядок выше, чем у

активного. В схеме используются несколько

источников питания: (-5 В) – для уменьшения

шумов схемы (удаление заряда в канале),

UП1 – задает режим

работы схемы, UП2 –

для смещения пассивного транзистора

VTП.

При подаче на вход логической единицы

на выходе получаем л огический

ноль.

огический

ноль.

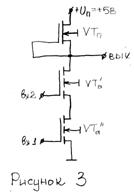

Реализация функции ИЛИ-НЕ в n-МОП-логике. Функция ИЛИ-НЕ осуществляется по схеме, представленной на рисунке 2. Два отдельных затвора VT1 и VT2 обладают большой емкостью, что хуже, однако при таком построении обеспечивается большее быстродействие. Если хотя бы на одном входе напряжение равно логической единице, то на выходе напряжение соответствующее логическому нулю. Если на входе логический ноль, то тока через VT1 и VT2 не будет и на выходе получим логическую единицу.

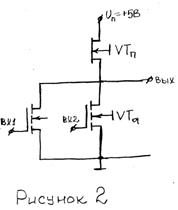

Реализация функции И-НЕ в n-МОП-логике. Функция И-НЕ осуществляется по схеме, представленной на рисунке 3. На кристалле вместо транзисторов VT1 и VT2 (схема элемента ИЛИ-НЕ) делают один транзистор, но с двумя затворами. На вход полевого транзистора можно подать до 200 В. Напряжение помехозащищенности по нулю при подключении еще одного входа уменьшается, поэтому необходимо увеличить крутизну канала VTП, еще больше по сравнению с первым входом. При большом количестве входов есть ограничение по быстродействию и нагрузочной способности.

40. Логический элемент p-моп логики

Логика на комплементарных МОП транзисторах (КМДП)

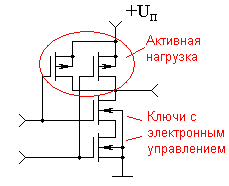

Схема логического элемента "И-НЕ" на КМОП микросхемах практически совпадает с упрощенной схемой "И" на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах приведена на рисунке 2.

Рисунок 2. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах.

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании низкого уровня схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать высокий потенциал, то транзисторы открываются, а если низкий - то закрываются.

В приведённой на рисунке 2 схеме ток от источника питания на выход микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме на рисунке 1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток микросхемой от источника питания потребляться не будет.