- •Содержание

- •Введение

- •1 Обоснование выбора элементной базы.

- •Структура мк51.

- •2 Структурная схема устройства. Описание функционирования устройства в целом.

- •3 Принципиальная схема устройства

- •Дешифраторы

- •Индикаторы.

- •Микроконтроллер.

- •4 Описание функционирования алгоритма программного обеспечения (по).

- •5 Оценка метрологических параметров приборов.

- •Заключение

- •Литература

2 Структурная схема устройства. Описание функционирования устройства в целом.

Упрощенная структурная схема измерителя периодов повторения импульсов представлена на рис. 3.

Рис. 3. Структурная схема устройства.

Согласно данной схеме периодически повторяющиеся импульсы (измеряемая величина) длительностью Tx подаются на входное устройство. В общем случае входное устройство может содержать узлы для масштабного преобразования входного сигнала, выделения его из помех и т. д.

Далее сигнал поступает на вход счетчика МП. По фронту импульса запускается счетчик, а по спаду счет прекращается.

В данной работе рассмотрим измеритель длительности импульсов, реализующий время-импульсный метод преобразования.

В измерителях данного вида измеряемая величина Тх преобразуется в цифровой код N. Таким образом эти измерители относятся к измерителям прямого преобразования.

Рис. 4. Временные диаграммы работы устройства:

а) входной сигнал; б) временная диаграмма подсчета импульсов.

В общем случае входное устройство может содержать узлы для масштабного преобразования входного сигнала, выделения его из помех и т. д. В МП осуществляется измерение длительности импульса. Значение, полученное в результате подсчета, через дешифраторы подается на индикаторы.

На входы одного из дешифраторов последовательно во времени поступают двоично-десятичные коды отображаемых цифр. Синхронно с их поступлением формируются управляющие сигналы идентификации знакоместа выводимого символа (на индикаторы подаются через другой дешифратор).

Измерение происходит примерно через каждые 0,5 с, яркость индикаторов и частота обновления достаточная, так что глаз человека не замечает мерцания.

3 Принципиальная схема устройства

Структурная схема устройства приведена в приложении 1.

Устройство основано на базе следующих микросхем: КР181ВЕ51, 564ИД1, 564ИД5. Далее рассмотрим их характеристики подробнее.

Дешифраторы

564ИД1

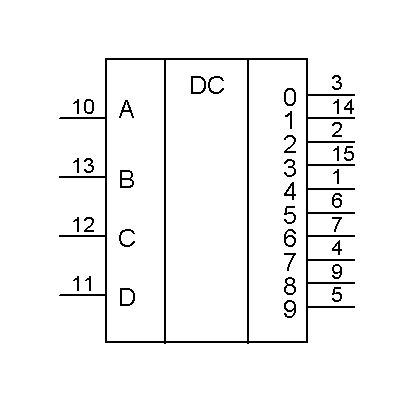

Рис. 6. Дешифратор 564ИД1, условное обозначение.

Данная микросхема является универсальным дешифратором. Она преобразовывает четырехразрядный двоичный код в десятичный. Она имеет четыре входа A..D, на которые подается двоичный код для дешифрации, и десять выходов 0..9. Выходной дешифрированный сигнал сохраняется до тех пор, пока на входах присутствует его двоичный код. Данный дешифратор принимает входной четырехразрядный код А…D и выдает напряжение низкого уровня по одному из десяти выходов Y0…Y9. На входы А…D поступают числа от 0 до 9 в двоичном коде, при этом открывается соответствующий выходной транзистор. Коды, эквивалентные числам от 10 до 15, дешифратор не отображает. Состояния дешифратора ИД1 показаны в таблице 2.

Табл.2.

входы |

Выходы с низким уровнем “0” |

|||

A |

B |

C |

D |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

1 |

3 |

0 |

1 |

0 |

0 |

4 |

0 |

1 |

0 |

1 |

5 |

0 |

1 |

1 |

0 |

6 |

0 |

1 |

1 |

1 |

7 |

1 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

1 |

9 |

1 |

0 |

1 |

0 |

Все выходы отключены |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

|

564ИД5

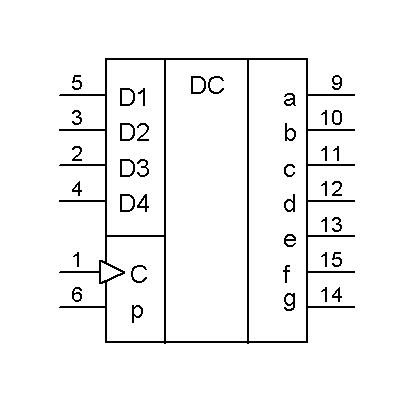

Рис. 7. Дешифратор 564ИД5, условное обозначение.

Микросхема 564ИД5 представляет собой дешифратор двоично-десятичного кода в код для управления семисегментными цифровыми индикаторами. Выходные усилители данной микросхемы позволяют выдавать на индикатор переменное напряжение с амплитудой, в 2 раза превышающей напряжение питания. Это необходимо для обеспечения достаточной яркости свечения индикаторов. Входной сигнал Р определяет выходной сигнал с инверсией (Р=1) и без нее (Р=0). В микросхеме присутствует входной регистр на основе однотактных D-триггеров, запись в которые осуществляется по сигналу С=1.

Данный дешифратор используется в работе для отображения численных значений проведенных измерений.