- •Глава 18. Микропроцессорные средства управления электроприводами

- •18.1. Состав и архитектура микропроцессорных систем

- •Структура однокристальных мп

- •Операционное устройство

- •18.2. Организация памяти микропроцессорных систем электропривода

- •18.2.1. Основные характеристики и классификации запоминающих устройств

- •18.2.2. Сверхоперативные и оперативные запоминающие устройства (созу и озу)

- •Статические эп способны хранить информацию (только один бит) как угодно долго, пока подается электропитание. В качестве такого эп используется статический триггер.

- •18.2.3. Постоянные запоминающие устройства

- •18.3. Организация ввода – вывода в микропроцессорных системах

- •18.4. Работа устройства управления мп

- •18.5. Особенности мп семейства х86

- •18.5.1. Процессоры 80186/80188 [3-8]

- •18.5.2. Процессор 80286

- •18.5.3. 32 – Разрядные процессоры

- •18.7. Микроконтроллеры с интегрированным сигнальным процессором mcs-296

- •Аналого-цифровые и цифро-аналоговые преобразователи

- •Аналого-цифровой преобразователь

- •Интегрирующий ацп

- •Аналого-цифровое преобразование с помощью мп

- •18.9. Принцип построения устройств измерения переменных состояний (координат) в электроприводах с микропроцессорным управлением

- •18.9.1. Устройства измерения перемещения (положения)

- •Средства измерения скорости

- •18.9.3. Измерение электрических величин

- •Глава 19. Программирование микропроцессорных систем

- •19.1. Форматы команд

18.4. Работа устройства управления мп

Н

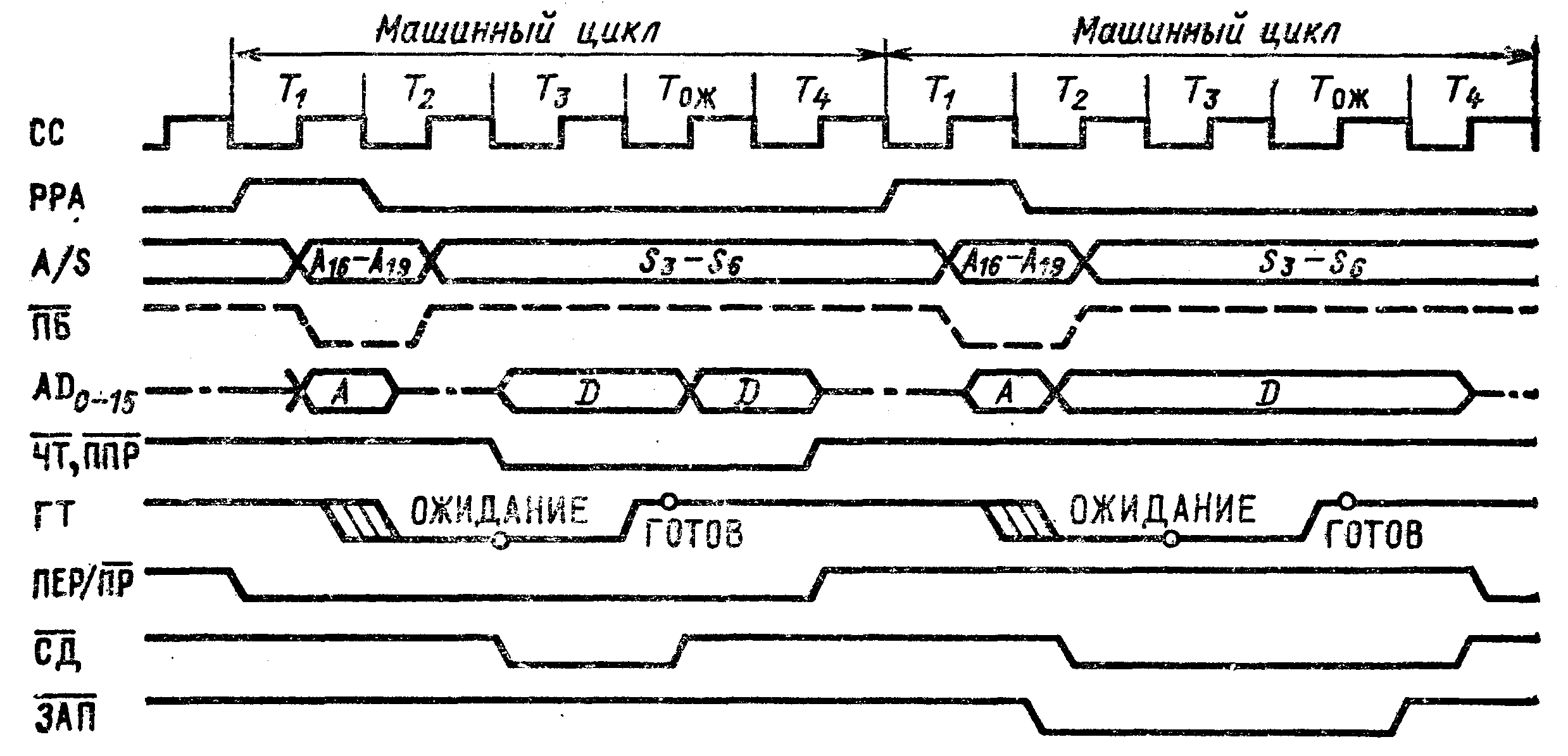

Рис.18.7. Временная

диаграмма работы МП

Каждый машинный цикл МП представляет собой цикл шины, так как МП а так же Т1, каждого МЦ выдаёт на линии AD0-19 код адреса памяти и формирует сигнал сопровождения и идентификации информации разрешения регистра адреса (РРА). По этому сигналу код адреса должен быть обязательно зафиксирован на внешнем регистре, так как в следующих тактах машинного цикла на шине осуществляется передача данных. Кроме того, в тактах Т2-Т4 по линиям А16-19 передаётся код состояния S3-6, который идентифицирует тип машинного цикла в минимальном режиме.

Одновременно

с передачей адреса по шине МП может

формировать сигнал передачи байта (![]() ),

который сопровождает передачу байта

данных по линиямAD8-15.

В такте Т1 по шине AD0-15

передаётся адрес, а в тактах Т2-Т4

принимается или передаётся двухбайтовое

слово. Стробирующий сигнал чтения (

),

который сопровождает передачу байта

данных по линиямAD8-15.

В такте Т1 по шине AD0-15

передаётся адрес, а в тактах Т2-Т4

принимается или передаётся двухбайтовое

слово. Стробирующий сигнал чтения (![]() )

используются для управления режимом

работы регистра данных памяти или УВВ.

В режиме прямого доступа к памяти линия

ЧТ переводится в высокоимпедансное

состояние. Стробирующий сигнал

подтверждения прерывания (

)

используются для управления режимом

работы регистра данных памяти или УВВ.

В режиме прямого доступа к памяти линия

ЧТ переводится в высокоимпедансное

состояние. Стробирующий сигнал

подтверждения прерывания (![]() )

используется для ввода в МП вектора

прерывания из котроллера УВВ, запросившего

прерывание. В режиме прямого доступа к

памяти линия

)

используется для ввода в МП вектора

прерывания из котроллера УВВ, запросившего

прерывание. В режиме прямого доступа к

памяти линия![]() переводится в высокоимпедансное

состояние.

переводится в высокоимпедансное

состояние.

Сигнал готов (ГТ) используется МП в качестве сигнала подтверждения окончания передачи данных из памяти или порта УВВ. Устройство управления МП опрашивает значение сигнала на линии ГТ в начале такта Т3 и в зависимости от него переходит или к состоянию Тож или к состоянию Т4.

Сигнал

обмена данными (ПЕР/![]() )

управляет работой шинных драйверов и

определяет направление передачи из МП

в память/УВВ или в МП из памяти/УВВ.

Управляющий сигнал стробирования данных

(

)

управляет работой шинных драйверов и

определяет направление передачи из МП

в память/УВВ или в МП из памяти/УВВ.

Управляющий сигнал стробирования данных

(![]() )

формируется в МП при обращении к памяти

и УВВ в тактах передачи данных по шине,

а так же машинном цикле подтверждения

прерывания. Сигнал запись (

)

формируется в МП при обращении к памяти

и УВВ в тактах передачи данных по шине,

а так же машинном цикле подтверждения

прерывания. Сигнал запись (![]() )

приобретает действующее нулевое значение

в циклах записи в память и вывода

информации в адресуемый порт УВВ.

)

приобретает действующее нулевое значение

в циклах записи в память и вывода

информации в адресуемый порт УВВ.

18.5. Особенности мп семейства х86

18.5.1. Процессоры 80186/80188 [3-8]

Процессоры i80186/80188 и их модификации 80С186/80С188 [18-3] не представляют нового поколения архитектуры: как и 8086/88, они являются процессорами с 16-разрядной внутренней архитектурой и программно совместимы с 8086. Разрядность шины адреса – 20бит, шины данных у 80186 – 16бит, у 80188 – 8бит. Эти процессоры имеют встроенные периферийные контроллеры прерываний, прямого доступа к памяти, трехканальный таймер и генератор синхронизации. Процессоры 80С186/88 имеют средства управления энергопотреблением, есть их модификации со встроенными последовательными портами и контроллерами регенерации динамической памяти.