Синтез КЛС

.pdf

Порядо выполнения работы

1.Составьте входн ю часть таблицы истинности для одноразрядных (варианы с 1 по 4) или дв хразрядных (варианты с 5 по 8) омпараторов.

2.Со ласно вариант проанализир йте выходные состояния и заполните их.

3.Минимизир йте равнения и переведите в базис «И-НЕ».

4.Составьте схем , обозначте ло ичес ие элементы со ласно ГОСТ, оцените энер озатраты для 155 серии ми росхем.

5.Промоделир йте составленн ю схем на омпьютере с помощью про раммных эм ляторов.

6.Соберите на стенде и проверьте работоспособность.

Контрольные вопросы

1.Представьте рафичес ое обозначение омпаратора с тремя выходами.

2.Представьте эпюры для описания работы омпаратора.

Лабораторная работа 5

Преобразователи одов

Преобразователь ода – это эле тронное стройство, предназначенное для перевода одной одовой омбинации (на входе стройства) в др ю (на выходе), в соответствии с заданной таблицей истинности.

X0

X1

X2

Z

Xn

Y0 |

|

X/Y |

X0 |

Y0 |

|

Y1 |

X1 |

Y1 |

Y2 |

X2 |

Y2 |

|

X3 |

Y3 |

|

X4 |

Y4 |

|

|

Y5 |

Ym |

|

Y6 |

à) |

á) |

Ðèñ. 3.

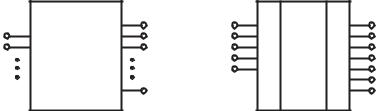

Графичес ое изображение преобразователя ода Хn в Ym приведено на рис н е 3а. Частичный сл чай преобразования ода «одной из 32» в од «один из 128» по азан на рис н е 3б.

В таблице 4 приведены наиболее распространенные стандартные

23

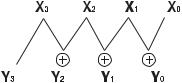

оды. Преобразование двоичных чисел в од Грея дости ается сложением по мод лю два по след ющем лючевом словию:

В ачестве пражнения заполните раф «Коды Грея» в таблице 4.

Десятичные |

Двоичные |

Двоично-десятичные коды |

код |

||||

|

|

|

|

||||

числа |

числа |

|

|

|

|

Грея |

|

8 4 2 1 |

с избытком 3 |

||||||

|

|

|

|||||

|

|

|

|

|

|

|

|

0 |

0000 |

|

0000 |

|

0011 |

|

|

|

|

|

|

|

|

|

|

1 |

0001 |

|

0001 |

|

0100 |

|

|

|

|

|

|

|

|

|

|

2 |

0010 |

|

0010 |

|

0101 |

|

|

|

|

|

|

|

|

|

|

3 |

0011 |

|

0011 |

|

0110 |

|

|

|

|

|

|

|

|

|

|

4 |

0100 |

|

0100 |

|

0111 |

|

|

|

|

|

|

|

|

|

|

5 |

0101 |

|

0101 |

|

1000 |

|

|

|

|

|

|

|

|

|

|

6 |

0110 |

|

0110 |

|

1001 |

|

|

|

|

|

|

|

|

|

|

7 |

0111 |

|

0111 |

|

1010 |

|

|

|

|

|

|

|

|

|

|

8 |

1000 |

|

1000 |

|

1011 |

|

|

|

|

|

|

|

|

|

|

9 |

1001 |

|

1001 |

|

1100 |

|

|

|

|

|

|

|

|

|

|

10 |

1010 |

0001 |

0000 |

0000 |

1101 |

|

|

|

|

|

|

|

|

|

|

11 |

1011 |

0001 |

0001 |

0000 |

1110 |

|

|

|

|

|

|

|

|

|

|

12 |

1100 |

0001 |

0010 |

0000 |

1111 |

|

|

|

|

|

|

|

|

|

|

13 |

1101 |

0001 |

0011 |

0001 |

0000 |

|

|

|

|

|

|

|

|

|

|

14 |

1110 |

0001 |

0100 |

0001 |

0001 |

|

|

|

|

|

|

|

|

|

|

15 |

1111 |

0001 |

0101 |

0001 |

0010 |

|

|

|

|

|

|

|

|

|

|

16 |

10000 |

0001 |

0110 |

0001 |

0011 |

|

|

|

|

|

|

|

|

|

|

17 |

10001 |

0001 |

0111 |

0001 |

0100 |

|

|

|

|

|

|

|

|

|

|

18 |

10010 |

0001 |

1000 |

0001 |

0101 |

|

|

|

|

|

|

|

|

|

|

19 |

10011 |

0001 |

1001 |

0001 |

0110 |

|

|

|

|

|

|

|

|

|

|

20 |

10100 |

0010 |

0000 |

0001 |

0111 |

|

|

|

|

|

|

|

|

||

|

|

Табл. 4. |

|

|

|

||

24

Цель работы

1. Составьте систем равнений, описывающих работ преобразователя ода со ласно ло ичес о о задания.

2. Синтезир йте преобразователь четырехразрядно о ода на стенде и на омпьютере.

Порядо выполнения работы

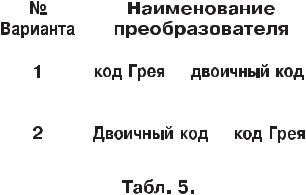

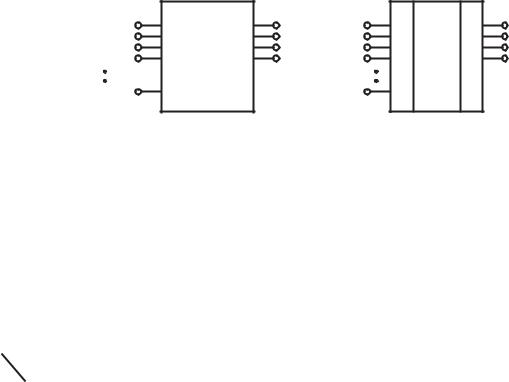

1. Заполните таблиц истинности 6 для Ваше о варианта преобразователя ода (табл. 5) при словии, что на стенде можно синтезировать стройства толь о на 4 входа и 4 выхода.

|

|

|

|

|

|

|

|

|

|

X0 |

X1 |

X2 |

X3 |

|

Y0 |

|

Y1 |

Y2 |

Y3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Òàáë. 6. |

|

|

|

|

||||

|

2. Составьте систем |

равнений по заполненной таблице |

||||||||||||||||||

истинности. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

3. Преобраз йте аждое |

равнение для синтеза на стенде, ис лю- |

||||||||||||||||||

чив операцию дизъюн ции. Для это о использ йте за он двойно о от-

рицания и за он де Мор ана. |

|

4. Составьте ло ичес ю схем |

Z- стройства по преобразован- |

ной системе равнений. |

|

5. Синтезир йте данн ю схем |

на стенде и на омпьютере. |

Контрольные вопросы

1.Методи а преобразования ло ичес о о равнения для возможности е о синтеза на стенде.

2.Ка ие преобразователи одов Вы знает?

3.Объясните принцип действия преобразователя двоично о ода

всемисе ментный од.

25

Лабораторная работа 6

Синтез двоично-десятично о шифратора

Шифратор – это эле тронное стройство, предназначенное для преобразования ода десятичных символов в двоичный од.

На вход данно о стройства Z пост пает 10 входящих шин, и толь- о на одной из них си нал соответств ет значению «1». На выходе Z – четыре шины Y0, Y1, Y2, Y3, соответств ющие четырем разрядам дво- ично-десятично о ода. На четырех выходах возможно возни новение 16 омбинаций двоичных чисел; но использ ется толь о 10, а это по азано в таблице 7.

X0 (0) |

|

X1 (1) |

|

X2 (2) |

Z |

X3 (3) |

|

X9 (9) |

|

Y0 (1) |

|

CD |

0 |

1 |

|

Y1 (2) |

1 |

2 |

Y2 (4) |

2 |

4 |

Y3 (8) |

3 |

8 |

|

9 |

|

Пос оль рассматривается од «один из 10» для одирования де-

сятичных цифр, то толь о одно значение Xi равно «1», |

де Xi – одно |

число из множества 0,1,2,…..,9. |

|

То да выходная ф н ция Y0 истинна, если десятичное число (Xi) |

|

равно 1,3,5,7 или 9. Отсюда можно записать систем |

равнений для |

определения пере лючательных ф н ций, полностью описывающих ра-

бот |

Z- |

стройства. |

|

|

|||||

|

|

|

|

|

|

|

Варианты про раммир емых |

||

X |

|

|

|

|

|

|

|||

Y3 |

Y2 |

|

Y1 |

Y0 |

лавиш шифраторов: |

||||

Y |

|

|

|

|

|||||

X0 |

0 |

|

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1. 1,2,3,4 |

2. |

2,3,4,5 |

X1 |

0 |

|

0 |

|

0 |

1 |

|||

|

|

|

|

|

|

|

3. 3,4,5,6 |

4. |

4,5,6,7 |

X2 |

0 |

|

0 |

|

1 |

0 |

|||

|

|

|

|

|

|

|

5. 5,6,7,8 |

6. |

6,7,8,9 |

X3 |

0 |

|

0 |

|

1 |

1 |

|||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

X4 |

0 |

|

1 |

|

0 |

0 |

Цель работы |

|

|

|

|

|

|

|

|

|

|

||

X5 |

0 |

|

1 |

|

0 |

1 |

|

||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

X6 |

0 |

|

1 |

|

1 |

0 |

1. Составьте систем |

равнений, описывающих |

|

|

|

|

|

|

|

|

|||

X7 |

0 |

|

1 |

|

1 |

1 |

|||

|

|

работ шифратора со ласно е о ло ичес о о задания. |

|||||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

2. Синтезир йте шифратор четырех линий на |

||

X8 |

1 |

|

0 |

|

0 |

0 |

|||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

стенде. |

|

|

X9 |

1 |

|

0 |

|

0 |

1 |

|

|

|

Òàáë. 7.

26

Порядо выполнения работы |

|

|

|

|

||||

1. Т. . на стенде имеется толь о 4 |

енератора вход- |

|

|

|

|

|||

Y |

Y2 |

Y1 |

Y0 |

|||||

ных переменных, составьте систем |

равнений для |

X |

|

|

|

|||

X0 |

0 |

0 |

0 |

|||||

шифратора четырех десятичных цифр в двоичный од. |

|

|||||||

|

|

|

|

|

||||

|

X1 |

0 |

0 |

1 |

||||

Таблица истинности та о о шифратора представлена в |

||||||||

|

|

|

|

|||||

|

|

|

|

|||||

таблице 8. |

|

|

|

X2 |

0 |

1 |

0 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|||

2. Преобраз йте аждое равнение для синтеза на |

X3 |

0 |

1 |

1 |

||||

стенде, ис лючив операцию дизъюн ции. Для это о ис- |

X4 |

1 |

0 |

0 |

||||

польз йте за он двойно о отрицания и за он де Мор ана. |

Òàáë. 8. |

|||||||

3. Составьте ло ичес ю схем |

Z- стройства по пре- |

|||||||

|

|

|

|

|||||

образованной системе равнений. |

|

|

|

|

|

|

|

|

4. Синтезир йте данн ю схем |

на стенде и на омпьютере. |

|

|

|||||

Контрольные вопросы

1.Методи а преобразования ло ичес о о равнения для возможности е о синтеза на стенде.

2.Где применяется стройство, имен емое шифратором?

3.Ка ие преобразователи одов Вы знаете?

Лабораторная работа 7

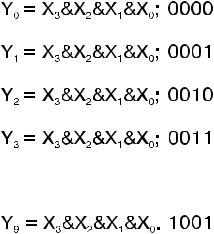

Синтез двоично-десятично о дешифратора

Дешифратор– это эле тронное стройство, предназначенное для реобразования двоично о ода в десятичный од.

|

|

Y0 (1) |

1 |

DC |

X0 (0) |

|

0 |

||

X1 (1) |

|

Y1 (2) |

2 |

1 |

X2 (2) |

Z |

Y2 (4) |

4 |

2 |

X3 (3) |

Y3 (8) |

8 |

3 |

|

|

|

Y9 (9) |

|

9 |

Ðèñ. 4.

На вход данно о стройства Z пост пает омбинация входных си - налов X0 – X3. Количество та их омбинаций равно 16, но использ ется толь о первые 10 (на рис н е 4 по азан дешифратор, преобраз ю- щий двоичный од в од «один из десяти»). Одной омбинации двоич-

27

ных входных си налов соответств ет одна и толь о одна выходная ф н- ция Y, соответств ющая десятичном представлению данно о двоично о ода.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X3 |

X2 |

X1 |

X0 |

|

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Òàáë. 9.

Варианты выходных си налов:

1. 1, 2, 3, 4 |

2. 2, 3, 4, 5 |

3. 3, 4, 5, 6 |

4. 4, 5, 6, 7 |

5. 5, 6, 7, 8 |

6. 6, 7, 8, 9 |

Цель работы

1.Составить систем равнений, описывающих работ дешифратора.

2.Синтезировать дешифратор 4 выходных ф н ций на стенде.

Порядо выполнения работы

1. На стенде имеется 4 инди атора выходных пере лючательных

ф н ций. Составьте схем |

равнений на 4 выхода. Преобраз йте аж- |

дое равнение, ис лючив операцию дизъюн ции. |

|

2. Составить ло ичес |

ю схем Z- стройства по данной системе |

равнений. |

|

3. Синтезир йте данн ю схем на стенде и на омпьютере.

Контрольные вопросы

1. Методи а преобразования ло ичес о о равнения для возможности е о синтеза на стенде.

28

2.Ка ие преобразователи одов Вы знаете?

3.Что та ое двоично-десятичный дешифратор?

4.Где применяется стройство, имен емое дешифратором?

Лабораторная работа 8

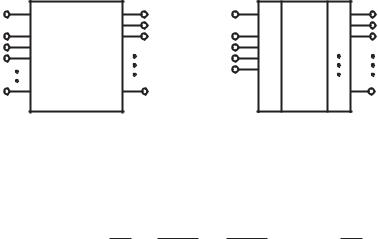

Синтез дем льтипле сора

Дем льтипле сор – это эле тронное стройство, предназначенное для преобразования последовательно о ода двоичных си налов

в параллельный. Др |

ими словами можно с азать, что м льтипле сор |

выполняет ф н ции |

стройства, под лючающе о одн входн ю шин |

любой из нес оль их выходных шин, в соответствии с заданной п- равляющей омбинацией.

X |

Y0 |

W |

DC 0 |

|

Y1 |

|

1 |

A0 |

Y2 |

1 |

2 |

A1 |

Z |

2 |

|

A2 |

4 |

|

|

|

|

8 |

|

Am |

Yn |

|

9 |

Количество правляющих шин m определяется оличеством выходных шин n: 2m=n.

Со ласно определению дем льтипле сора можно записать равнение для Y0:

Y0 = X & (Am & Am – 1 & Am – 2 & … & A0),

де |

омбинация |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

соответств ет двоичном |

|

Am, |

Am–1, |

Am–2 |

… A0 |

|||||||||||||||||

адрес — 000 … 0. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Для Y1: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Y1 = X & (Am & Am – 1 & Am – 2 & … & A0), |

|||||||||||||||||||

де |

омбинация |

|

|

|

|

|

|

|

соответств ет двоичном |

|||||||||||

Am, |

Am–1, |

Am–2 |

… A0 |

|||||||||||||||||

адрес — 000 … 1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И та |

далее… |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Можно заметить, что система равнений дем льтипле сора образована из системы равнений дешифратора п тем онъюн ции аждо о равнения с входным си налом Х.

29

Цель работы

1. Составить систем равнений для м льтипле сора на 4 входных линии.

2.Реализовать ло ичес ю схем со ласно записанным равнениям.

3.Синтезировать схем на стенде и на омпьютере.

Порядо выполнения работы

1. Та а n = 4, то оличество си налов правления m = 2. В ито е имеется трех анальная шина состоящяя из информационно о анала Х и 2 анала определяющие адрес под лючаемой выходной шины.

|

|

|

|

|

Y0 = X & (A1 |

& A0) |

||||

X |

|

|

|

Y0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

A0 |

|

|

|

Y1 |

Y1 |

= X & (A1 |

& A0) |

|||

|

|

|

||||||||

|

|

|

Y2 |

|||||||

|

|

|

||||||||

A1 |

|

Z |

|

Y3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y2 |

= X & (A1 |

& A0) |

|||

|

|

|

|

|

Y3 |

= X & (A1 |

& A0) |

|||

|

|

|

|

|

||||||

2. Преобраз йте систем |

равнений та им образом, чтобы синте- |

|||||||||

зировать ее на стенде.

3.Составьте схем , со ласно преобразованной системе.

4.Синтезир йте данн ю схем .

Контрольные вопросы

1.Методи а преобразования ло ичес о о равнения для возможности е о синтеза на стенде.

2.Ка ие преобразования одов Вы знаете?

3.Что та ое дем льтипле сор?

4.Для че о использ ется дем льтипле сор?

5.Составьте равнения и нарис йте схем дем льтипле сора на два информационных выхода.

30

Лабораторная работа 9

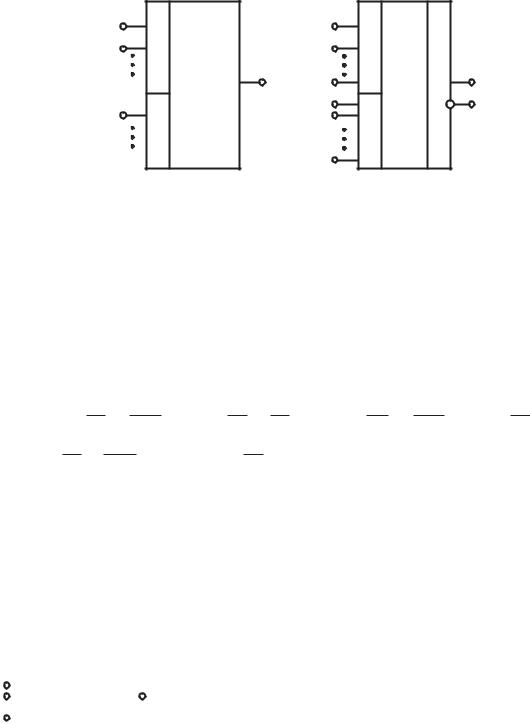

Синтез м льтипле сора

М льтипле сор – это эле тронное стройство, предназначенное для преобразования параллельных цифровых одов в последовательные.

X0

X1

X2

X3

Xn

A0

A1

Am

X0 MS

X0 MS

X1

Z  X2 X3

X2 X3

Y |

Xn |

Y |

|

|

_ |

|

A0 |

Y |

|

A1 |

|

|

Am |

|

Принцип передачи информации от нес оль их источни ов в один приемни или анал называется м льтипле сированием. Иными словами, м льтипле сор под лючает ло ичес и любой из нес оль их входных аналов единственном выход , причем адрес анала определяется двоичным одом на правляющих (адресных) входах.

Для то о, чтобы ос ществить ло ичес ое под лючение входа Xn выход Y, т.е. Y=Xn, необходимо, чтобы си нал входа (абонента) был онъю тивно связан с минтермом ода правления. Запишем равнение м льтипле сора.

Y = X0 & (Am & Am-1 & … & A1 & A0) v X1 & (Am & Am-1 & … & A1 & A0) + + X2 & (Am & Am-1 & … & A1 & A0) + … + Xn & (Am & Am-1 & … & A1 & A0).

|

|

|

|

|

|

Цель работы |

|

1. |

Составить таблиц |

истинности для MS на два абонента. |

|||||

2. |

Составить равнение для 2-входово о м льтипле сора. |

||||||

3. |

Составить ло ичес |

ю схем стройства. |

|||||

4. |

Реализовать данн ю схем на стенде и на омпьютере. |

||||||

X0 |

|

|

|

|

|

Порядо |

выполнения работы |

|

|

|

|

|

|||

|

|

|

|

||||

X1 |

|

|

Z |

|

Y |

1. Пос оль |

оличество информационных |

|

|

||||||

A0 |

|

|

|

||||

|

|

|

|

входов n = 2, значить оличество адресных вхо- |

|||

|

|

|

|

|

|||

|

|

|

|

|

дов m = 1 (2 m=n), смотри рис но . То да рав- |

||

|

|

|

|

|

|

|

|

31

нение м льтипле сора принимает след ющий вид:

Y = X0 & A0 v X1 & A0

2. Преобраз йте данное равнение, ис лючив операцию дизъюн ции.

3. Составить схем по пол ченном равнению.

4. Синтезировать данн ю схем на стенде и на омпьютере.

Контрольные вопросы

1.Методи а преобразования ло ичес о о равнения для возможности е о синтеза на стенде.

2.Ка ие преобразователи одов Вы знаете?

3.Что та ое м льтипле сор?

4.Для че о использ ется м льтипле сор?

5.Составьте равнения и нарис йте схем м льтипле сора на 2 информационных входа.

Лабораторная работа 10

Синтез одноразрядно о двоично о полно о

смматора

Смматор – это эле тронное стройство, предназначенное для арифметичес о о сложения дв х двоичных чисел. Например, сложим 2 числа:

Из примера видно, что при сложении входных переменных A и B, в рам ах данно о разряда необходимо читывать си нал переноса P из младше о разряда. В рез льтате сложения пол чаем две ф н ции S и P, де S – рез льтат с ммирования в данном разряде, а P – перенос, если он возни ает, в след ющий старший разряд.

32