Синтез КЛС

.pdf

Упражнение 1. Пол с мматоры.

Пол с мматор обеспечивает операцию сложения дв х одноразрядных чисел. П сть за младшие разряды дв х сла аемых отвечают переменные А и В. На рис н е по азано словное обозначение пол - с мматора и е о таблица истинности.

A

B

|

|

|

|

|

|

|

A |

B |

|

S |

P |

|

|

|

|

|

|

|

|

|

|

||

HS |

|

S |

|

|

0 |

0 |

|

|

|

||

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

0 |

1 |

|

|

|

||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||

|

|

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

|

|

1 |

1 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Из рис н а видно, что необходимо синтезировать систем из дв х равнений.

Порядо выполнения работы

1.Занесите в тетрадь для лабораторных работ таблиц истинности пол с мматора.

2.Запишите равнения выходных ф н ций: S – си нал с ммы; Р – си нал переноса в старший разряд.

3. Использ йте пол ченн ю систем равнений для синтеза принципиальной схемы:

а) использ йте минимальное оличество известных Вам

фн циональных ло ичес их элементов;

б) преобраз йте равнения ф н ции S и P для их реализации на элементах Шеффера.

4. Реализ йте схем на «УЦС-1» и на омпьютере.

Упражнение 2. Полный с мматор.

|

|

|

|

|

|

В полном с мматоре реализовано сложение |

Ai |

|

SM |

|

S |

|

|

|

|

|

дв х одноразрядных двоичных чисел Аi, Вi и си - |

|||

Bi |

|

|

|

P |

|

|

|

|

|

|

нала переноса из предыд ще о (младше о) |

||

|

|

|

||||

Pi-1 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

разряда Pi-1. |

|

|

|

|

|

|

|

|

Систем |

полно о с мматора можно реализовать из дв х пол с м- |

||||

маторов. |

|

|

|

|

||

Ai

Bi

Pi-1

HS |

S |

|

|

HS |

S |

|

|

||||

|

P |

|

|

|

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

Si |

1 |

Pi |

|

33

Порядо выполнения работы

1. Воспольз йтесь рез льтатами пражнения 1 и реализ йте на стенде схем полно о с мматора из дв х пол с мматоров.

2. Составьте и заполните таблиц истинности полно о с мматора.

Pi-1 |

Ai |

Bi |

|

Si |

Pi |

|

Pi-1 |

Ai |

Bi |

|

Si |

Pi |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.Воспольз йтесь для составления системы равнений операцией, реализ емой элементом Шеффера.

4.Реализ йте схем полно о с мматора на стенде и на омпьютере.

Контрольные вопросы

1.Методи а преобразования ло ичес о о равнения для возможности е о синтеза на стенде.

2.Правила сложения двоичных чисел.

3.Ка ие действия выполняет оператор «сложение по мод лю два»?

4.Ка ими способами можно реализовать стройства для вычитания двоичных чисел?

Задания для самостоятельной под отов и

1.Синтезир йте вычитатель двоичных чисел.

2.Промоделир йте работоспособность стройства на омпьютере с помощью про рммных эм ляторов.

2.Анализ и синтез последовательных схем

Синтез последовательных схем (ПС) подраз мевает про раммирование на физичес ом ровне элементов памяти (пол автоматов) и на их основе злы и стройства.

Значение y=Q элемента памяти в те щий момент времени t считается «вн тренним состоянием». Рез льтат пере лючения элемента памяти в новое состояние зависит от последовательности подачи входных си налов с четом «вн тренне о состояния» y = f (Q, X).

34

Для сравнения отметим, что в КЛС единственное «вн треннее состояние», в ПС – их не оторое множество.

Частные решения создания автоматов элементов памяти:

–мод ли ПЗУ;

–три еры-пол автоматы с дв мя стойчивыми состояниями.

Цифровые автоматы – синтезир ются на базе три еров.

В настоящем разделе синтезир ем все возможные три еры и неоторые цифровые автоматы: ре истры и цифровые счетчи и имп льсов.

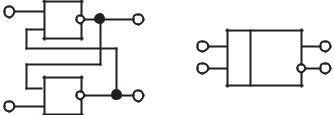

Простейший пол автомат реализ ется из «три ерно о ольца» - подачей си нала с выхода цепи из дв х последовательно соедененных инверторов на вход (рис. 5).

ОБРАТНАЯ СВЯЗЬ

Ðèñ. 5.

При в лючении питания на выходе DD1.1 си нал можно присвоить «вн треннее состояние» Q, а на выходе DD1.2 соответственно Q (рис. 6). «Три ерное ольцо» является базовым злом для про- е тирования любо о автомата, оторые различают на автоматы М ра

(выход однозначно определяется «вн тренним сотоянием») и Мили (выход зависит не толь о от «вн тренне о состояния», но и входно-

оси нала). Автоматы М ра можно преобразовать в автомат Мили

инаоборот [8].

Формализованное описание « онечных автоматов» ( онечный - предс аз емый, про раммир емый) инвариантно реализ ется с помощью:

–таблиц истинности, переходов;

–направленных рафов;

–эпюр;

–ал ебраичес их равнений переходов.

Синтез автоматов памяти в лючает след ющие этапы:

1.Техничес ое задание;

2.Формализованное описание;

3.Минимизация ал ебраичес ой ф н ции возб ждения;

4. Переход заданном элементном базис , запись равнения

в операторной форме; |

|

|

5. Составление схемы три |

ера (от выхода |

о вход ): |

– начинаем с выходно о |

зла – три ерно о ольца; |

|

– обозначаем на выходах Q и Q, далее по |

равнению. |

|

35

6.Анализ пол ченной схемы по след ющим призна ам:

– выделение бло а памяти;

– выделение бло а автомати и и правления.

7.Анализ развития ф н циональных возможностей.

8.Моделирование схемы на омпьютере с помощью про раммных эм ляторов.

9.Сбор а на стенде и провер а автомата.

Лабораторная работа 11

Из чение RS-три еров

Три ер – это эле тронное стройство, имеющее 2 стойчивых состояния, в аждое из оторых оно переходит под воздействием внешне о эле тронно о имп льса (или имп льсов). Trigger (ан л.) – сп с о- вой рючо ( ро ).

С помощью омбинационных схем можно выполнить сложные операции, одна о для более сложной обработ и данных необходимо запомнить промеж точный рез льтат. При цифровой обработ е данные представляются омбинацией н лей и единиц, следовательно, необходимо запомнить два состояния: 0 и 1. Схема, составленная из дв х последовательно соединенных инверторов с обратной связью,

представляет собой элементарн ю ячей |

памяти (рис. 5). |

Эт схем принято изображать «три |

ерным ольцом», а дополни- |

тельные входы «S» и «R» позволяют записать и сбросить информацию, тем приблизить зел онечном пол автомат (рис. 6).

|

|

DD1.1 |

S |

& |

Q |

|

|

|

|

& |

_ |

|

Q |

|

|

|

|

R |

|

|

|

|

DD1.2 |

Ðèñ. 6.

S |

T |

Q |

|

|

_ |

R |

|

Q |

36

Асинхронный RS-три ер с прямыми входами

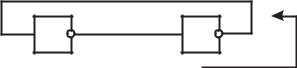

Работа асинхронно о RS-три ера, а автомата с памятью (автомат М ра), хара териз ется таблицей состояний

(табл. 10).

(Rt) – сброс, (St) – вход, (Qt) –

вн треннее состояние три ера (е о вых.) на та т t. (Qt+1) – вн реннее состояние три ера, соответств ющее выходной

ф н ции.

На входы RS-три ера запрещено одновременно подавать «1» (Rt = St = 1). Если точнить значение прямо о выходно о

си нала Qt+1, то возможно про раммирование на физичес ом ровне трех модифи аций: S-три ера, R-три ера, E-три ера.

Упражнение 1. Синтез S-три ера.

При Rt = St =1, Qt+1 =1

Упражнение 2. Синтез R-три ера.

В таблице истинности R-три |

ера Rt = St =1, Qt+1 = 0 |

Упражнение 3. Синтез Е-три ера. |

|

В таблице истинности Е-три |

ера Rt = St = 1, Qt+1 = Qt |

Порядо выполнения пражнений

1.Перенесите таблиц истинности в тетрадь для лабораторных работ и заполните ее.

2.Использ йте таблиц состояний для нахождения ф н ций переходов, доопределив ее стро ами запрещающих состояний (наборы 3 и 7). В арте Карно лет и, соответств ющие запрещенным наборам, доопределите в соответствие с пражнением.

3. Запишите минимальные б левы равнения S, R или Е-три еров

вобщем базисе.

4.Изобразите схем RS-три ер на элементах Шеффера (от вы-

ходно о три ерно о ольца |

о вход ): |

а) реализ йте схем |

RS-три ера с прямыми входами на ни- |

версальном стенде; |

|

37

б) проверьте правильность работы автомата в соответствии с таблице 10 рассмотрев все возможные переходы Q(t) —> Q(t+1).

Упражнение 4. Синтез RCS-три ера.

Синхронный RСS-три ер ф н ционир ет, а RS-три ер, при с- ловии С=1. При отс тствии синхронизир ющих имп льсов состояние е о сохраняется неизменным.

Порядо выполнения пражнения |

1.Перенесите таблиц состояний в тетрадь для лабораторных работ и заполните ее.

2.Заполните арт Карно, доопределив ф н цию переходов еди-

ницами на запрещенных наборах (синхронный S-три ер).

3. |

Пол чите стр т рн ю форм л синхронно о RS-три ера. |

4. |

Синтезир йте схем три ера на базовых элементах. |

5.Синтезир йте схем три ера на элементах Шеффера (примените двойное отрицание и теорем де Мор ана).

6.Реализ йте схем синхронно о RS-три ера на ниверсальном стенде. Проверьте правильность работы автомата в соответствии с

ео таблицей истинности.

7. Синтезир йте схем три ера на элементах Пирса.

8. Синтезир йте дв хта тный RCS-три ернаэлементахШеффера. 9. Реализ йте схем дв хта тно о RCS-три ера на ниверсаль-

ном стенде и на омпьютере.

Контрольные вопросы

1. Методи а составления схемы три ера.

2.В чем отличие синхронно о и асинхронно о три еров и их с- ловных обозначений?

3.Ка реализовать RS-три ер на элементах Пирса?

38

Лабораторная работа 12

Из чение D- и Т-три еров

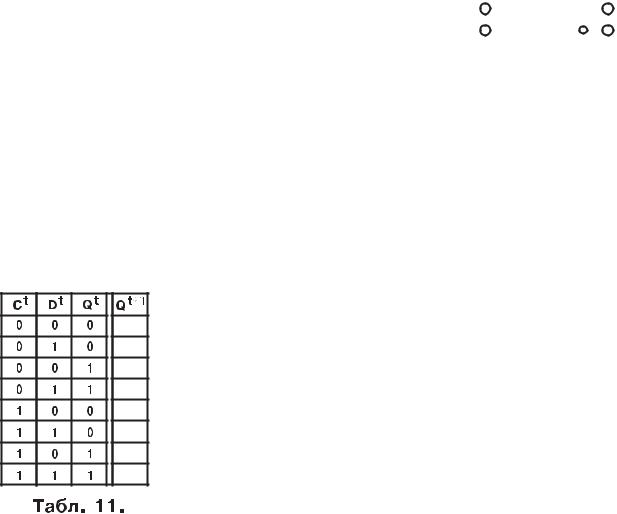

Упражнение 1. Однота тный D-три ер.

«Однота тный D-три ер» – «ло ичес ая задерж а» – от delay.

Цель пражнения

1. |

Из чить принцип действия и синтез D-три ера. |

|

|

|

|

|

|

2. |

Из чить эпюры си налов и состояний. |

|

|

|

|

|

|

На выходе три ера Q информация меняется в |

|

|

|

|

|

||

D |

|

T |

|

Q |

|||

|

|

|

|

|

|||

соответствии с состоянием на информационном |

|

||||||

C |

|

|

_ |

||||

|

|

|

|

|

|

Q |

|

входе D, т.е. Qt+1=Dt (три ер «отслеживает» вход- |

|

|

|||||

|

|

|

|

|

|||

н ю информацию). А при подаче на синхровход «С» |

|

|

|

|

|

||

ло ичес о о 0 на входе Q остаются та информация, т.е. три |

ер «за- |

||||||

щел н лся», и изменение состояния на D-входе не влияет на состояние на Q-выходе.

Порядо |

выполнения пражнения |

|

|

1. Заполните таблиц |

истинности (табл. 11) и арт Карно. |

|

|

2. Инженерном решению схемы D-три ера отвечает не мини- |

|||

мальное б лево равнение, использ ется дополнительная р ппа. |

|

||

3. Уравнение D-три |

ера из ДНФ переведите в |

||

базис элементов Шеффера, использ йте в записи |

|||

штрих Шеффера. |

|

|

|

4. Нарис йте схем |

D-три ера, начиная с три - |

||

ерно о ольца. |

|

|

|

5. Минимизир йте схем D-три ера, ис лючив |

|||

инвертор на входе и до азав возможность вместо |

|||

D подать на вход си нал (DIC). |

|

||

6. Выполните сбор |

схемы на стенде и |

бе- |

|

дитесь в правильности работы «ло очес ой |

|||

задерж и». |

|

|

|

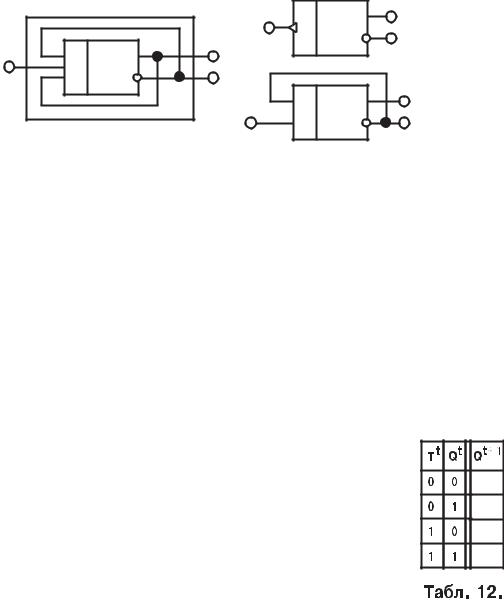

Упражнение 2. Т-три ер. |

|

|

|

Т-три ер – «делитель на два», выходной си нал имеет частот в |

|||

два раза меньше, чем на входе. |

|

|

|

Принцип работы Т-три ера за лючается в пере лючении е о вы- |

|||

|

|

|

39 |

хода Q в противоположное состояние под воздействием фронта входно о имп льса. Этот три ер строится:

1. на базе дв хта тно о RCS-три ера; 2. на базе D-три ера.

TT

T

|

S |

TT |

Q |

Q |

|

|

|||

“T” |

C |

|

|

_ |

|

R |

|

_ |

Q |

|

|

|

Q |

|

D T

C

C

Цель пражнения

Q

_

Q

Q

_

Q

1. Из чить принцип действия Т-три ера. На читься строить диа - раммы входно о напряжения и выходно о состояния пол автоматов.

2. На читься собирать схемы на стенде и моделировать на омпьютере.

3. До азать возможность применения RCS и D-три ера для реализации Т-три ера.

Порядо выполнения пражнения

В таблице 12 представлены входные си налы и вн тренние состояния однота тно о Т-три ера.

1. Соберите схем Т-три ера на стенде и на омпьютере.

2.Заполните значения выходных ф н ций в таблице состояний.

3.Использ я таблиц состояний, составьте равне-

ние Т-три ера.

4. До ажите применения RCS и D-три еров для реализации Т-три ера, сравнивая равнения выходных ф н ций в общем базисе.

Контрольные вопросы

1.Методи а составления схемы три ера и ло ичес о о равнения для возможности е о синтеза на стенде.

2.В чем отличие синхронно о и асинхронно о три еров и их с- ловных обозначений ?

3.В чем отличие одно- и дв хта тных три еров ?

4.Принцип работы Т-три ера.

40

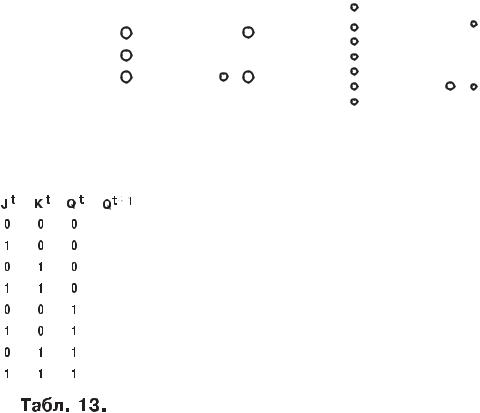

Лабораторная работа 13

Из чение JK-три ера

Отдельным |

лассом от RS-три |

еров (при полном сходстве) |

|||

выделены JK-три |

еры. Вход S заменен на J, вход сброса R на K (б - |

||||

вы выбраны авторами а |

соседние в алфавите). Входы J и K отвечают |

||||

здесь, соответственно за « станов |

» и «считывание». |

||||

Отличие таблицы JK от RS-три |

ера в той же стро е для входных |

||||

си налов J = K = 1, Qt+1 = Qt. |

|

|

|

||

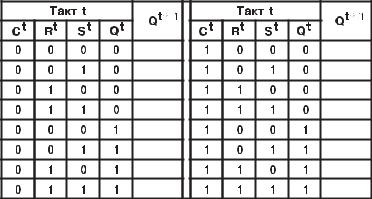

На схемах JK-три еры изображают та , |

а на рис н е 7а. В ни- |

||||

версальных JK-три ерах |

роме стандартных входов применяют допол- |

||||

нительные S, R , входы &, |

онъю тивно связанные с J и K (рис. 7б). |

||||

В та ом варианте JK-три ер называют |

ниверсальным. Приве- |

||||

дем схемы взаимно о преобразования три |

еров (рис. 8). |

||||

Синтезир ем схем JK-три ера: |

|

|

|||

а) преобразованием из RСS-три |

ера (рис. 9); |

||||

б) преобразованием из RS-три |

ера (рис. 10). |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

TT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

J |

|

Q |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

J |

|

|

Q |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

_ |

|

|

C |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

K |

|

|

|

Q |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a) |

|

|

|

|

|

á) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ðèñ. 7. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Порядо выполнения работы |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

1. Выполните сбор |

схемы JK-три ера (рис. 9) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

настенде. |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

2. Заполните таблиц |

истинности (табл. 13) э - |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

сперементально и сравните с RS. |

||||||||||||||

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

3. Использ йте арт |

|

арно для записи б лева |

||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

равнения, дополните е о выражением Q V |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

Q. |

|||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

4. Синтезир йте схем |

JK-три ера, изобра- |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

женн ю на рис н е 10. |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

Контрольные вопросы |

||||||||||||

|

1. Чем JK-три ер отличается от RS-три |

ера? |

||||||||||||||||||||

2. Возможности взаимозаменяемости JK-три еров.

41

|

D - триггер |

|

|

Т - триггер |

|

D |

J T |

Q |

D |

J T |

Q |

C |

C |

|

C |

C |

|

|

|

_ |

|

|

_ |

|

K |

Q |

|

K |

Q |

Ðèñ. 8.

J |

& |

S |

T |

|

|||

C |

|

C |

|

K |

& |

R |

|

|

|

|

Ðèñ. 9.

Q

Q

_

Q

& |

|

|

J |

|

T |

|

S |

|

|

|

|

C |

|

|

& |

R |

|

K |

|

|

Ðèñ. 10.

Q

Q

_

Q

|

Лабораторная работа 14 |

|

Ре истры |

Ре истры – |

стройства автомати и для записи, хранения и сдви а |

цифровой информации. |

|

Число три |

еров определяет число двоичных разрядов в «слове». |

Упражнение 1. Синтез дв хразрядно о ре истра.

Синтезировать дв хразрядный параллельный ре истр в базисе элементов Шеффера. Управление входом С (разрешить С = 1), правление выходом С1 (разрешить С1 = 1) на инди аторы в прямом и С2 в обратном оде.

42