- •Технические средства информатизации

- •Глава 1

- •Технологии электронных схем

- •Общее устройство пк

- •Процессоры (основные принципы и классы)

- •Процессоры Intel

- •Itanium (архитектура ia-64)

- •Процессоры других производителей

- •Набор микросхем системной платы (чипсет)

- •Глава 2

- •Организация оперативной памяти

- •Конкретные системы памяти

- •Реализация систем основной памяти

- •Интерфейсы пк. Внутренние интерфейсы

- •Интерфейсы периферийных устройств

- •Внешние интерфейсы

- •Интерфейсы центральных процессоров

- •Спецификации pc 98, pc 99, pc 2001

- •Глава 3

- •Магнитные накопители. Ленты (мл)

- •Накопители на магнитных дисках (мд)

- •Технологии сменных носителей

- •Носители dvd

- •Альтернативные и перспективные накопители

- •Глава 4

- •Терминалы. Клавиатуры

- •Мониторы на основе элт

- •Плоскопанельные мониторы

- •Видеоадаптеры и интерфейсы мониторов

- •Манипуляторы и сенсорные экраны

- •Глава 5

- •Принтеры

- •Сканеры

- •Плоттеры

- •5.4. Дигитайзеры

- •Глава 6

- •Цифровое видео

- •Сжатие видеоинформации

- •Обработка аудиоинформации

- •Принципы и элементы проекторов мультимедиа

- •Глава 7

- •Каналы передачи и телекоммуникация

- •Цифровые и мобильные системы связи

- •Компьютерные сети

- •Мобильные компьютеры и gps

Конкретные системы памяти

Для повышения быстродействия применяются различные архитектурно-логические решения, известно множество различных типов памяти, отличающихся друг от друга своими основными характеристиками.

Основная память соединяется с процессором через адресную шину и шину данных. Каждая шина состоит из множества электрических цепей или бит. Ширина (разрядность) адресной шины определяет, сколько адресов может быть в ОЗУ (адресное пространство), а шины данных сколько данных может быть передано за 1 цикл. Например, в 1985 г. процессор Intel 386 имел 32-разрядную адресную шину, что дает возможность поддерживать адресное пространство в 4 Гбайт. В процессоре Pentium (1993 г.) ширина шины данных была увеличена до 64 бит, что позволило передавать 8 байт информации одновременно.

Каждая передача данных между процессором и памятью называется циклом шины. Количество бит, которое процессор может передать за один цикл шины, влияет на производительность компьютера и определяет, какой тип памяти требуется.

Рассмотрим вкратце основные типы систем памяти (более подробные сведения приводятся, например, в [16]).

Динамическая память

Динамическая память (DRAM) используется обычно в качестве оперативной памяти общего назначения, а также как память для видеоадаптера. Из применяемых в современных и перспективных ПК типов динамической памяти наиболее известны DRAM и FPM DRAM, EDO DRAM и BEDO DRAM, EDRAM и CDRAM, Synchronous DRAM, DDR SDRAM и SLDRAM, видеопамять MDRAM, VRAM, WRAM и SGRAM, RDRAM и некоторые другие.

Микросхема памяти этого типа представляет собой прямоугольный массив ячеек со вспомогательными логическими схемами, которые используются для чтения или записи данных, а также цепей регенерации, поддерживающих целостность данных. Массивы памяти организованы в строки (raw) и столбцы (column) ячеек памяти, именуемые соответственно линиями слов (wordlines) и линиями бит (bitlines). Каждая ячейка памяти имеет уникальное размещение, задаваемое пересечением строки и столбца. Цепи, поддерживающие работу памяти, включают:

усилители, считывающие сигнал из ячейки памяти;

схемы адресации для выбора строк и столбцов;

схемы выбора адреса строки (row adress select /RAS) и столбца (column adress select /CAS), чтобы открывать и закрывать адреса строк и столбцов, а также начинать и заканчивать операции чтения и записи;

цепи записи и чтения информации;

внутренние счетчики или регистры, следящие за циклами регенерации данных;

схемы разрешения выхода (Output enable ОЕ).

Каждый бит такой памяти представляется в виде наличия (или отсутствия) заряда на конденсаторе, образованном в структуре полупроводникового кристалла. Конденсатор управляет транзистором. Если транзистор открыт и ток идет, это соответствует «1», если закрыт «0». С течением времени конденсатор разряжается, и его заряд нужно периодически восстанавливать. Между периодами доступа к памяти посылается электрический ток, обновляющий заряд на конденсаторах для поддержания целостности данных (вот почему данный тип памяти называется динамическим ОЗУ). Этот процесс называется регенерацией памяти.

Интервал регенерации измеряется в наносекундах (нс), и это число отражает «скорость» ОЗУ. Большинство ПК на основе процессоров Pentium характеризуются скоростью 60 или 70 нс. Процесс регенерации снижает скорость доступа к данным, поэтому доступ к DRAM обычно осуществляется через кэш-память. Однако когда быстродействие процессоров превысило 200 МГц, кэширование перестало существенно влиять на присущую DRAM низкую скорость и возникла необходимость использования других технологий ОЗУ.

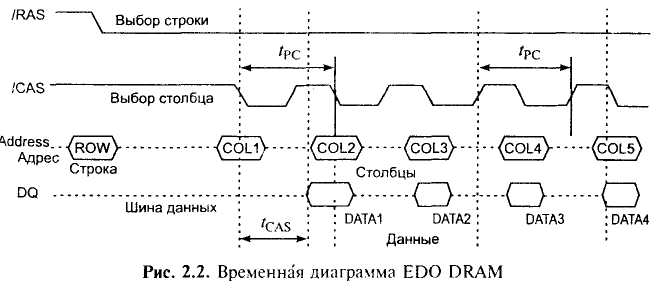

Цикл чтения включает следующие события (см. рис. 2.15, для EDO DRAM):

выбор строки. Активизация цепи /RAS используется для связывания со строкой памяти и инициации цикла памяти;

выбор столбца. Сигнал /CAS используется для связывания со столбцом памяти и инициации операции записи-чтения;

разрешение записи (Write enable /WE);

разрешение вывода (Output enable /ОЕ). Во время операций чтения из памяти этот сигнал предотвращает преждевременное появление данных;

ввод-вывод данных. Выводы DQ на чипе памяти предназначены для ввода и вывода. Во время операции записи высокое («1») или низкое («0») напряжение подается на DQ. При чтении данные считываются из выбранной ячейки и передаются на DQ, если доступ осуществлен и /ОЕ открыт.

Охарактеризуем вкратце системы динамической оперативной памяти.

FPM DRAM (Fast page mode DRAM) представляет собой стандартный тип памяти, быстродействие которой составляет 60 или 70 нс. Система управления памятью в процессе считывания активирует адреса строк, столбцов, осуществляет проверку данных и передачу информации в систему. Столбцы после этого деактивируются, что приводит к нежелательному состоянию ожидания процессора в некоторых сочетаниях операций с памятью. В наилучшем случае данный режим реализует временную схему пакета вида 5-3-3-3.

EDO RAM (RAM с расширенным выходом). Обращение на чтение осуществляется таким же образом, как и в FPM, за исключением того, что высокий уровень /CAS не сбрасывает выходные данные, а использование триггера позволяет сохранять данные то тех пор, пока уровень CAS снова не станет низким. Тем самым не происходит сброса адреса столбцов перед началом следующей операции с памятью.

Упрощенная схема работы EDO показана на рис. 2.2. Выходная величина поддерживается последовательностью стробирующих импульсов до тех пор, пока она не будет считана ЦП. Эта память обеспечивает лучшие параметры для серии быстрых последовательных считываний, чем FPM RAM. Теоретически скорость памяти на 27% выше, чем для FMP DRAM.

BEDO RAM (Burst extended data out DRAM Пакетная с расширенным выходом), как это видно из названия, читает данные в виде пакета, что означает, что после получения адреса каждая из следующих трех единиц информации читается за один цикл таймера, а ЦП считывает данные в виде пакета 5-1-1-1. Быстродействие системы на 100% превосходит FPM и на 50% EDO DRAM.

SDRAM (Synchronous DRAM Синхронная динамическая память). Этот тип памяти существенно отличается от других тем, что использует тот факт, что большинство обращений к памяти является последовательным и спроектировано так, чтобы передать все биты пакета данных как можно быстрее (когда начинается передача пакета, все последующие биты поступают с интервалом 10 нс).

Как видно из названия, эта память обеспечивает синхронизацию всех входных и выходных сигналов с системным таймером. Наибольшая скорость SDRAM в циклах ЦП это 5-1-1-1 для пакета чтения четырех единиц информации (байт/слово/двойное слово), что делает ее такой же быстродействующей, как и BEDO RAM; однако самое большое достоинство SDRAM то, что она легко поддерживает частоту шины до 100 МГц.

SDRAM PC100. Для материнских плат, поддерживающих внешние частоты 100 МГц и выше, необходима память (SDRAM), которая сможет нормально и без сбоев работать с такими частотами, обеспечивая оптимальную скорость. Такие модули памяти должны иметь время доступа не более 8 нс, но самого быстродействия как такового недостаточно. Память, способная устойчиво работать на внешних частотах 100 МГц и выше, должна удовлетворять специальному стандарту PC 100.

SDRAM PC133 память, соответствующая стандарту РС133. Спецификация PC 133 SDRAM DIMM разработана группой компаний VIA Technologies, IBM Microelectronics, Micron Semiconductor Products, NEC Electronics, Samsung Semiconductor (Revision 0.4, 7 июня 1999 г.). Память PC 133 это лучшие образцы памяти стандарта РС100, «разогнанные» до 133 МГц.

Пиковая пропускная способность РС133 SDRAM приблизительно равна 1 Гб/с и средняя пропускная способность около 250 Мбайт/с, что соответствует пропускной способности AGP 4-х (1 Гбайт/с пиковая и 200 Мбайт/с средняя).

DDR SDRAM (SDRAM II). В системах с синхронизацией данные обычно передаются по фронту импульса синхронизации (clock tick). Так как сигнал генератора импульсов изменяется между «1» и «0», данные могут передаваться или по переднему фронту импульса (изменение с «0» на «1»), или по заднему (с «1» на «0»).

Компанией Samsung предложена система DDR (Double Data Rate) SDRAM или SDRAM II, в которой передача данных осуществляется по обоим фронтам тактовых импульсов одновременно, этим достигается удвоение скорости передачи при той же тактовой частоте. Кроме того, DDR использует DLL (delay-locked loop цикл с фиксированной задержкой) для выдачи сигнала DataStrobe, означающего доступность данных на выходных контактах.

DDR II SDRAM. К числу основных отличий технологии DDR-II от предыдущего варианта (DDR-I) относится то, что в ней размер выборки данных увеличен вдвое с 2 до 4 бит, а значит, во столько же раз возрастает скорость передачи. Память DDR-II отличается от DDR-I более низким напряжением питания 1,8 вместо 2,5 В.

SLDRAM (Synchronous linked DRAM). Этот тип устройств разработан консорциумом крупнейших производителей модулей памяти SLDRAM Consortium. Считается, что применение SLDRAM экономически выгодно при объеме ОЗУ не менее 256 Мбайт. Повышение производительности достигается за счет распространения пакетного протокола передачи данных на сигналы управления (отсюда название этого типа памяти Linked SDRAM). В SLDRAM адреса, команды, а также сигналы управления передаются в пакетном режиме по однонаправленной шине Command Link.

Одновременно с ними по другой, двунаправленной шине Data Link, и тоже в пакетном режиме, передаются данные, причем передача происходит на обоих фронтах тактовых импульсов, как и в случае с DDR SDRAM. Максимальная достижимая скорость передачи SLDRAM превышает 1 Гбайт/с на каждый разряд при частоте 400 МГц.

ESDRAM (Enhanced SDRAM улучшенная SDRAM) более быстрая версия SDRAM, соответствующая стандарту JEDEC компании Enhanced Memory Systems (EMS). С точки зрения времени доступа производительность ESDRAM в 2 раза выше по отношению к стандартной SDRAM.

Основные отличия от SDRAM:

более быстрое время доступа (27 нс вместо стандартных 60 нс);

производительность, повышенная почти до уровня статического ОЗУ;

кэш-память, связанная с каждым банком памяти;

скрытая регенерация;

гибкое использование кэш-памяти для обеспечения максимальной производительности при различных типах обращений.

CDRAM (Cached DRAM DRAM с кэш-памятью). Этот тип ОЗУ разработан в корпорации Mitsubishi и представляет собой улучшенный вариант ESDRAM. Изменения коснулись кэш-памяти ее объема, принципа размещения данных, средств доступа. Cached DRAM имеет раздельные адресные линии для статического кэша и динамического ядра. Необходимость управлять разнородными типами памяти усложняет контроллер, однако эффективность кэш-памяти, размещенной внутри микросхемы, выше, чем при традиционной архитектуре ПК, так как перенос в кэш осуществляется блоками, в 8 раз большими, чем при выдаче из микросхемы обычной DRAM.

Direct Rambus (DRDRAM). Одной из наиболее быстродействующих является память RDRAM (Rambus DRAM), разработанная компанией Rambus (США) и выпускаемая такими компаниями, как NEC, Toshiba и Fujitsu. Память RDRAM является 9-разрядной, тактируется частотой 250 МГц и достигает пиковой скорости передачи данных 500 Мбайт/с.

Подсистема памяти Rambus состоит из следующих компонентов: основной контроллер (RMC Rambus Memory Controller), канал (RC Rambus Channel), разъем для модулей (RRC Rambus RIMM Connector), модуль памяти (R1MM Rambus In-line Memory Module), генератор дифференциальных импульсов (DRCG Direct Rambus Clock Generator) и сами микросхемы памяти (RDRAM Rambus DRAM).

VCM (Virtual Channel Memory) разработанная NEC и Siemens технология, позволяющая оптимизировать доступ к оперативной памяти нескольких процессов (запись данных центральным процессором, перенос содержимого оперативной памяти на жесткий диск, обращения графического процессора и т. п.) таким образом, что переключение между процессами не приводит к падению производительности. В отличие от традиционной схемы, когда все процессы делят одну и ту же шину ввода-вывода, в технологии VCM каждый из них использует виртуальную шину. Организованное на уровне чипа взаимодействие виртуальных шин и реальной шины позволяет достичь прироста производительности системы до 25%.

Чтобы при одновременном обращении к памяти нескольких процессов не снизилась производительность, число каналов доведено до 16 по 1024 бита каждый (в модулях по 256 Мбайт каждый канал может передавать до 2048 бит). Работает VC SDRAM при частоте до 143 МГц. Тип корпуса стандартный, совместимый по контактам и набору команд с SDRAM.

Active Link разработка NEC, которая нагружает DRAM новыми функциями архивация (сжатие информации) в основной памяти. Чтобы не загружать рутинной работой процессор, функция компрессии/декомпрессии возлагается на сам чип DRAM. В результате несколько расширилось обрамление кристалла, но налицо двойной выигрыш нужна меньшая по количеству ячеек микросхема DRAM, и доступ к информации происходит быстрее, чем обычно.

IRAM (Intellectual Random Access Memory). Главная идея IRAM в размещении процессора и DRAM в одном чипе. Это дает возможность чтения и записи данных длинными словами (от 128 до 16 384 бит), обеспечивая повышение пропускной способности памяти. Раньше это было невозможно все упиралось в неприемлемо большое число выводов микросхемы. Средняя скорость RAS/CAS равна приблизительно 1030 нс для модулей 64256 Мбайт IRAM.

При этом снижается энергопотребление и уменьшается площадь, занимаемая микросхемами памяти.

Магнитная оперативная память. Надо заметить, что первые образцы ОЗУ были выполнены на кольцевых магнитных ферритовых сердечниках, нанизанных на адресные и информационные шины (провода). Емкость таких ЗУ не превосходила 64 Кбайт. В последующем длительный период времени устройства ОЗУ выполнялись на кремниевых полупроводниковых элементах.

В 2000 г. IBM и Infineon Technologies AG (ФРГ) объявили программу разработки MRAM (Magnetic Random Access Memory). Принцип организации элементов памяти магнитная среда, заключенная между слоями металла.

Преимущества технологии высокая емкость, скорость, низкая стоимость, возможность применения как в форме статической, так и динамической памяти, более низкое энергопотребление.

Статическая память

Статическая память (SRAM) обычно применяется в качестве кэш-памяти второго уровня для кэширования основного объема ОЗУ. Статическая память выполняется обычно на основе ТТЛ-, КМОП- или БиКМОП-микросхем и по способу доступа к данным может быть как асинхронной, так и синхронной. Асинхронным называется доступ к данным, который можно осуществлять в произвольный момент времени. Асинхронная SRAM применялась на материнских платах для третьего пятого поколений процессоров. Время доступа к ячейкам такой памяти составляло от 15 (33 МГц) до 8 не (66 МГц).

Синхронная память обеспечивает доступ к данным не в произвольные моменты времени, а синхронно с тактовыми импульсами. В промежутках между ними память может готовить для доступа следующую порцию данных. В большинстве материнских плат пятого поколения используется разновидность синхронной памяти пакетно-конвейерная SRAM (Pipelined Burst SRAM), для которой типичное время одиночной операции чтения/записи составляет 3 такта, а групповая операция занимает 3-1-1-1 такта при первом обращении и 1-1-1-1 при последующих обращениях, что обеспечивает ускорение доступа более чем на 25%.

Async SRAM (Асинхронная статическая память). Это кэш-память, которая используется в течение многих лет с тех пор, как появился первый 386-й компьютер с кэш-памятью второго уровня. Обращение к ней производится быстрее, чем к DRAM, и могут в зависимости от скорости ЦП использоваться варианты с доступом за 20, 15 или 10 нс (чем меньше время обращения к данным, тем быстрее память и тем короче может быть пакетный доступ к ней). Тем не менее, как видно из названия, эта память является недостаточно быстрой для синхронного доступа, что означает, что для обращения ЦП все-таки требуется ожидание, хотя и меньшее, чем при использовании DRAM.

SyncBurst SRAM (Синхронная пакетная статическая память). При частотах шины, не превышающих 66 МГц, синхронная пакетная SRAM является наиболее быстрой из существующих видов памяти. Причина этого в том, что, если ЦП работает на не слишком большой частоте, синхронная пакетная SRAM может обеспечить полностью синхронную выдачу данных, что означает отсутствие задержки при пакетном чтении ЦП 2-1-1-1. Когда частота ЦП становится больше 66 МГц, синхронная пакетная SRAM не справляется с нагрузкой и выдает данные пакетами по 3-2-2-2, что существенно медленнее, чем при использовании конвейерной пакетной SRAM. К недостаткам относится и то, что синхронная пакетная SRAM производится меньшим числом компаний и поэтому стоит дороже. Синхронная пакетная SRAM имеет время адрес/данные от 8,5 до 12 нс.

РВ SRAM (Конвейерная пакетная статическая память). Конвейер распараллеливание операций SRAM с использованием входных и выходных регистров. Заполнение регистров требует дополнительного начального цикла, но, будучи заполненными, регистры обеспечивают быстрый переход к следующему адресу за то время, пока по текущему адресу считываются данные.

Благодаря этому такая память является наиболее быстрой кэш-памятью для систем с производительностью шины более 5 МГц. РВ SRAM может работать при частоте шины до 133 МГц. Она, кроме того, работает не намного медленнее, чем синхронная пакетная SRAM при использовании в медленных системах: она выдает данные пакетами по 3-1-1-1 все время. Время адрес/данные составляет от 4,5 до 8 нс.

1-Т SRAM. Традиционные конструкции SRAM используют для запоминания одного разряда (ячейки) статический триггер. Для реализации одной такой схемы на плате должно быть размещено от четырех до шести транзисторов (4-Т, 6-Т SRAM). Фирма Monolithic System Technology (MoSys) объявила о создании нового типа памяти, в которой каждый разряд реализован на одном транзисторе (1-Т SRAM). Фактически здесь применяется технология DRAM, поскольку приходится осуществлять периодическую регенерацию памяти. Однако интерфейс с памятью выполнен в стандарте SRAM, при этом циклы регенерации скрыты от контроллера памяти. Схемы 1-Т позволяют снизить размер кремниевого кристалла на 5080% по сравнению с аналогичными для SRAM, а потребление электроэнергии на 75%.

Системы видеопамяти

Известны следующие типы видеопамяти (табл. 2.1, здесь отражены также некоторые из вышеперечисленных универсальных систем памяти).

Таблица 2. 1. Характеристики систем видеопамяти

Параметр |

Тип |

|||||

|

EDO |

VRAM |

WRAM |

SDRAM |

SGRAM |

RDRAM |

Максимальная производительность, Мбайт/с |

400 |

400 |

960 |

800 |

800 |

600 |

Двух- или однопортовые |

1 |

2 |

2 |

1 |

1 |

1 |

Типичная ширина данных |

64 |

64 |

64 |

64 |

64 |

8 |

Типичная скорость, нс |

50-60 |

50-60 |

50-60 |

10-15 |

8-10 |

330 МГц тактовая частота |

VRAM (Video RAM видеоОЗУ) так называемая двухпортовая DRAM. Этот тип памяти обеспечивает доступ к данным со стороны сразу двух устройств, т. е. есть возможность одновременно писать данные в какую-либо ячейку памяти и одновременно с этим читать данные из какой-нибудь соседней ячейки. За счет этого позволяет совмещать во времени вывод изображения на экран и его обработку в видеопамяти, что сокращает задержки при доступе и увеличивает скорость работы.

WRAM (Window RAM) вариант VRAM, с увеличенной на ~25% пропускной способностью и поддержкой некоторых часто применяемых функций, таких как отображение шрифтов, перемещение блоков изображения и т. п.

SGRAM (Synchronous Graphics RAM синхронное графическое ОЗУ) вариант DRAM с синхронным доступом. В принципе, работа SGRAM полностью аналогична SDRAM, но дополнительно поддерживаются еще некоторые специфические функции типа блоковой и масочной записи. В отличие от VRAM и WRAM, SGRAM является однопортовой, однако может открывать две страницы памяти как одну, эмулируя двухпортовость других типов видеопамяти.

MDRAM (Multibank DRAM многобанковое ОЗУ) вариант DRAM, разработанный фирмой MoSys, организованный в виде множества независимых банков объемом по 32 Кбайт каждый, работающих в конвейерном режиме, и использующий распараллеливание операций доступа к данным между большим количеством банков памяти.