- •К.А. Палагута Микропроцессоры и интерфейсные средства транспортных средств

- •Москва 2011

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия 11

- •Глава 2 Режимы работы мпс 33

- •Глава 3. Реализация и организация памяти мп 57

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080) 77

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086) 138

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4 159

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus 209

- •Глава 8. Понятие и задачи интерфейса 239

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus 255

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле 308

- •Глава 11. Интегральные схемы программируемой логики (ис пл) 326

- •Предисловие

- •Введение

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия

- •1.1 Определение микропроцессора, классификация мп

- •1.2 Микропроцессорный комплект (мпк)

- •1.3 Микропроцессорная система

- •1.4 Линия, шина, магистраль

- •1.5 Типы магистралей

- •1.6 Шина адреса, раздельные и объединенные адресные пространства памяти и устройств ввода-вывода

- •1.7 Шина данных

- •1.8 Шина управления

- •1.9 Архитектура и структура микропроцессора

- •1.10 Cisc и risc процессоры, конвейерное выполнение команд программы

- •1.11 Конвейерная обработка данных

- •1.12 Контрольные вопросы и задания

- •Глава 2 Режимы работы мпс

- •2.1 Режим обмена данными под управлением процессора

- •2.2 Режим пдп

- •2.3 Режим прерывания

- •2.4 Контрольные вопросы и задания

- •Глава 3. Реализация и организация памяти мп

- •3.1. Виды запоминающих устройств (зу)

- •3.2. Кэш-память

- •3.3. Когерентность, механизмы сквозной и обратной записи

- •3.4. Алгоритмы обновления содержимого заполненных строк, снуппинг

- •3.5. Организация памяти

- •3.6. Внешние зу

- •3.7. Контрольные вопросы и задания

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080)

- •4.1 Структура мп к580вм80

- •4.2 Основные технические характеристики мп кр580вм80а

- •4.3 Регистровая модель мп к580вм80

- •4.4 Классификация команд мп кр580вм80а

- •4.5 Команды пересылки (перемещения) данных

- •4.5.1 Пересылка из регистра в регистр

- •4.5.2 Непосредственная пересылка

- •4.5.3 Непосредственная загрузка пары регистров

- •4.5.4 Запоминание/загрузка аккумулятора и пары hl

- •4.5.5 Ввод из пары регистров в стек

- •4.5.6 Ввод а и f в стек

- •4.5.7 Выбор из стека пары регистров

- •4.5.8 Выбор (a) и (f) из стека

- •4.5.9 Обмен данными

- •4.5.10 Пересылка нl

- •4.6 Приращение / отрицательное приращение

- •4.6.1 Приращение/отрицательное приращение регистра

- •4.6.2 Приращение пары регистров

- •4.6.3 Отрицательное приращение пары регистров

- •4.7 Арифметические и логические операции

- •4.7.1 Арифметические операции над (a) и (r)

- •4.7.2 Арифметические операции с непосредственной адресацией

- •4.7.3 Сложение содержимого пар регистров

- •4.7.4 Логические операции над (а) и (r)

- •0800) Ora c

- •4.7.5 Логические операции с непосредственной адресацией

- •4.7.6 Операции сравнения

- •4.7.7 Операции циклического сдвига (а).

- •4.7.8 Дополнение аккумулятора

- •4.8 Команды перехода и вызова подпрограмм

- •4.8.1 Команды переходов

- •4.8.2 Команды вызова подпрограмм и возврата из подпрограмм

- •4.9 Команды ввода – вывода

- •4.9.1 Ввод данных из входного порта

- •4.9.2 Вывод данных в выходной порт

- •4.10 Команды управления

- •4.10.1 Рестарт (повторный запуск)

- •4.10.2 Изменение (Тс)

- •0800) Stc

- •0800) Cmc

- •4.10.3 Управление прерываниями

- •4.10.4 Двоично-десятичная коррекция

- •4.10.5 Пустая операция

- •4.10.6 Останов

- •4.11 Микропроцессор intel8085

- •4.11.1 Архитектура мп intel8085

- •4.11.2 Регистры мп Intel 8085

- •4.11.3 Ввод и вывод последовательных данных

- •4.12 Контрольные вопросы и задания

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086)

- •5.1. Устройство и работа микропроцессора Intel 8086 (k1810bm86)

- •5.1.1. Структура микропроцессора Intel 8086

- •5.1.2. Режимы работы микропроцессора

- •5.1.3. Структура минимально укомплектованной системы на базе микропроцессора к1810вм86

- •5.1.4. Структура системы средней сложности на базе микропроцессора к1810вм86

- •5.2. Программная модель микропроцессора Intel 8086

- •5.2.1. Пользовательские регистры

- •5.2.2. Регистры общего назначения

- •5.2.3. Сегментные регистры

- •5.2.4. Регистры состояния и управления

- •5.3. Формирование физического адреса в микропроцессоре Intel 8086

- •5.4 Способы адресации микропроцессора

- •5.5 Контрольные вопросы и задания

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4

- •6.1. Архитектура микропроцессоров 80186/80188

- •6.2. Микропроцессор 80286

- •6.2.1 Аппаратные особенности

- •6.2.2 Система команд

- •6.2.3. Виртуальная память

- •6.3. Микропроцессоры 80386 и 80486

- •6.3.1. Микропроцессор 80386

- •6.4. Микропроцессоры Pentium и Pentium Pro

- •6.5. Специальные регистры микропроцессора Pentium

- •6.6. Управление памятью микропроцессора Pentium

- •6.7. Новые команды микропроцессора Pentium

- •6.8. Специальные особенности микропроцессора Pentium Pro

- •6.9. Микропроцессоры Pentium II, Pentium III и Pentium 4

- •6.9.1. Сопряжение с памятью

- •6.9.2. Набор регистров

- •6.11 Контрольные вопросы и задания

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus

- •7.1 Микропроцессор к1801вм1

- •7.1.1 Структурная схема микропроцессора к1801вм1

- •7.1.2 Основные технические характеристики

- •7.1.3 Регистровая модель микропроцессора

- •7.1.4 Адресное пространство

- •7.1.5 Формат команд

- •7.1.6 Методы адресации

- •7.2. Системная магистраль q-Bus

- •7.2.1 Временная диаграмма цикла ввод

- •7.2 2 Временная диаграмма цикла вывод

- •7.2.3 Цикл ввод-пауза-вывод

- •7.2.4 Временная диаграмма предоставления прямого доступа к памяти

- •7.2.5 Временная диаграмма прерывания

- •7.3 Контрольные вопросы и задания

- •Глава 8. Понятие и задачи интерфейса

- •8.1 Интерфейс

- •8.2 Селекция магистралей

- •8.2.1 Схемы централизованной селекции

- •8.2.2 Схемы децентрализованной селекции

- •8.3 Синхронизация обмена по магистрали

- •8.4 Координация взаимодействия устройств на магистрали

- •8.5 Контрольные вопросы и задания

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus

- •9.1 Isa

- •9.2. Порядок обмена по системной магистрали isa

- •9.2.1. Особенности магистрали isa

- •9.2.2. Сигналы магистрали isa

- •9.2.3. Циклы магистрали isa

- •9.3 Разработка устройств сопряжения для isa

- •9.3.1. Проектирование аппаратуры для сопряжения с isa

- •9.4 Разработка устройств сопряжения для q-bus

- •9.5 Контрольные вопросы и задания

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле

- •10.1 Промышленные Fieldbus (полевые) сети

- •10.1.1 Модель osi (Open System Interconnection) (iso/osi) для стандартов.

- •10.1.2 Локальная сеть на основе интерфейса rs-485, объединяющая несколько приемо-передатчиков.

- •10.2 Этапы развития fieldbus технологий

- •10.3 Сетевые протоколы в автомобиле

- •10.4 Контрольные вопросы и задания

- •Глава 11. Интегральные схемы программируемой логики (ис пл)

- •11.1. Классификация ис программируемой логики

- •11.2. Конструктивно-технологические типы современных программируемых элементов

- •11.3. Области применения микросхем с программируемой логикой

- •11.4 Системные свойства ис пл

- •11.5 Типовые схемотехнические решения

- •11.6 Приемы дополнительной обработки сигнала

- •11.7 Организация двунаправленных выводов

- •11.8 Схема программирования типа выхода ячейки (введение триггера)

- •11.9 Fpga (программируемые пользователем вентильные матрицы)

- •11.10. Полные ресурсы межсоединений в микросхемах cpld

- •11.11 Контрольные вопросы и задания

- •Заключение

- •Глоссарий

- •Список литературы

6.2.1 Аппаратные особенности

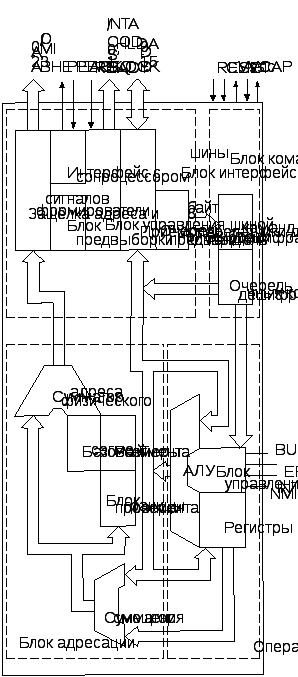

На рис. 6.2 приведена блок-схема микропроцессора 80286. Она, в отличие от микропроцессоров 80186/80188, не содержит в себе встроенных контроллеров. Вместо них он содержит блок управления памятью, иначе MMU (Memory-Management Unit), который на блок-схеме назван блоком адресации (address unit). Ознакомление с блок-схемой показывает, что адресные выводы А23—А0, а также выводы BUSY , CAP, ERROR , PEREQ и РЕАСК являются новыми, или добавленными, выводами, которых нет в микропроцессоре 8086.

Сигналы BUSY , ERROR , PEREQ и РЕАСК используются при работе с сопроцессором, примером которого является 80287. Аналогичный вывод TEST процессора 8088/8086 в процессоре 80286 называется BUSY. Шина адреса разрядностью 24 бита позволяет адресовать 16 Мбайт физической памяти. Вывод САР соединяется с конденсатором емкостью 0,047 мкФ +20% с рабочим напряжением 12 В, который в свою очередь подключают к нулевому потенциалу. Конденсатор необходим для работы внутреннего делителя частоты. Для сравнения на рис. 6.3 приведены условные схемы обозначения микропроцессоров 8086 и 80286. Следует заметить, что микропроцессор 80286 не имеет мультиплексированной шины адреса/данных.

Микропроцессор 80286 работает в реальном и защищенном режимах. В реальном режиме работы микропроцессор 80286, используя только 16-разрядную шину адреса, адресует лишь 1 Мбайт памяти и, в сущности, является идентичным с микропроцессором 8086. В защищенном режиме работы микропроцессор 80286, используя все 24 разряда, адресует уже 16 Мбайт физической памяти.

В состав микропроцессора 80286, кроме регистра EFLAGS, добавлены еще регистр слова состояния машины (MSW), регистр задачи (TR), регистры таблиц дескрипторов (GDTR, IDTR, LDTR) и 6 регистров расширения сегментных регистров.

|

|

|

Рис. 6.2 Блок-схема микропроцессора 80286

|

|

|

|

Рис. 6.3. Схемы обозначения микропроцессоров 8086 и 80286

|

6.2.2 Система команд

Система команд микропроцессора 80286 включает все команды процессоров 8086/8088 и имеет ряд дополнительных команд. Дополнительные команды управляют системой виртуальной памяти с помощью блока управления памятью микропроцессора 80286. В табл. 6.1 перечислены все эти команды с комментариями относительно назначения каждой из них. Здесь приведены только дополнительно добавленные в микропроцессоре 80286 команды. Кроме них система команд микропроцессора 80286 содержит новые, добавленные еще и для микропроцессоров 80186/80188 команды, такие как: INS, OUTS, BOUND, ENTER, LEAVE, PUSHA, POPA, а также команды целочисленного умножения на константу и команды сдвигов, включая циклические, с указанием счетчика в константе.

Таблица 6.1.

Дополнительные команды микропроцессора 80286

|

Команда |

Назначение |

|

CLTS |

Сбрасывает бит флага переключения задач |

|

LGDT |

Загружает из памяти регистр глобальной таблицы дескрипторов |

|

SGDT |

Сохраняет в памяти содержимое регистра глобальной таблицы дескрипторов |

|

LIDT |

Загружает из памяти регистр таблицы дескрипторов прерываний |

|

SIDT |

Сохраняет в памяти содержимое регистра таблицы дескрипторов прерываний |

|

LLDT |

Загружает из регистра или памяти регистр локальной таблицы дескрипторов |

|

SLOT |

Сохраняет в регистре или в памяти содержимое регистра локальной таблицы дескрипторов |

|

LMSW |

Загружает регистр состояния машины (MSW) |

|

SMSW |

Сохраняет содержимое регистра состояния машины |

|

LAR |

Загружает права доступа дескриптора |

|

LSL |

Загружает граничное значение сегмента |

|

STR |

Сохранение содержимого регистра задачи |

|

LTR |

Загружает регистр задачи |

|

ARPL |

Приводит уровень привилегии к наибольшему значению |

|

VERR |

Проверяет сегмент на возможность считывания |

|

VERW |

Проверяет сегмент на возможность записи |

Ниже следует описание некоторых специальных команд, которые используются для управления защитой.

□ CLTS

Команда CLTS (clear task-switched flag) сбрасывает бит флага переключения задач TS (task-switched) в регистре состояния машины MSW (machine state word). Если флаг TS установлен и следующая команда, относящаяся к сопроцессору 80287, вызовет прерывание (тип вектора 7). Это позволяет программно определить, относится ли контекст сопроцессора к текущей задаче. Команда clts используется в системе и считается привилегированной командой, поскольку она может выполняться только в защищенном режиме с нулевым уровнем привилегий. Команды для установки флага TS не существует. Однако установить флаг можно при помощи записи логической единицы в бит 3 (TS) регистра состояния машины MSW с использованием команды lmsw.

□ LAR

Команда LAR (load access rights) считывает дескриптор сегмента и размещает копию байта прав доступа в 16-разрядный регистр. Примером является команда LAR ах, вх, которая загружает регистр АХ байтом прав доступа из выбранного дескриптора по значению селектора, указанного в регистре ВХ. Команда используется для получения прав доступа, чтобы она могла быть проверена перед программным использованием сегмента памяти, описанного дескриптором.

□ LSL

Команда LSL (load segment limit) загружает в выделенный для пользователя регистр граничное значение сегмента. Например, команда LSL ах, вх загружает в регистр АХ граничное значение сегмента, описываемое дескриптором, который выбирается селектором, указанным в регистре ВХ. Эта команда используется для проверки граничного значения сегмента.

□ ARPL

Команда ARPL (adjust requested privilege level) используется для проверки селектора, чтобы уровень привилегий запрашиваемого селектора не нарушался. Примером является команда ARPL ах, CX. Регистр АХ содержит запрашиваемый уровень привилегий, а СХ содержит значения селектора вызывающего процесса для доступа к дескриптору. Если запрашиваемый уровень привилегий имеет приоритет ниже, чем у проверяемого дескриптора, то устанавливается флаг нуля ZF. Использование команды гарантирует, что параметр-селектор в подпрограмме не запросит большего уровня привилегированности, чем ему позволит вызывающий процесс.

□ VERR

Команда VERR (verify for read access) проверяет сегмент на возможность считывания. Это означает, что сегмент кода может иметь защиту от несанкционированного чтения. Если считывание из сегмента кода разрешено, то устанавливается флаг нуля ZF, если же не разрешено, то флаг будет сброшен. Команда VERR ах проверяет дескриптор, выбираемый с помощью регистра АХ.

□ VERW

Команда VERW (verify for write access) проверяет сегмент на возможность записи. Сегмент кода может иметь защиту от несанкционированной записи. Если запись в сегмент кода разрешена, то устанавливается флаг нуля ZF, если же не разрешена, то флаг будет сброшен.