- •К.А. Палагута Микропроцессоры и интерфейсные средства транспортных средств

- •Москва 2011

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия 11

- •Глава 2 Режимы работы мпс 33

- •Глава 3. Реализация и организация памяти мп 57

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080) 77

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086) 138

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4 159

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus 209

- •Глава 8. Понятие и задачи интерфейса 239

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus 255

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле 308

- •Глава 11. Интегральные схемы программируемой логики (ис пл) 326

- •Предисловие

- •Введение

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия

- •1.1 Определение микропроцессора, классификация мп

- •1.2 Микропроцессорный комплект (мпк)

- •1.3 Микропроцессорная система

- •1.4 Линия, шина, магистраль

- •1.5 Типы магистралей

- •1.6 Шина адреса, раздельные и объединенные адресные пространства памяти и устройств ввода-вывода

- •1.7 Шина данных

- •1.8 Шина управления

- •1.9 Архитектура и структура микропроцессора

- •1.10 Cisc и risc процессоры, конвейерное выполнение команд программы

- •1.11 Конвейерная обработка данных

- •1.12 Контрольные вопросы и задания

- •Глава 2 Режимы работы мпс

- •2.1 Режим обмена данными под управлением процессора

- •2.2 Режим пдп

- •2.3 Режим прерывания

- •2.4 Контрольные вопросы и задания

- •Глава 3. Реализация и организация памяти мп

- •3.1. Виды запоминающих устройств (зу)

- •3.2. Кэш-память

- •3.3. Когерентность, механизмы сквозной и обратной записи

- •3.4. Алгоритмы обновления содержимого заполненных строк, снуппинг

- •3.5. Организация памяти

- •3.6. Внешние зу

- •3.7. Контрольные вопросы и задания

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080)

- •4.1 Структура мп к580вм80

- •4.2 Основные технические характеристики мп кр580вм80а

- •4.3 Регистровая модель мп к580вм80

- •4.4 Классификация команд мп кр580вм80а

- •4.5 Команды пересылки (перемещения) данных

- •4.5.1 Пересылка из регистра в регистр

- •4.5.2 Непосредственная пересылка

- •4.5.3 Непосредственная загрузка пары регистров

- •4.5.4 Запоминание/загрузка аккумулятора и пары hl

- •4.5.5 Ввод из пары регистров в стек

- •4.5.6 Ввод а и f в стек

- •4.5.7 Выбор из стека пары регистров

- •4.5.8 Выбор (a) и (f) из стека

- •4.5.9 Обмен данными

- •4.5.10 Пересылка нl

- •4.6 Приращение / отрицательное приращение

- •4.6.1 Приращение/отрицательное приращение регистра

- •4.6.2 Приращение пары регистров

- •4.6.3 Отрицательное приращение пары регистров

- •4.7 Арифметические и логические операции

- •4.7.1 Арифметические операции над (a) и (r)

- •4.7.2 Арифметические операции с непосредственной адресацией

- •4.7.3 Сложение содержимого пар регистров

- •4.7.4 Логические операции над (а) и (r)

- •0800) Ora c

- •4.7.5 Логические операции с непосредственной адресацией

- •4.7.6 Операции сравнения

- •4.7.7 Операции циклического сдвига (а).

- •4.7.8 Дополнение аккумулятора

- •4.8 Команды перехода и вызова подпрограмм

- •4.8.1 Команды переходов

- •4.8.2 Команды вызова подпрограмм и возврата из подпрограмм

- •4.9 Команды ввода – вывода

- •4.9.1 Ввод данных из входного порта

- •4.9.2 Вывод данных в выходной порт

- •4.10 Команды управления

- •4.10.1 Рестарт (повторный запуск)

- •4.10.2 Изменение (Тс)

- •0800) Stc

- •0800) Cmc

- •4.10.3 Управление прерываниями

- •4.10.4 Двоично-десятичная коррекция

- •4.10.5 Пустая операция

- •4.10.6 Останов

- •4.11 Микропроцессор intel8085

- •4.11.1 Архитектура мп intel8085

- •4.11.2 Регистры мп Intel 8085

- •4.11.3 Ввод и вывод последовательных данных

- •4.12 Контрольные вопросы и задания

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086)

- •5.1. Устройство и работа микропроцессора Intel 8086 (k1810bm86)

- •5.1.1. Структура микропроцессора Intel 8086

- •5.1.2. Режимы работы микропроцессора

- •5.1.3. Структура минимально укомплектованной системы на базе микропроцессора к1810вм86

- •5.1.4. Структура системы средней сложности на базе микропроцессора к1810вм86

- •5.2. Программная модель микропроцессора Intel 8086

- •5.2.1. Пользовательские регистры

- •5.2.2. Регистры общего назначения

- •5.2.3. Сегментные регистры

- •5.2.4. Регистры состояния и управления

- •5.3. Формирование физического адреса в микропроцессоре Intel 8086

- •5.4 Способы адресации микропроцессора

- •5.5 Контрольные вопросы и задания

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4

- •6.1. Архитектура микропроцессоров 80186/80188

- •6.2. Микропроцессор 80286

- •6.2.1 Аппаратные особенности

- •6.2.2 Система команд

- •6.2.3. Виртуальная память

- •6.3. Микропроцессоры 80386 и 80486

- •6.3.1. Микропроцессор 80386

- •6.4. Микропроцессоры Pentium и Pentium Pro

- •6.5. Специальные регистры микропроцессора Pentium

- •6.6. Управление памятью микропроцессора Pentium

- •6.7. Новые команды микропроцессора Pentium

- •6.8. Специальные особенности микропроцессора Pentium Pro

- •6.9. Микропроцессоры Pentium II, Pentium III и Pentium 4

- •6.9.1. Сопряжение с памятью

- •6.9.2. Набор регистров

- •6.11 Контрольные вопросы и задания

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus

- •7.1 Микропроцессор к1801вм1

- •7.1.1 Структурная схема микропроцессора к1801вм1

- •7.1.2 Основные технические характеристики

- •7.1.3 Регистровая модель микропроцессора

- •7.1.4 Адресное пространство

- •7.1.5 Формат команд

- •7.1.6 Методы адресации

- •7.2. Системная магистраль q-Bus

- •7.2.1 Временная диаграмма цикла ввод

- •7.2 2 Временная диаграмма цикла вывод

- •7.2.3 Цикл ввод-пауза-вывод

- •7.2.4 Временная диаграмма предоставления прямого доступа к памяти

- •7.2.5 Временная диаграмма прерывания

- •7.3 Контрольные вопросы и задания

- •Глава 8. Понятие и задачи интерфейса

- •8.1 Интерфейс

- •8.2 Селекция магистралей

- •8.2.1 Схемы централизованной селекции

- •8.2.2 Схемы децентрализованной селекции

- •8.3 Синхронизация обмена по магистрали

- •8.4 Координация взаимодействия устройств на магистрали

- •8.5 Контрольные вопросы и задания

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus

- •9.1 Isa

- •9.2. Порядок обмена по системной магистрали isa

- •9.2.1. Особенности магистрали isa

- •9.2.2. Сигналы магистрали isa

- •9.2.3. Циклы магистрали isa

- •9.3 Разработка устройств сопряжения для isa

- •9.3.1. Проектирование аппаратуры для сопряжения с isa

- •9.4 Разработка устройств сопряжения для q-bus

- •9.5 Контрольные вопросы и задания

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле

- •10.1 Промышленные Fieldbus (полевые) сети

- •10.1.1 Модель osi (Open System Interconnection) (iso/osi) для стандартов.

- •10.1.2 Локальная сеть на основе интерфейса rs-485, объединяющая несколько приемо-передатчиков.

- •10.2 Этапы развития fieldbus технологий

- •10.3 Сетевые протоколы в автомобиле

- •10.4 Контрольные вопросы и задания

- •Глава 11. Интегральные схемы программируемой логики (ис пл)

- •11.1. Классификация ис программируемой логики

- •11.2. Конструктивно-технологические типы современных программируемых элементов

- •11.3. Области применения микросхем с программируемой логикой

- •11.4 Системные свойства ис пл

- •11.5 Типовые схемотехнические решения

- •11.6 Приемы дополнительной обработки сигнала

- •11.7 Организация двунаправленных выводов

- •11.8 Схема программирования типа выхода ячейки (введение триггера)

- •11.9 Fpga (программируемые пользователем вентильные матрицы)

- •11.10. Полные ресурсы межсоединений в микросхемах cpld

- •11.11 Контрольные вопросы и задания

- •Заключение

- •Глоссарий

- •Список литературы

11.7 Организация двунаправленных выводов

В зависимости от конкретной задачи могут потребоваться различные соотношения чисел входов и выходов. Поэтому специализация выводов и жесткое разделение их на входы и выходы сужает функциональные возможности микросхемы. Вследствие этого широкое применение находят микросхемы с двунаправленными выводами (рис. 11.7), которые путем программирования можно сделать либо входами, либо выходами.

|

|

|

Рис. 11.7 Схема организации двунаправленных выводов |

Рассмотрим устройство схемы, здесь КП – контактная площадка, сигнал OE=0 переводит буфер в третье состояние; сигнал OE=1 переводит буфер в активное состояние.

Рассмотрим работу схемы, пусть:

OE1=1 – буфер 1 активен;

OE2=0 – буфер 2 в третьем состоянии;

тогда сигнал из схемы проходит на КП – выходной сигнал, вывод является выходом.

Предположим:

OE1= 0 – буфер 1в третьем состоянии;

OE2=1 – буфер 2 активен;

тогда сигнал с КП подается внутрь ПЛИС, вывод является входом.

11.8 Схема программирования типа выхода ячейки (введение триггера)

Введение триггеров непосредственно в логические блоки обогащает функциональные возможности микросхем программируемой логики (рис. 11.8), причем обычно логическое функционирование триггеров программируется. Чаще всего триггеры строятся на основе триггера D типа и дополнительных логических элементов.

|

|

|

Рис. 11.8 Схема программирования типа выхода ячейки |

Рассмотрим

устройство и работу схемы. Ее элементы:

синхронный триггер Д типа, 2 мультиплексора

и сумматор по модулю 2 (М2). Если 1-ый

мультиплексор подключает триггер по

входу D к линии F, то данный триггер

работает как D триггер. Если мультиплексор

1 подключает ко входу D выход сумматора

по модулю 2, то работа схемы требует

более серьезного анализа: пусть F = 0,

тогда триггер находится в режиме

хранения, при F = 1 на D вход подается

сигнал

![]() и триггер работает как Т-триггер (счетный

режим). Мультиплексор 2 может либо

напрямую передать F на выход ячейки,

тогда ячейка работает как комбинационная,

либо подключить на выход ячейки выход

триггера, тогда ячейка может работать

как последовательностная.

и триггер работает как Т-триггер (счетный

режим). Мультиплексор 2 может либо

напрямую передать F на выход ячейки,

тогда ячейка работает как комбинационная,

либо подключить на выход ячейки выход

триггера, тогда ячейка может работать

как последовательностная.

11.9 Fpga (программируемые пользователем вентильные матрицы)

Их основой служит матрица регулярно расположенных по строкам и столбцам идентичных конфигурируемых логических блоков. Между строками и столбцами логических блоков проходят трассировочные каналы, содержащие ресурсы межсоединений При программировании логические блоки настраиваются на требуемые операции преобразования данных, а трассировочные ресурсы – на обеспечение нужных взаимных соединений логических блоков.

Свойства и возможность FPGA во многом определяются типом логических блоков и системой межсоединений.

Типичными представителями логических блоков FPGA являются:

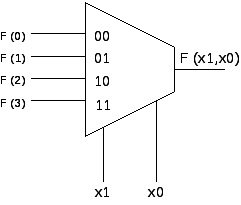

- логические модули на основе мультиплексоров (рис. 11.9);

- логические модули на основе программируемой памяти (блоки типа LUT – Look-Up Tables), рис. 11.10.

Известно, что мультиплексоры способны работать в режиме универсальных логических модулей, если на их адресные входы подавать аргументы логической функции, а на информационные – значения логической функции для соответствующей комбинации аргументов.

Самые распространенные логические блоки FPGA – табличные (LUTs). Эти блоки часто называют табличными функциональными преобразователями. В них применяются программируемые запоминающие устройства. В этом случае набор аргументов служит адресом, по которому записывается соответствующее значение функции, если разрядность памяти равна 1 биту, или значения m функций, если разрядность ячеек памяти равна m.

|

Рис. 11.9 Схема мультиплексора в режиме логического блока |

|

|

|

Рис. 11.10 Схема табличного логического блока

|

Для систем межсоединений FPGA характерны сегментированные линии (рис. 11.11 а)), составленные из отдельных отрезков, соединяемых друг с другом программируемыми элементами. Программируемые элементы могут быть размещены в переключательных блоках, конфигурируемых так, чтобы составить из сегментов необходимые цепи. Программируемые соединительные элементы (ключи) из-за собственных паразитных элементов (сопротивление R и емкость C) вносят в передачу сигналов задержки, которые доминируют над другими составляющими.

Связи в этой структуре являются сегментированными, в результате чего время задержки распространения по одному сегменту определяется сопротивлением и емкостью ключевого элемента, следовательно, время задержки будет зависеть от выбранного пути (т.е. от того, как много окажется ключевых элементов). Это потенциально опасно в связи с возникновением состязаний.

|

|

|

Рис. 11.11 Структура FPGA с межсоединениями общего назначения (а), схема переключательного блока (б) и узла пересечения линий с программируемыми соединениями в этом блоке (в)

|

Для большей универсальности, кроме связей единичной длины, вводят связи двойной длины, прямые линии (от одного логического блока до другого), длинные линии (они охватывают несколько логических блоков) и линии глобального тактирования (проходят через весь кристалл).