- •К.А. Палагута Микропроцессоры и интерфейсные средства транспортных средств

- •Москва 2011

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия 11

- •Глава 2 Режимы работы мпс 33

- •Глава 3. Реализация и организация памяти мп 57

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080) 77

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086) 138

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4 159

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus 209

- •Глава 8. Понятие и задачи интерфейса 239

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus 255

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле 308

- •Глава 11. Интегральные схемы программируемой логики (ис пл) 326

- •Предисловие

- •Введение

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия

- •1.1 Определение микропроцессора, классификация мп

- •1.2 Микропроцессорный комплект (мпк)

- •1.3 Микропроцессорная система

- •1.4 Линия, шина, магистраль

- •1.5 Типы магистралей

- •1.6 Шина адреса, раздельные и объединенные адресные пространства памяти и устройств ввода-вывода

- •1.7 Шина данных

- •1.8 Шина управления

- •1.9 Архитектура и структура микропроцессора

- •1.10 Cisc и risc процессоры, конвейерное выполнение команд программы

- •1.11 Конвейерная обработка данных

- •1.12 Контрольные вопросы и задания

- •Глава 2 Режимы работы мпс

- •2.1 Режим обмена данными под управлением процессора

- •2.2 Режим пдп

- •2.3 Режим прерывания

- •2.4 Контрольные вопросы и задания

- •Глава 3. Реализация и организация памяти мп

- •3.1. Виды запоминающих устройств (зу)

- •3.2. Кэш-память

- •3.3. Когерентность, механизмы сквозной и обратной записи

- •3.4. Алгоритмы обновления содержимого заполненных строк, снуппинг

- •3.5. Организация памяти

- •3.6. Внешние зу

- •3.7. Контрольные вопросы и задания

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080)

- •4.1 Структура мп к580вм80

- •4.2 Основные технические характеристики мп кр580вм80а

- •4.3 Регистровая модель мп к580вм80

- •4.4 Классификация команд мп кр580вм80а

- •4.5 Команды пересылки (перемещения) данных

- •4.5.1 Пересылка из регистра в регистр

- •4.5.2 Непосредственная пересылка

- •4.5.3 Непосредственная загрузка пары регистров

- •4.5.4 Запоминание/загрузка аккумулятора и пары hl

- •4.5.5 Ввод из пары регистров в стек

- •4.5.6 Ввод а и f в стек

- •4.5.7 Выбор из стека пары регистров

- •4.5.8 Выбор (a) и (f) из стека

- •4.5.9 Обмен данными

- •4.5.10 Пересылка нl

- •4.6 Приращение / отрицательное приращение

- •4.6.1 Приращение/отрицательное приращение регистра

- •4.6.2 Приращение пары регистров

- •4.6.3 Отрицательное приращение пары регистров

- •4.7 Арифметические и логические операции

- •4.7.1 Арифметические операции над (a) и (r)

- •4.7.2 Арифметические операции с непосредственной адресацией

- •4.7.3 Сложение содержимого пар регистров

- •4.7.4 Логические операции над (а) и (r)

- •0800) Ora c

- •4.7.5 Логические операции с непосредственной адресацией

- •4.7.6 Операции сравнения

- •4.7.7 Операции циклического сдвига (а).

- •4.7.8 Дополнение аккумулятора

- •4.8 Команды перехода и вызова подпрограмм

- •4.8.1 Команды переходов

- •4.8.2 Команды вызова подпрограмм и возврата из подпрограмм

- •4.9 Команды ввода – вывода

- •4.9.1 Ввод данных из входного порта

- •4.9.2 Вывод данных в выходной порт

- •4.10 Команды управления

- •4.10.1 Рестарт (повторный запуск)

- •4.10.2 Изменение (Тс)

- •0800) Stc

- •0800) Cmc

- •4.10.3 Управление прерываниями

- •4.10.4 Двоично-десятичная коррекция

- •4.10.5 Пустая операция

- •4.10.6 Останов

- •4.11 Микропроцессор intel8085

- •4.11.1 Архитектура мп intel8085

- •4.11.2 Регистры мп Intel 8085

- •4.11.3 Ввод и вывод последовательных данных

- •4.12 Контрольные вопросы и задания

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086)

- •5.1. Устройство и работа микропроцессора Intel 8086 (k1810bm86)

- •5.1.1. Структура микропроцессора Intel 8086

- •5.1.2. Режимы работы микропроцессора

- •5.1.3. Структура минимально укомплектованной системы на базе микропроцессора к1810вм86

- •5.1.4. Структура системы средней сложности на базе микропроцессора к1810вм86

- •5.2. Программная модель микропроцессора Intel 8086

- •5.2.1. Пользовательские регистры

- •5.2.2. Регистры общего назначения

- •5.2.3. Сегментные регистры

- •5.2.4. Регистры состояния и управления

- •5.3. Формирование физического адреса в микропроцессоре Intel 8086

- •5.4 Способы адресации микропроцессора

- •5.5 Контрольные вопросы и задания

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4

- •6.1. Архитектура микропроцессоров 80186/80188

- •6.2. Микропроцессор 80286

- •6.2.1 Аппаратные особенности

- •6.2.2 Система команд

- •6.2.3. Виртуальная память

- •6.3. Микропроцессоры 80386 и 80486

- •6.3.1. Микропроцессор 80386

- •6.4. Микропроцессоры Pentium и Pentium Pro

- •6.5. Специальные регистры микропроцессора Pentium

- •6.6. Управление памятью микропроцессора Pentium

- •6.7. Новые команды микропроцессора Pentium

- •6.8. Специальные особенности микропроцессора Pentium Pro

- •6.9. Микропроцессоры Pentium II, Pentium III и Pentium 4

- •6.9.1. Сопряжение с памятью

- •6.9.2. Набор регистров

- •6.11 Контрольные вопросы и задания

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus

- •7.1 Микропроцессор к1801вм1

- •7.1.1 Структурная схема микропроцессора к1801вм1

- •7.1.2 Основные технические характеристики

- •7.1.3 Регистровая модель микропроцессора

- •7.1.4 Адресное пространство

- •7.1.5 Формат команд

- •7.1.6 Методы адресации

- •7.2. Системная магистраль q-Bus

- •7.2.1 Временная диаграмма цикла ввод

- •7.2 2 Временная диаграмма цикла вывод

- •7.2.3 Цикл ввод-пауза-вывод

- •7.2.4 Временная диаграмма предоставления прямого доступа к памяти

- •7.2.5 Временная диаграмма прерывания

- •7.3 Контрольные вопросы и задания

- •Глава 8. Понятие и задачи интерфейса

- •8.1 Интерфейс

- •8.2 Селекция магистралей

- •8.2.1 Схемы централизованной селекции

- •8.2.2 Схемы децентрализованной селекции

- •8.3 Синхронизация обмена по магистрали

- •8.4 Координация взаимодействия устройств на магистрали

- •8.5 Контрольные вопросы и задания

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus

- •9.1 Isa

- •9.2. Порядок обмена по системной магистрали isa

- •9.2.1. Особенности магистрали isa

- •9.2.2. Сигналы магистрали isa

- •9.2.3. Циклы магистрали isa

- •9.3 Разработка устройств сопряжения для isa

- •9.3.1. Проектирование аппаратуры для сопряжения с isa

- •9.4 Разработка устройств сопряжения для q-bus

- •9.5 Контрольные вопросы и задания

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле

- •10.1 Промышленные Fieldbus (полевые) сети

- •10.1.1 Модель osi (Open System Interconnection) (iso/osi) для стандартов.

- •10.1.2 Локальная сеть на основе интерфейса rs-485, объединяющая несколько приемо-передатчиков.

- •10.2 Этапы развития fieldbus технологий

- •10.3 Сетевые протоколы в автомобиле

- •10.4 Контрольные вопросы и задания

- •Глава 11. Интегральные схемы программируемой логики (ис пл)

- •11.1. Классификация ис программируемой логики

- •11.2. Конструктивно-технологические типы современных программируемых элементов

- •11.3. Области применения микросхем с программируемой логикой

- •11.4 Системные свойства ис пл

- •11.5 Типовые схемотехнические решения

- •11.6 Приемы дополнительной обработки сигнала

- •11.7 Организация двунаправленных выводов

- •11.8 Схема программирования типа выхода ячейки (введение триггера)

- •11.9 Fpga (программируемые пользователем вентильные матрицы)

- •11.10. Полные ресурсы межсоединений в микросхемах cpld

- •11.11 Контрольные вопросы и задания

- •Заключение

- •Глоссарий

- •Список литературы

6.5. Специальные регистры микропроцессора Pentium

Микропроцессор Pentium является, по существу, таким же микропроцессором, как 80386 и 80486, за исключением введения некоторых дополнительных функций и изменений в набор управляющих регистров. В этом разделе рассматриваются различия в структуре управляющих регистров и регистра флагов микропроцессора Pentium и микропроцессоров 80386 и 80486.

Управляющие регистры

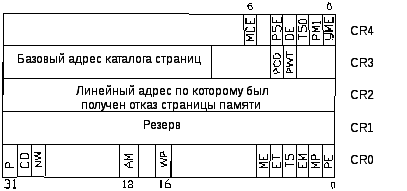

На рис. 6.9 показан формат управляющих регистров для микропроцессора Pentium. В набор управляющих регистров добавлен новый управляющий регистр CR4. В данном разделе текста объясняются только новые компоненты в управляющих регистрах микропроцессора Pentium. Формат управляющих регистров микропроцессора 80386 приведен на рис. 6.5

|

|

|

Рис. 6.9. Формат управляющих регистров микропроцессора Pentium |

□ CD

Бит CD (cache disable) регистра CR0 управляет внутренней кэш-памятью процессора. Если CD = 1, то кэш запрещен и не заполняется новыми данными по промахам при обращении в кэш, но продолжает функционировать при удачном обращении в кэш-память. Если CD = 0, то микропроцессор работает как обычно — промахи вынуждают кэш заполняться новыми данными. Этого бита не было в процессоре 80386, но он появился в 80486.

□ NW

Бит NW (not write-through) регистра CR0 выбирает режим работы для данных кэш-памяти. Если бит NW = 1, то для кэш-памяти данных запрещается сквозная запись. Этого бита не было в процессоре 80386, он стал использоваться, начиная с процессора 80486.

□ AM

Бит AM (alignment mask) регистра CR0 позволяет выполнять контроль выравнивания, если он установлен, и запрещает этот контроль, если он очищен. Контроль выравнивания выполняется только в защищенном режиме, когда бит AM установлен, установлен флаг АС, а уровень привилегий имеет значение 3 (режим пользователя). Бит стал использоваться, начиная с процессора 80486.

□ WP

Если бит WP (write protect) регистра CR0 установлен, то он защищает от записи страницы уровня пользователя при доступе в режиме супервизора. Если этот бит очищен, то страницы уровня пользователя, предназначенные только для чтения, могут быть затерты записью процессом супервизора. Этого бита не было в процессоре 80386, но он появился, начиная с микропроцессора 80486.

□ NE

При установленном бите NE (numeric error) регистра CR0 разрешается стандартный механизм сообщений об ошибках при операциях сопроцессора. Если бит NE = 1, то вывод FERR активизируется при ошибке сопроцессора. Если бит NE = 0, то любая ошибка сопроцессора игнорируется. Этот бит стал использоваться, начиная с процессора 80486.

□ PCD

Бит PCD (page cache disable) регистра CR3 запрещает кэширование страниц. Состояние этого бита устанавливается в зависимости от состояния одноименного вывода микропроцессора. Этот бит стал использоваться, начиная с процессора 80486.

□ PWT

Состояние бита PWT (page write-through) регистра CR3 устанавливается в зависимости от состояния одноименного вывода микропроцессора во время циклов шины, не работающих со страницами (например, циклов квитирования прерывания), когда подкачка страниц разрешена. Если подкачка страниц запрещена, то состояние этого бита устанавливается в любых циклах шины. Этого бита не было в процессоре 80386, но он появился, начиная с микропроцессора 80486.

□ VME

Бит VME (virtual mode extension) регистра CR4 разрешает поддержку флага виртуального прерывания в защищенном режиме. Если бит VME = 0, то поддержка виртуального прерывания запрещается.

□ PVI

Бит PVI (protected mode virtual interrupt) регистра CR4 разрешает использование флага виртуального прерывания в защищенном режиме.

□ TSD

Бит TSD (time stamp disable) регистра CR4 управляет командой rdtsc.

□ DE

Бит DE (debugging extension) регистра CR4, если он установлен, то попытки обращения к регистрам DR4 и DR5 вызывают исключение недопустимого кода операции, если же бит сброшен, то разрешает использовать регистры DR4 и DR5 для установки контрольных точек останова при обращении к портам ввода-вывода.

□ PSE

Бит PSE (page size extension) регистра CR4, если он установлен, разрешается использовать страницы памяти размером по 4 Мбайта, если же он сброшен, то используются стандартные страницы по 4 Кбайта.

□ МСЕ

Бит MCE (machine check enable) регистра CR4, если он установлен, то разрешается исключение машинного контроля (аппаратной проверки), возникающее, когда блок внутреннего контроля операций внутри чипа или на шине обнаруживает ошибку, если же бит МСЕ сброшен, то это исключение запрещается.

Микропроцессор Pentium в сравнении с микропроцессором 80486 имеет новые особенности, которые управляются с помощью битов регистра CR4, а в сравнении с процессором 80386 содержит еще несколько битов и в регистре CR0.

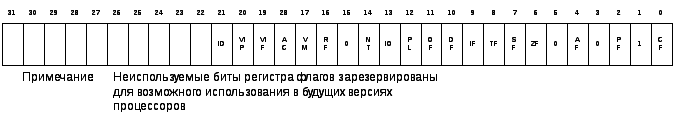

Регистр флагов EFLAG

Расширенный регистр флагов EFLAG (extended flag register) в микропроцессоре Pentium немного видоизменен. На рис. 6.10 показано содержимое регистра EFLAG. В этот регистр процессора Pentium добавлены три новых флага (бита) по сравнению с микропроцессором 80486. Неиспользуемые биты регистра флагов зарезервированы для возможного использования в будущих версиях процессоров.

|

|

|

Рис. 6.10. Формат регистра EFLAG микропроцессора Pentium

|

□ ID

Бит ID (identification flag) используется командой идентификации процессора cpuid для тестирования. Если программа может устанавливать и сбрасывать флаг ID, то процессор поддерживает команду cpuid.

□ VIP

Бит VIР (virtual interrupt pending) указывает, что виртуальное прерывание задерживается. Системное программное обеспечение устанавливает этот флаг, если требуется отложить обработку прерывания. Используется совместно с VIF.

□ VIF

Бит VIF (virtual interrupt) — это виртуальный флаг прерывания, который является виртуальным образом флага IF и используется совместно с флагом VIP.

Следует отметить, что флаг AC (alignment check), указывающий на состояние бита AM в управляющем регистре CR0, был добавлен еще в микропроцессоре 80486.

Встроенный самоконтроль

Встроенный тест самоконтроля BIST (built-in self-test) выполняется после включения питания посредством установки сигнала высокого логического уровня на вывод INIT, в то время как сигнал на выводе RESET изменяется с высокого на низкий логический уровень. Тест BIST проверяет 70% внутренней структуры микропроцессора Pentium примерно за 150 мкс. По завершению проверки встроенного самоконтроля микропроцессор Pentium сообщает результат в регистре ЕАХ. Если ЕАХ = 0, то самоконтроль пройден и микропроцессор Pentium готов к работе. Если же бит ЕАХ содержит любой другой показатель, то микропроцессор функционирует неправильно и неисправен.