- •Электроника

- •Содержание

- •1.1 Основы алгебры логики………………………………………………..5

- •1 Цифровые интегральные микросхемы

- •1.1 Основы алгебры логики

- •1.1.1 Основные определения

- •1.1.2 Некоторые логические функции и реализующие их логические элементы

- •1.1.3 Основные законы и соотношения алгебры логики

- •Сочетательный закон

- •Распределительный закон

- •1.2 Параметры цифровых интегральных микросхем

- •1.2.1 Параметры цифровых интегральных микросхем (цимс), имеющие размерность напряжение.

- •1.2.2 Параметры, соответствующие размерности тока.

- •1.2.3 Параметры, имеющие размерность мощности.

- •1.3.2 Характеристики дтл.

- •1.4 Транзисторно – транзисторная логика.

- •1.5 Ттл со сложным инвертором.

- •1.6 Ттл с открытым коллекторным выходом.

- •1.7 Ттл с тремя состояниями на выходе

- •1.8 Транзисторно-транзисторная логика Шоттки

- •1.9 Комплиментарная мдп логика

- •2 Операционные усилители

- •2.1 Параметры и характеристики оу

- •2.3 Дифференциальный усилитель

- •2.4 Составной транзистор

- •2.5 Источник тока

- •2.6 Схема сдвига уровня

- •2.7 Эмиттерный повторитель

- •2.8 Инвертирующий усилитель на оу.

- •2.9 Неинвертирующий усилитель

- •3 Технологические основы производства полупроводниковых интегральных микросхем

- •3.1 Подготовительные операции

- •3. 2 Эпитаксия

- •3.3 Термическое окисление

- •3.4 Литография

- •3.5 Легирование

- •3.5.2 Ионная имплантация.

- •3.6.1 Термическое (вакуумное) напыление.

- •3.6.2 Катодное напыление.

- •3.6.3 Ионно-плазменное напыление.

- •4 Полупроводниковые

- •4.1 Методы изоляции элементов в ппимс

- •4.1.1 Изоляция элементов обратно смещенными pn-переходами.

- •4.1.2 Резистивная изоляция.

- •4.1.3 Диэлектрическая изоляция

- •4.2 Планарно-эпитаксиальный биполярный транзистор

- •4.2.1 Этапы изготовления

- •4.2.2 Распределение примесей.

- •4.2.3 Эквивалентная схема.

- •4.3 Планарно-эпитаксиальный биполярный транзистор

- •4.4 Разновидности биполярных транзисторов

- •4.4.1 Многоэмиттерный транзистор.

- •4.4.2 Транзистор с барьером Шоттки.

- •4.4.3 Транзисторы р-n-р

- •4.5 Интегральные диоды

- •4.6 Полевые транзисторы

- •4.6.1 Полевые транзисторы с управляющим p-n переходом

- •4.6.3 Мноп-транзистор.

- •4.7 Полупроводниковые резисторы

- •4.7.1 Диффузионные резисторы.

- •4.7.2 Ионно-легированные резисторы.

- •4.8 Полупроводниковые конденсаторы

- •5.1 Подложки гимс.

- •5.2 Резисторы.

- •5.3 Конденсаторы

- •5.4 Катушки индуктивности

2.5 Источник тока

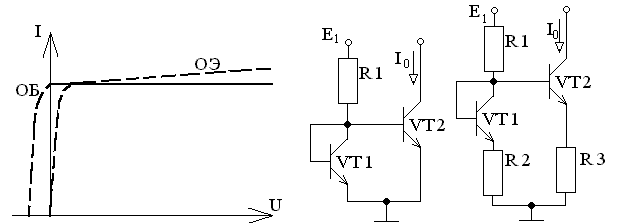

Неизменное значение постоянного тока I0, независимое от параметров цепи (нагрузки), может обеспечить только идеальный генератор тока с бесконечно большим динамическим сопротивлением, ВАХ которого параллельна оси напряжения (рисунок 2.6а). ВАХ реального генератора тока приближается к ВАХ идеального генератора только в некотором интервале значения напряжения. При этом его динамическое сопротивление хотя и очень большое, но не бесконечно большое.

Заметим, что выходная характеристика биполярного транзистора в схеме с ОБ близка к ВАХ идеального генератора тока. Следовательно, транзистор, включенный по схеме с общей базой, практически может выполнять функцию генератора тока. Cхема с ОЭ несколько уступает схеме с ОБ.

Однако на практике используется не один, а два и более транзисторов (рисунок 2.6б и 2.6в), которые обеспечивают не только получение большого динамического сопротивления, но и слабую зависимость самого тока генератора от нестабильности напряжения источников питания и температурной нестабильности элементов схемы.

-

а)

б)

в)

Рисунок 2.6

2.6 Схема сдвига уровня

Отказ от разделительных конденсаторов при соединении отдельных каскадов ИС требует применения элементов, обеспечивающих согласование выхода каскада со входом следующего каскада по величине (уровню) постоянного потенциала для сохранения работоспособности ИС.

Включение резисторных делителей для понижения потенциала приводит к снижению коэффициента усиления сигнала, так что этот способ в ИС не находит практического применения.

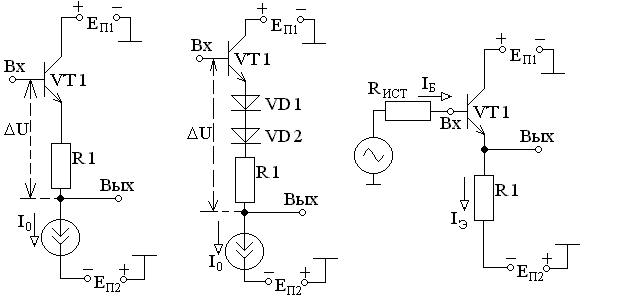

Простейшая схема сдвига уровня (ССУ) показана на рисунке 2.7а. Она представляет собой эмиттерный повторитель на транзисторе VT1, принцип работы и параметры которого будут рассмотрены ниже. Эмиттерная цепь состоит из резистора R1 и источника стабильного тока, обеспечивающего постоянство тока I0. В качестве источника тока используются схемы, рассмотренные выше. Уровень постоянной составляющей напряжения на выходе сдвинут на величину U= I0R1+ UБЭ1 по сравнению с ее значением на входе.

Каскад ослабляет переменный сигнал незначительно, так как динами -ческое (выходное) сопротивление источника тока значительно больше сопротивления R1. Тем не менее, следует заметить, что сопротивление R1 из условий согласования приходится выбирать достаточно большим, поэтому выходное сопротивление каскада, равное R1, оказывается значительным и при работе на низкоомную нагрузку будет проявляться ослабление переменного сигнала. Для борьбы с этим явлением в схему на выходе вводится дополнительный эмиттерный повторитель, исключающий влияние низкоомной нагрузки.

Температурную стабильность можно увеличить также включением в цепь эмиттера одного или нескольких диодов, как показано на рисунке 2.7б. Для более точного согласования включается резистор R1. Очевидно, что U = UБЭ +2Uд + R1I0. В качестве диодов используются интегральные транзисторы в диодном включении. Варьированием величин I0 и R1 можно получить любое значение сдвига.

|

а) |

б) |

в) |

Рисунок 2.7