- •1.Общие сведения о пэвм.

- •3.Принципы взаимодействия основных частей пэвм.

- •4. Общие сведения об операционных системах, применяемых на пэвм.

- •5.Базовая система ввода/вывода (bios). Подсистема post.

- •Вопрос 9.Файловая система fat

- •10) Ntfs

- •11)Резидентные системные программы и утилиты. Командные файлы, файлы конфигурации системы

- •Файл autoexec.Nt

- •Файлы winstart.Bat и dosstart.Bat

- •Файл config.Nt

- •12. Прерывания дисковой системы пэвм.

- •14. Назначение, структурная схема и программирование контроллеров нdd.

- •15. Назначение и состав системы ввода-вывода.

- •19. Организация обмена данными через параллельные порты.

- •20. Характеристики микропроцессоров intel и amd

- •21. Математические сопроцессоры.

- •1. Регистры ммх

- •2. Типы данных ммх

- •3. Команды пересылки данных ммх

- •4. Команды преобразования типов ммх

- •5. Арифметические операции ммх

- •6. Команды сравнения ммх

- •7. Логические операции ммх

- •8. Сдвиговые операции ммх

- •9. Команды управления состоянием ммх

- •10. Расширение amd 3d

- •25. Модель микропроцессора для программиста.

- •Реальный режим общие сведения

- •26. Спецификация регистров микропроцессора. Режимы работы. Типы данных.

- •Реальный режим общие сведения

- •Работа с адресами

- •Обработка прерываний

- •27. Системные регистры.

- •Регистры управления памятью

- •Регистры управления процессором

- •Отладочные регистры

- •Машинно-специфичные регистры

- •31. Системные ресурсы пэвм

- •32. Дескрипторы

- •33. Сегмент состояния задачи

- •35. Прерывания пэвм

- •Исключения в защищённом режиме

- •Обработка аппаратных прерываний

- •39. Контроллер прерываний. Исключения.

- •42 Полупроводниковые пзу, рпзу.

- •43 Сегментация. Физические и логические адреса.

- •Общие сведения

- •Работа с адресами

- •Обработка прерываний

- •Вход в защищённый режим(286)

- •2.1. Подготовка к переключению в защищённый режим

- •2.2. Переключение в защищённый режим

- •2.3. Возврат в реальный режим

- •47 Режим виртуального процессора i8086

- •48 Преобразование адресов

- •Программирование микросхемы таймера 8253/8254.

- •50.Каналы и управление таймеров. Микросхемы таймера 8253/8254

- •Средства ms-dos для работы с таймером

- •51.Режимы работы таймеров. Микросхемы таймера 8253/8254

- •52.Назначение, структурная схема контроллера пдп(dma).

- •53 Программирование контроллера пдп(dma).

- •54 Организация ввода данных с клавиатуры.

- •56. Прерывания и порты клавиатуры.

- •58. Прерывания видеосистемы.

- •59.Организация вывода информации на экран дисплея через память видеоадаптера.

- •60. О рганизация вывода информации на экран дисплея через прерывания. Прерывания dos

- •Прерывания bios

- •Int 10h

- •Int 1Dh

- •Int 1Fh

Общие сведения

Реальным называется режим работы процессора после начальной загрузки. Процессоры первого поколения (i8088 и i8086) могли работать только в таком режиме. Процессор i80286 и 32-битные процессоры могут работать и в других режимах (защищенном и виртуальном), но после перезагрузки системы все равно находятся в реальном режиме. Этот режим является базовым режимом для операционной системы DOS, другие системы также используют его перед переключением в другие режимы.

Работа с адресами

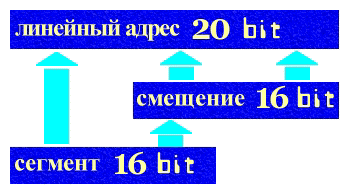

В реальном режиме линейный (физический) адрес формируется при помощи сегмента и смещения. Сегмент обычно хранится в специальном регистре - сегментном или указывается явно. При формировании 20-разрядного адреса (именно такова разрядность адресной шины первых процессоров) сегмент содержит первые 16 разрядов. Смещение содержит младшие 16 разрядов, 12 из которых добавляются к сегменту. Такая схема получения адреса связана с тем, что в первых процессорах разрядности регистров не хватало для формирования полного адреса.

Логично предположить, что при сложении сегмента и части смещения может возникнуть переполнения. В этом случае процессоры 8088 и 8086 просто отбросят старший, 21-ый бит и адресация будет производится от начала памяти. Старшие процессоры поступят также в случае, если их адресная линия А20 (т.е. 21 бит на адресной шине) блокирована. В противном случае произойдет обращение к памяти за пределами 1-го мегабайта, что используется при работе по интерфейсу HMA.

В отличие от других режимов, в реальном режиме вся память является доступной для чтения и записи (кроме областей ROM BIOS) всем программам, что не позволяет организовать безопасную многозадачную работу.

Обработка прерываний

При выполнении инструкции INT или генерации аппаратного (асинхронного) прерывания вызывается системная процедура, адрес которой содержится в таблице векторов прерываний. Для получения нужного индекса в таблице номер прерывания умножается на 4. Из таблицы выбирается дальний указатель (4 байта - сегмент и смещение) на точку входа, сохраняются в стеке CS , IP и флаги, блокируются прерывания (флаг IF), трассировка (флаг TF) и выполняется переход в точку входа. По команде IRET управление возвращается в точку вызова или прерванного управления (в случае асинхронного прерывания). Адрес таблицы прерываний для процессоров 808x всегда один - начало памяти (0000:0000), для старших процессоров он определяется содержимым регистра IDTR.

Принципы переключения режимов работы с памятью.

Процессоры i80386 и выше могут переключаться из реального режима в защищённый и обратно с помощью команды MOV. Младший бит PE системного регистра CR0 определяет текущий режим работы процессора. Если этот бит установлен в 1, процессор работает в защищённом режиме, а если в 0 - в реальном.

Для переключения процессора из реального режима в защищённый можно использовать, например, такую последовательность команд:

mov ax, cr0

or ax, 1

mov cr0, ax

Для совместимости с процессором i80286 оставлена возможность переключения в защищённый режим с помощью команды LMSW.

Для возврата в реальный режим необходимо сбросить бит PE:

mov ax, cr0

and ax, 0fffe

mov cr0, ax

Таким образом, существует более красивый способ возврата в реальный режим, чем выполнение аппаратного сброса или перевод процессора в состояние отключения (конечно, вы по-прежнему можете пользоваться старым способом перевода процессора в реальный режим).

Перед переключением в реальный режим из защищённого программа должна выполнить следующие действия:

обеспечить равенство линейных адресов физическим;

отключить трансляцию страниц, сбросив бит PG в регистре CR0;

загрузить ноль в регистр CR3 для сброса кэш-памяти страниц;

передать управление сегменту кода с пределом 64 килобайта;

загрузить в сегментные регистры SS, DS, ES, FS, GS селекторы дескрипторов, подготовленных для адресации памяти в реальном режиме и содержащих соответствующие реальному режиму значения;

запретить маскируемые и немаскируемые прерывания;

сбросить бит PE, переключив процессор в реальный режим;

выполнить команду дальнего перехода для очистки внутренней очереди команд процессора;

настроить систему прерываний для работы в реальном режиме;

разрешить прерывания;

загрузить в сегментные регистры значения, необходимые для работы в реальном режиме.

Как видите, процедура возврата в реальный режим сильно упростилась и ускорилась по сравнению с использованной для процессора i80286. Однако большинство программ, переключившись в защищённый режим, никогда больше не возвращаются назад. Они либо всё время работают в защищённом режиме, либо переключаются в режим виртуального процессора 8086.