- •1.Общие сведения о пэвм.

- •3.Принципы взаимодействия основных частей пэвм.

- •4. Общие сведения об операционных системах, применяемых на пэвм.

- •5.Базовая система ввода/вывода (bios). Подсистема post.

- •Вопрос 9.Файловая система fat

- •10) Ntfs

- •11)Резидентные системные программы и утилиты. Командные файлы, файлы конфигурации системы

- •Файл autoexec.Nt

- •Файлы winstart.Bat и dosstart.Bat

- •Файл config.Nt

- •12. Прерывания дисковой системы пэвм.

- •14. Назначение, структурная схема и программирование контроллеров нdd.

- •15. Назначение и состав системы ввода-вывода.

- •19. Организация обмена данными через параллельные порты.

- •20. Характеристики микропроцессоров intel и amd

- •21. Математические сопроцессоры.

- •1. Регистры ммх

- •2. Типы данных ммх

- •3. Команды пересылки данных ммх

- •4. Команды преобразования типов ммх

- •5. Арифметические операции ммх

- •6. Команды сравнения ммх

- •7. Логические операции ммх

- •8. Сдвиговые операции ммх

- •9. Команды управления состоянием ммх

- •10. Расширение amd 3d

- •25. Модель микропроцессора для программиста.

- •Реальный режим общие сведения

- •26. Спецификация регистров микропроцессора. Режимы работы. Типы данных.

- •Реальный режим общие сведения

- •Работа с адресами

- •Обработка прерываний

- •27. Системные регистры.

- •Регистры управления памятью

- •Регистры управления процессором

- •Отладочные регистры

- •Машинно-специфичные регистры

- •31. Системные ресурсы пэвм

- •32. Дескрипторы

- •33. Сегмент состояния задачи

- •35. Прерывания пэвм

- •Исключения в защищённом режиме

- •Обработка аппаратных прерываний

- •39. Контроллер прерываний. Исключения.

- •42 Полупроводниковые пзу, рпзу.

- •43 Сегментация. Физические и логические адреса.

- •Общие сведения

- •Работа с адресами

- •Обработка прерываний

- •Вход в защищённый режим(286)

- •2.1. Подготовка к переключению в защищённый режим

- •2.2. Переключение в защищённый режим

- •2.3. Возврат в реальный режим

- •47 Режим виртуального процессора i8086

- •48 Преобразование адресов

- •Программирование микросхемы таймера 8253/8254.

- •50.Каналы и управление таймеров. Микросхемы таймера 8253/8254

- •Средства ms-dos для работы с таймером

- •51.Режимы работы таймеров. Микросхемы таймера 8253/8254

- •52.Назначение, структурная схема контроллера пдп(dma).

- •53 Программирование контроллера пдп(dma).

- •54 Организация ввода данных с клавиатуры.

- •56. Прерывания и порты клавиатуры.

- •58. Прерывания видеосистемы.

- •59.Организация вывода информации на экран дисплея через память видеоадаптера.

- •60. О рганизация вывода информации на экран дисплея через прерывания. Прерывания dos

- •Прерывания bios

- •Int 10h

- •Int 1Dh

- •Int 1Fh

47 Режим виртуального процессора i8086

Процессор i80386 содержит средства для работы в так называемом режиме виртуального процессора i8086, называемого также для краткости режимом V86 или просто виртуальным режимом. Заметим, что до разработки фирмой Intel процессора i80386 термин "виртуальный режим" иногда использовался в литературе для обозначения защищённого режима работы процессора i80286.

В режим V86 процессор может перейти из защищённого режима, если установить в регистре флагов EFLAGS бит виртуального режима (VM-бит). Номер бита VM в регистре EFLAGS - 17.

Когда процессор i80386 находится в виртуальном режиме, его поведение во многом напоминает поведение хорошо знакомого нам процессора i8086. В частности, для адресации памяти используется схема <сегмент:смещение>, размер сегмента составляет 64 килобайта, а размер адресуемой в этом режиме памяти - 1 мегабайт.

Виртуальный режим предназначен для работы программ, ориентированных на процессор i8086 (или i8088). Но виртуальный режим - это не реальный режим процессора i8086, имеются существенные отличия. Процессор фактически продолжает использовать схему преобразования адресов памяти и средства мультизадачности защищённого режима.

В виртуальном режиме используется трансляция страниц памяти. Это позволяет в мультизадачной операционной системе создавать несколько задач, работающих в виртуальном режиме. Каждая из этих задач может иметь собственное адресное пространство, каждое размером в 1 мегабайт.

Все задачи виртуального режима обычно выполняются в третьем, наименее привилегированном кольце защиты. Когда в такой задаче возникает прерывание, процессор автоматически переключается из виртуального режима в защищённый. Поэтому все прерывания отображаются в операционную систему, работающую в защищённом режиме.

Обработчики прерываний защищённого режима могут моделировать функции соответствующих прерываний реального режима, что необходимо для правильной работы программ, ориентированных на реальный режим операционной системы MS-DOS.

48 Преобразование адресов

Процессор i80386 и выше в защищённом режиме использует трёхступенчатую схему преобразования адреса.

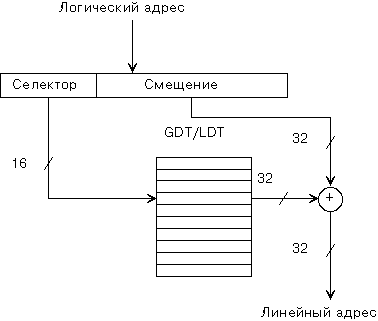

Программы используют логический адрес, состоящий из селектора и смещения (аналогично процессору i80286). Селектор полностью аналогичен используемому в процессоре i80286. Компонента смещения является 32-разрядной, т.к. допустимый размер сегмента значительно превышает 64 килобайта.

Уровень логического адреса - это первая ступень в схеме преобразования адресов.

Вторая ступень - получение из логического адреса 32-разрядного линейного адреса. Линейный адрес берётся из глобальной или локальной таблицы дескрипторов (GDT или LDT) в зависимости от соответствующего бита селектора (бит 2). Механизм получения линейного адреса напоминает механизм получения 24-разрядного физического адреса в процессоре i80286. Однако линейный адрес не отображается непосредственно на адресную шину памяти, то есть он не является физическим адресом.

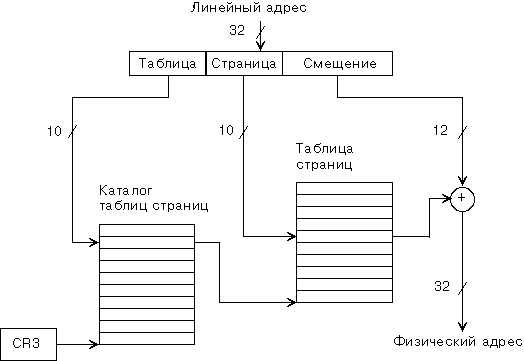

Для получения из линейного адреса физического адреса используется третья ступень - механизм страничной адресации. С помощью этого механизма 20 старших бит линейного адреса используются для выбора блока памяти размером 4 килобайта. Такой блок называется страницей физической памяти. Оставшиеся 12 бит линейного адреса представляют собой смещение внутри страницы.

Процесс преобразования логического адреса в линейный иллюстрируется рис. 17.

Рис. 17. Преобразование логического адреса в линейный.

Значение из поля индекса селектора используется в качестве индекса в таблице LDT или GDT для выборки 32-разрядного базового адреса. Этот базовый адрес складывается со второй компонентой логического адреса - смещением. В результате получается 32-разрядный линейный адрес.

Преобразование линейного адреса в физический иллюстрируется рис. 18.

Рис. 18. Преобразование линейного адреса в физический.

Процесс вычисления адреса страницы часто называют трансляцией страниц. Старшие 10 бит линейного адреса используются как индекс в таблице, называемой каталогом таблиц страниц. Расположение каталога таблиц страниц в физической памяти определяется содержимым системного регистра процессора CR3.

Каталог таблиц страниц содержит дескрипторы таблиц страниц, определяющие физический адрес таблиц страниц. В каталоге таблиц страниц всего может быть 1024 дескриптора. Самих же каталогов может быть сколько угодно, но в каждый момент времени используется только один - тот, на который указывает регистр CR3.

Следующие 10 бит линейного адреса предназначены для индексации таблицы страниц, выбранной с помощью старших 10 бит адреса. Таблица страниц содержит 1024 дескриптора, определяющих физические адреса страниц памяти. Размер одной страницы составляет 4 килобайта, т.е. 4096 байт.

Младшие 12 бит линейного адреса указывают смещение к адресуемому байту внутри страницы.

На рис. 19 представлен формат дескриптора таблицы страниц.

![]()

Рис. 19. Дескриптор таблицы страниц.

Для представления старших 20 битов физического адреса таблицы сраниц в дескрипторе используются биты 12-31. Младшие 12 битов адреса таблицы всегда равны нулю, таким образом, таблица страниц должна быть выровнена в памяти на границу 4096 байт (на границу страницы).

Формат дескриптора страницы представлен на рис. 20.

![]()

Рис. 20. Дескриптор страницы.

Биты 12-31 в дескрипторе страниц указывают старшие 20 бит физического адреса страницы. Младшие 12 бит адреса страницы всегда равны нулю.

Назначение бит 0-11 одинаково и для дескриптора таблицы страниц, и для дескриптора страницы. В таблице 4 приведено описание этих бит.

Таблица 5. Биты 0-12 дескрипторов таблиц страниц и страниц.

|

Номер бита |

Назначение |

|

0 (P) |

Бит присутствия в памяти. Установлен в 1, если определяемая данным дескриптором таблица страниц находится в оперативной памяти. Этот бит используется для организации виртуальной памяти. |

|

1 (W) |

Разрешение записи. Если бит установлен в 1, то запись в страницы разрешена. Бит используется для организации защиты от записи на уровне страниц. |

|

2 (U) |

Пользователь/супервизор. Используется для разграничения доступа к страницам операционной системы (страницы супервизора) и страницам программ пользователя. Значение бита, равное 0, соответствует страницам супервизора, 1 - страницам программы пользователя. |

|

3-4 |

Эти биты зарезервированы и должны быть установлены в 0 для совместимости со следующими моделями процессора. |

|

5 (A) |

Бит доступа. Он устанавливается процессором перед выполнением операций чтения страницы или записи в страницу. |

|

6 (D) |

Бит мусора. Устанавливается, если была выполнена запись в каталог или страницу. |

|

7-8 |

Эти биты зарезервированы и должны быть установлены в 0 для совместимости со следующими моделями процессора. |

|

9-12 (AVL) |

Эти биты доступны для использования операционной системой (AVL - Available for use). |

Мы видим, что для процессора i80386 добавилось ещё два типа таблиц, содержащих дескрипторы и, соответственно, два типа дескрипторов - дескриптор таблиц страниц и дескриптор страниц.

Для использования механизма трансляции страниц операционная система должна установить в 1 старший бит системного регистра CR0. Если этот бит не установлен в 1, физический адрес будет равен линейному, содержимое регистра адреса каталога таблиц страниц CR3 при этом для преобразования адреса использоваться не будет.

Форматы дескрипторов, располагающихся в таблицах GDT, LDT и IDT претерпели изменения по сравнению с используемыми в процессоре i80286. Например, вместо 24-битового физического адреса в дескрипторах должен находиться 32-битовый линейный адрес.

Напомним, что в дескрипторах процессора i80286 было зарезервировано два байта. Эти байты используются процессором i80386 (рис. 21).

Рис. 21. Дескрипторы для процессора i80386.

Процессор i80386 использует 32-разрядный базовый адрес сегмента и 20-разрядное поле предела. В зарезервированном для процессора i80286 поле в битах 24-31 находится старший байт 32-разрядного базового адреса сегмента. Биты 16-19 используются для хранения старших четырёх битов предела.

В процессоре i80286 поле предела указывало размер сегмента в байтах. Для процессора i80386 интерпретация поля предела зависит от установки бита G - бита гранулярности. Если бит G установлен в 1, поле предела содержит размер сегмента в страницах (размером 4096 байт). Если бит G сброшен, размер сегмента вычисляется в байтах.

Бит гранулярности G также находится в поле, которое в процессоре i80286 было отмечено как зарезервированное.

Поле, обозначенное на рис. 21 как X, указывает разрядность выполняемых команд, принятых по умолчанию. Если этот бит установлен в 1, используются 32-разрядные команды, если сброшен в 0 - 16-разрядные.

Бит AVL предназначен для использования системным программным обеспечением.

Бит S - признак системного сегмента. Если этот бит сброшен в 0, то сегмент системный.

Назначение остальных полей дескриптора аналогично используемому в процессоре i80286. В первой главе мы привели таблицу типов сегментов, в ней описаны и сегменты для процессора i80386.

49. Таймер ПЭВМ

Все IBM PC используют микросхему таймера 8253 (или 8254) для

согласования импульсов от микросхемы системных часов. Число цик-

лов системных часов преобразуется в один импульс, а последова-

тельность этих импульсов подсчитывается для определения времени,

или они могут быть посланы на громкоговоритель компьютера для

генерации звука определенной частоты. Микросхема 8253 имеет три

идентичных независимых канала, каждый из которых может программи-

роваться.

Микросхема 8253 работает независимо от процессора. Процессор

программирует микросхему и затем обращается к другим делам. Таким

образом 8253 действует как часы реального времени - она считает

свои импульсы независимо от того, что происходит в компьютере.

Однако, максимальный программируемый интервал составляет прибли-

зительно 1/12 секунды. Для подсчета интервалов времени в часы и

минуты нужны какие-то другие средства. Именно по этой причине

импульсы от нулевого канала микросхемы таймера накапливаются в

переменной, находящейся в области данных BIOS. Этот процесс пока-

зан на рис. 2-1. Это накопление обычно называется подсчетом вре-

мени суток. 18.2 раза в секунду выход канала 0 обрабатывается

аппаратным прерыванием (прерыванием таймера), которое ненадолго

останавливает процессор и увеличивает счетчик времени суток.

Число 0 соответствует полночи 12:00; когда счетчик достигает

значения эквивалентного 24 часам, он сбрасывается на ноль. Другое

время в течение суток легко определяется делением показателя

счетчика на 18.2 для каждой секунды. Счетчик времени суток ис-

пользуется в большинстве операций, связанных со временем.