- •1.Общие сведения о пэвм.

- •3.Принципы взаимодействия основных частей пэвм.

- •4. Общие сведения об операционных системах, применяемых на пэвм.

- •5.Базовая система ввода/вывода (bios). Подсистема post.

- •Вопрос 9.Файловая система fat

- •10) Ntfs

- •11)Резидентные системные программы и утилиты. Командные файлы, файлы конфигурации системы

- •Файл autoexec.Nt

- •Файлы winstart.Bat и dosstart.Bat

- •Файл config.Nt

- •12. Прерывания дисковой системы пэвм.

- •14. Назначение, структурная схема и программирование контроллеров нdd.

- •15. Назначение и состав системы ввода-вывода.

- •19. Организация обмена данными через параллельные порты.

- •20. Характеристики микропроцессоров intel и amd

- •21. Математические сопроцессоры.

- •1. Регистры ммх

- •2. Типы данных ммх

- •3. Команды пересылки данных ммх

- •4. Команды преобразования типов ммх

- •5. Арифметические операции ммх

- •6. Команды сравнения ммх

- •7. Логические операции ммх

- •8. Сдвиговые операции ммх

- •9. Команды управления состоянием ммх

- •10. Расширение amd 3d

- •25. Модель микропроцессора для программиста.

- •Реальный режим общие сведения

- •26. Спецификация регистров микропроцессора. Режимы работы. Типы данных.

- •Реальный режим общие сведения

- •Работа с адресами

- •Обработка прерываний

- •27. Системные регистры.

- •Регистры управления памятью

- •Регистры управления процессором

- •Отладочные регистры

- •Машинно-специфичные регистры

- •31. Системные ресурсы пэвм

- •32. Дескрипторы

- •33. Сегмент состояния задачи

- •35. Прерывания пэвм

- •Исключения в защищённом режиме

- •Обработка аппаратных прерываний

- •39. Контроллер прерываний. Исключения.

- •42 Полупроводниковые пзу, рпзу.

- •43 Сегментация. Физические и логические адреса.

- •Общие сведения

- •Работа с адресами

- •Обработка прерываний

- •Вход в защищённый режим(286)

- •2.1. Подготовка к переключению в защищённый режим

- •2.2. Переключение в защищённый режим

- •2.3. Возврат в реальный режим

- •47 Режим виртуального процессора i8086

- •48 Преобразование адресов

- •Программирование микросхемы таймера 8253/8254.

- •50.Каналы и управление таймеров. Микросхемы таймера 8253/8254

- •Средства ms-dos для работы с таймером

- •51.Режимы работы таймеров. Микросхемы таймера 8253/8254

- •52.Назначение, структурная схема контроллера пдп(dma).

- •53 Программирование контроллера пдп(dma).

- •54 Организация ввода данных с клавиатуры.

- •56. Прерывания и порты клавиатуры.

- •58. Прерывания видеосистемы.

- •59.Организация вывода информации на экран дисплея через память видеоадаптера.

- •60. О рганизация вывода информации на экран дисплея через прерывания. Прерывания dos

- •Прерывания bios

- •Int 10h

- •Int 1Dh

- •Int 1Fh

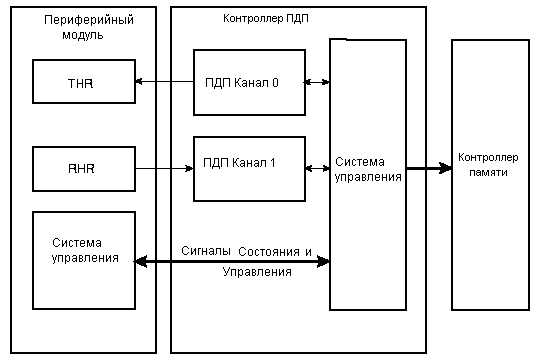

52.Назначение, структурная схема контроллера пдп(dma).

DMA (Direct Memory Access — «прямой доступ к памяти» — ПДП) — это механизм максимально быстрого обмена данными между периферийными устройствами и памятью микропроцессора/микроконтроллера без участия ядра процессора (CPU). Его основное назначение — выполнение «рутинной» работы параллельно с основной работой ядра процессора, для которой он, собственно, и проектировался. Такое разделение труда позволяет существенно увеличить производительность системы в целом (а в некоторых системах прирост скорости приложения с использованием DMA возрастает на порядки). А поскольку само ядро разгружается от «лишней» работы, то возникает возможность снижения частоты его тактирования и напряжения питания, что, в свою очередь, повышает экономичность системы. Обычное копирование блока данных из одного места памяти в другое выполняется контроллером DMA значительно быстрее, чем программное (пример: стандартная библиотечная функция в C-компиляторах) и при этом практически не «съедает» процессорного времени.

Упрощенно контроллер DMA можно представить как дополнительный аппаратный блок, размещенный на кристалле микропроцессора. Фактически он является автоматом состояний, управляемым внешними событиями. В относительно «простых» микропроцессорах контроллер DMA подключен к общей внутренней шине данных, являющейся мостом между всеми периферийными устройствами, внутренней или внешней памятью и ядром. В сложных и более быстродействующих процессорах для контроллера DMA чаще всего отводится отдельная шина или даже отдельная область памяти, что в значительной степени сокращает участие ядра процессора в операциях пересылки данных через DMA. Обычно (в зависимости от конкретного процессора) источниками и приемниками данных могут служить как внутренние периферийные узлы, так и внутренняя/внешняя память, причем в любом сочетании.

Как правило, контроллер DMA имеет несколько идентичных каналов, каждый из которых может быть настроен индивидуально и независимо друг от друга. В одну из задач контроллера DMA входит разделение общих ресурсов для каждого из каналов, в частности шины данных. В некоторых процессорах реализовано несколько шин данных, одна из которых предназначена исключительно для DMA. Помимо равноправного управления в некоторых процессорах доступно приоритетное управление каналами, в этом случае управление общими ресурсами, например, арбитраж шины данных определяется исходя из заранее заданного приоритета канала. Чаще всего число каналов в контроллере DMA кратно двум. Такая особенность объясняется просто: данные обычно передаются в обе стороны, то есть используется двунаправленная передача. Например, обмен по последовательному порту (USART, USB, SPI) с внешним устройством, микросхемой на плате или компьютером.

Любой контроллер DMA включает также узел управления прерываниями. Вместо его описания стоит привести один классический пример, касающийся приема непрерывного высокоскоростного потока байт данных по последовательному порту. Если в выбранном процессоре отсутствует контроллер DMA, то после приема очередного байта всякий раз необходима обработка прерывания, требующая некоторого процессорного. Все это будет работать до тех пор, пока хватает производительности ядра процессора. Но может возникнуть такая ситуация, что скорость потока поступающих данных как минимум сравняется и даже превысит скорость обработки этих данных. В этом случае придется либо увеличивать производительность процессора путем увеличения его тактовой частоты, либо вовсе заменить его на более подходящий.

Рис1.Контроллер

ПДП (DMA) периферийных модулей