конмпект лекций

.pdf

Uпр

|

|

|

|

|

|

|

|

|

I ( мА) |

|

|

|

|

|

|

|

|

|

|

+ |

|

|

- |

+ |

|

|

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

+ |

|

|

|

десятки вольт |

U |

|

|

|

|

|

|

||||

|

|

p |

- |

+ |

|

n |

|

||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

(мкА) |

0,6 В |

|

|

|

Еграницы |

|

|

||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||

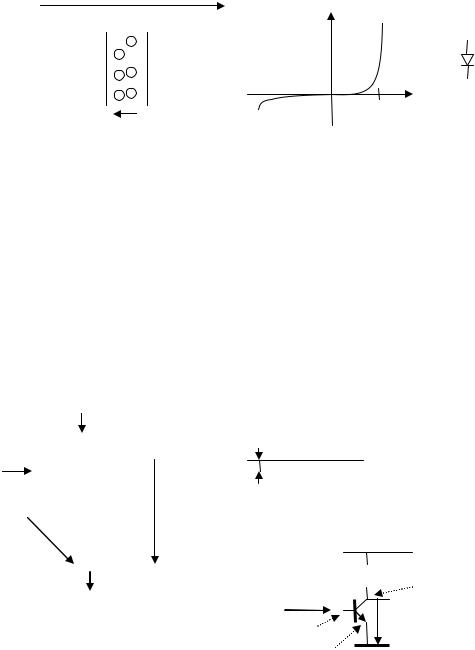

а) структура вентиля |

|

|

б) вольтамперная характеристика |

||||||

|

|

|

|

|

|

|

|

||

Рисунок 5. pn – переход

Ток в прямом направлении появляется в вентиле при напряжении внешнего источника 0,6 - 0,7 В и резко зависит от напряжения. Обратный ток pn – перехода определяется движением неосновных носителей заряда (концентрация которых весьма мала) и, практически, не зависит от величины приложенного обратного напряжения.

Управляемый pn – переход, как известно называется транзитором, и в случае npn (или обратного транзистора) представляет собой следующую структуру (рисунок 6).

|

|

Iк |

|

|

|

Эмиттер |

|

|

База |

|

Коллектор |

||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Коллектор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Iб |

|

w |

|

|

|

|

|

|

n1 |

|

|

p |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n2 |

|

|||

База |

|

n2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

p |

|

Uкэ |

n1>>n2 |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n1 |

|

|

|

|

|

б) |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uбэ |

Эмиттер |

|

|

|

|

|

|

|

|

|

|

Uп = 5 В |

||||||

|

|

|

|

|

|

|

|

|

|

|

Rк |

|

|

|

|

|

|||

|

|

|

Iэ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Коллектор |

||||||||

|

|

|

|

|

|

Iвх = I базы |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

Iэ = Iк + Iб |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

База |

|

|

Uвых = U кэ |

|||||||||

|

|

а) |

|

|

Эмиттер |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

в) |

|

|

|

|

|

|

|

|

|

||

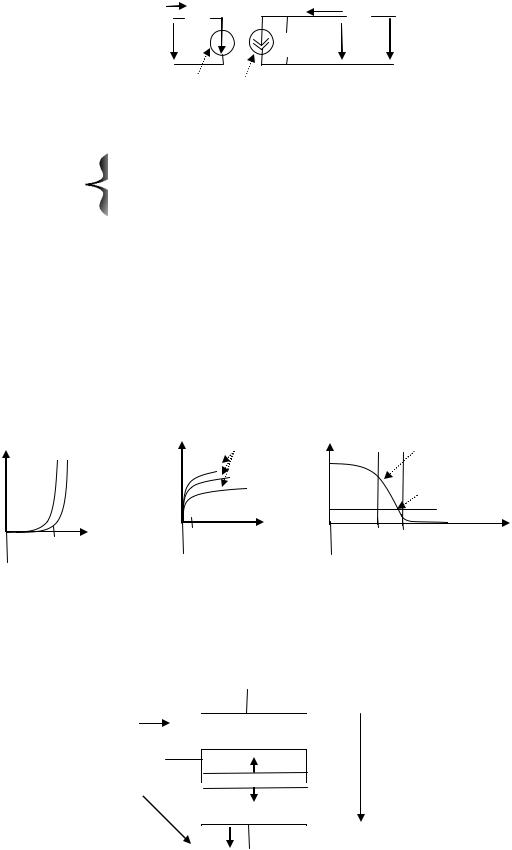

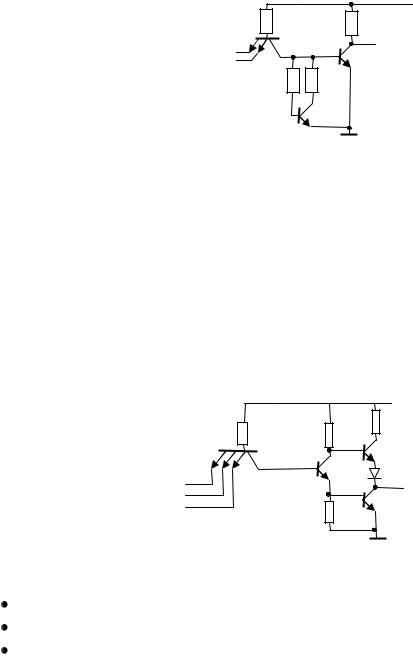

Рисунок 6 . Упрощенная (а), реальная (б) структуры npn- транзистора и схема биполярного насыщенного ключа (в)

Формы и концентрации эмиттера и коллектора выполняют таким образом, чтобы эмиттер наилучшим образом осуществлял инжекцию электронов в область базы, а коллектор – экстракцию электронов из области базы. Этому же способствует и конструктивная особенность транзистора: площадь перехода база-коллектор существенно больше площади перехода эмиттер-база. Представленные на рисунке 6 структуры соответствуют диффузионным или бездрейфовым транзисторам. В них концентрация примеси в области базы примерно одинакова по объёму, а движение носителей заряда происходит, главным образом, в результате диффузии. В

11

дрейфовых транзисторах внутри базы создают области с различной концентрацией примеси. Возникающее при этом дополнительное электрическое поле существенным образом влияет на скорость перемещения носителей заряда (дрейф) и увеличивает быстродействие транзистора.

Iвх |

|

Rвх |

|

|

Iвых |

|

Rк |

|

||

|

|

|

|

|

|

|

|

|

||

Uвх |

|

|

|

|

|

|

|

|

|

Uп |

|

|

|

|

|

Yвых |

Uвых |

||||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||

|

KU Uвых |

|

|

|

|

|

|

|

||

|

KI Iвх |

|

|

|

|

|||||

Рисунок 7. Схема замещения в виде четырёхполюсника Система уравнений :

Uвх = Iвх Rвх + Uвых Ku,

|

Iвых = Iвх KI + Uвых Yвых, |

|

где Rвх |

= dUвх/dIвх |

(определяется в режиме к.з.), |

Yвых = dIвых/dUвых |

(определяется в режиме х.х), |

|

Ku |

= dUвх/dUвых |

(коэффициент обратной связи по напряжению, |

|

|

определяется в режиме х. х), |

KI |

= dIвых/dIвх |

(коэффициент усиления по току, определяется в |

|

|

режиме к.з.). |

- дифференциальные характеристики.

Iвх |

|

Iвых |

Iвх= const |

|

|

||

|

Uк2> Uк1 |

|

|

Uк1=0 |

|

|

|

|

Uвх |

|

Uвых |

|

|

|

|

|

|

1 В |

|

0,6 В |

|

|

|

Uвых |

Насыщение б-э |

|

5 В |

перехода |

|

|

Насыщение б-к |

|

0,5 В |

перехода |

|

|

|

|

0,6 В |

1,2 В |

Uвх |

|

||

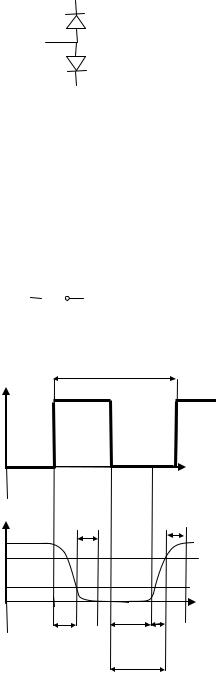

Входная характеристика |

Выходная характеристика |

Передаточная характеристика |

Рисунок 8. Вольтамперные характеристики биполярного транзистора Сдвиг входной характеристики вправо при увеличении напряжения

коллектор – эмиттер объясняется модуляцией (изменением ширины) области базы под действием потенциала коллектора и называется эффектом Эрли.

Коллектор

Iб

n2

База

Uкэ

p

n1

Uбэ |

Эмиттер |

|

12

Рисунок 9. Иллюстрация эффекта Эрли.

Нулевое значение сигнала на выходе биполярного ключа определяется открытым состоянием транзистора. На вход подаётся потенциал высокого уровня. При этом по мере увеличения входного тока, нарастает концентрация электронов в области базы, увеличивается выходной ток (IвхKI) и уменьшается напряжение на коллекторе (Uвых = Uп – IвыхRк), в то время как напряжение базы (Uвх) остаётся, практически постоянным (входная характеристика). Когда напряжение базы становится больше напряжения коллектора на 0,6 В база - коллекторный pn – переход также открывается. Это, в свою очередь, дополнительно увеличивает концентрацию электронов в области базы.

Коллектор

База

Эмиттер

Рисунок 9.а «Диодная» схема замещения обратного биполярного транзистора

Единичное значение сигнала на выходе ключа формируется подачей нулевого потенциала на вход (переключение транзистора в закрытое состояние) по мере того, как рассасывается заряд в области базы.

Рассмотренный биполярный насыщенный ключ является простейшим логическим элементом, выполняет операцию «НЕ» и называется инвертором.

Uвх |

|

Uвых |

|

||

|

|

|

Рисунок 10. Условное обозначение инвертора

Tmin

Uвх

5 В

Uвых

2 В

0,8 В

t 0 min |

t 1 min |

t нар.конц неосн нос заряда в обл.

базы = t обр фронта

Uвх

t расс. t нараст. сигнала

t фронта

13

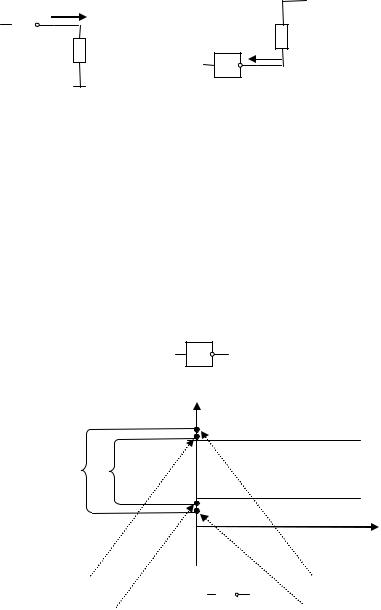

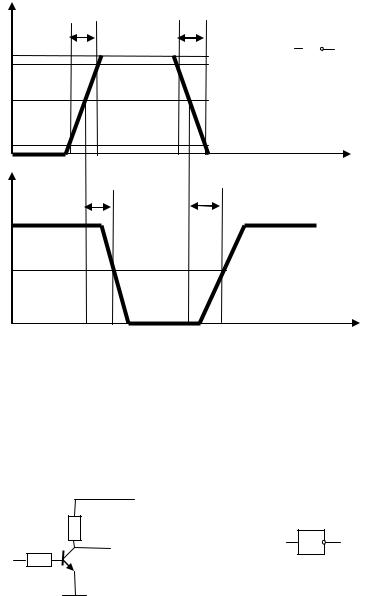

Рисунок 11. Прохождение П-образного импульса через РТЛ-инвертор Повышенная концентрация неосновных носителей заряда в области базы (высокая степень насыщения) ограничивает частотные свойства РТЛ –

инвертора :

fmax = 1/Tmin

Tmin ≥ tобр фронта + t0min + tобр фронта + t1min

Основные параметры логических элементов (на примере инвертора)

1. Токи (инвертор работает на элемент ДТЛ)

I«1» max << I «0» max |

|

||

0 |

1 I«1» |

Uп |

|

|

|||

|

|

1 |

0 |

|

|

||

I«0»

Рисунок 12. Нагрузочные токи логического элемента

2. Напряжения

Для повышения помехоустойчивости выдерживаются следующие соотношения (для ТТЛ-уровней):

2В <= Uвх «1» min < Uвых «1» min Uвых «0» max < Uвх «0» max <= 0,8 В

Говорят, что «выходные» напряжения должны быть «лучше» входных, т.е. интервал выходных напряжений является охватывающим для интервала входных напряжений.

2 В < Uвх1 min < Uвых1 min

0,8 В > Uвх0 max > Uвых0 max

u

2 В

выходные входные

0,8 В

t

Uвх «1» min |

|

Uвых «1» min |

Uвх «0» max |

|

Uвых «0» max |

|

Рисунок 13. Соотношения для входных и выходных напряжений

14

Разница U-пом= Uвых «1» min - Uвх «1» min и U+пом= Uвх «0» max - Uвых «0» max

характеризует, соответственно, допустимую отрицательную и положительную помехи.

3. Быстродействие

Предельно абстрактно работу цифрового элемента можно рассматривать, как прохождение через него П-образного прямоугольного импульса напряжения. В реальности и входные и выходные кривые напряжений имеют профиль, заметно отличающийся от прямоугольного.

Некоторым компромиссным решением являются т.н. диаграммы в измерительных уровнях, на которых кривые напряжений апроксимируются трапециями.

Uвх |

t фронта |

|

t спада |

|

|

|

|

|

|

|

|||

U1 |

|

|

|

0,9U1 |

|

|

|

|

|

|

|

||

0,5(U0+U1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0,1U1 |

|

t |

U0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвх |

t 10 |

|

t 01 |

|

|

|

|

|

|

|

|||

0,5(U0+U1)

t зад = 0,5(t10+t01) t

Рисунок 14. Диаграммы в измерительных уровнях Таким образом, частотные свойства цифрового элемента определяют,

в-основном, по времени задержки. t зад = 0,5(t10+t01)

1.1.1 РТЛ - инвертор

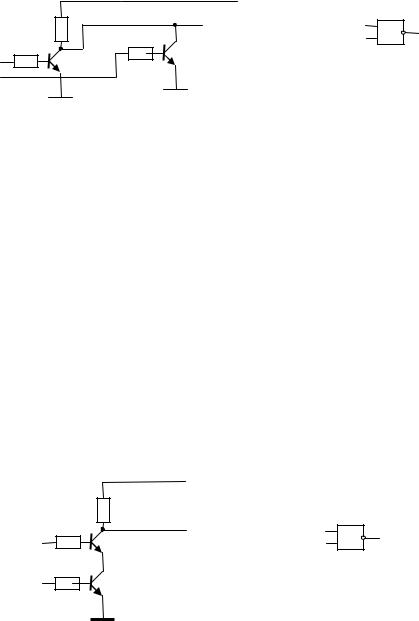

Инвертор резисторно-транзисторной логики содержит один npn – транзистор по схеме с общим эмиттером.

|

+Uп |

|

|

|

Rк |

|

|

Rб |

y |

х |

y |

|

|

|

|

х |

|

|

|

|

VT |

|

|

а) |

б) |

|

Рисунок 15. Упрощенная схема (а) и обозначение(б) РТЛинвертора

15

1.1.2 РТЛ элемент 2ИЛИ-НЕ

Базисный элемент 2ИЛИ-НЕ (стрелка Пирса) резисторнотранзисторной логики содержит два npn – транзистора.

+Uп

|

Rк |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

y |

|

|

|

x0 |

1 |

y |

|

|

|

|

|

|

|

|

Rб2 |

|

|

|

|

|||||

|

Rб1 |

|

|

|

|

|

|

x1 |

|

|

||||||

|

|

|

|

|

|

VT2 |

|

|

|

|

|

|||||

x0 |

|

|

|

VT1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

x1 |

|

|

|

|

|

|

|

|

|

|

б) |

|

|

|||

|

|

|

|

а) |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

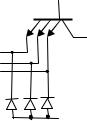

Рисунок 16. Упрощенная схема (а) и обозначение (б) РТЛ 2ИЛИ-НЕ |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2 |

|

|

|

|

Таблица состояний элемента 2ИЛИ-НЕ |

|

|||||||||||

|

|

|

|

|

|

|

|

|

x1 |

|

x0 |

y |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

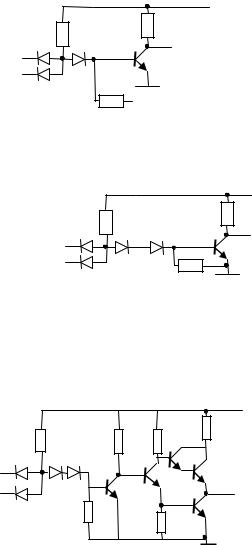

1.1.3 РТЛ элемент 2И-НЕ |

|

|

|

|

|

|

||||||||||

Базисный элемент 2И-НЕ |

(штрих Шеффера) |

резисторно- |

||||||||||||||

транзисторной логики также содержит два npn – транзистора. |

||||||||||||||||

|

|

|

|

Rк |

|

|

+Uп |

|

|

|

|

|

|

|||

|

|

|

|

Rб1 |

|

|

|

|

|

x0 |

& |

y |

|

|||

|

x0 |

|

|

|

|

|

|

|

|

|

||||||

|

|

VT1 |

|

|

y |

|

x1 |

|

||||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

x1 |

Rб2 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

VT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

а) |

|

|

|

|

|

|

|

б) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рисунок 17. Упрощенная схема (а) и обозначение (б) РТЛ 2И-НЕ

Таблица 3

Таблица состояний элемента 2И-НЕ

x1 |

x0 |

y |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

16

Элементы 2И-НЕ и 2ИЛИ-НЕ представляют собой базис для синтеза цифровых схем, так как на каждом из них можно реализовать все три основные логические функции: конъюнкции, дизъюнкции и инверсии, а значит, и синтезировать любую передаточную функцию.

1.1.4 ДТЛ элемент 2И-НЕ

В ДТЛ – элементе 2И-НЕ при подаче на оба входа высоких уровней напряжения делителем R1-Rсм формируется Uб > 0,6 В, обеспечивая открытое и насыщенное состояние транзистора. При подаче низкого уровня сигнала на один или оба входа напряжением смещения формируется Uб < 0,6В, что надёжно удерживает транзистор в режиме отсечки. Переключающим в ДТЛ – логике является сигнал низкого уровня, который характеризуется меньшим «дребезгом контактов» (удобно представить переключение ключевого транзистора из состояния хх входного сигнала).

+Uп

|

R1 |

Rк |

|

|

|

VD1 |

|

y |

x1 |

|

|

x2 |

|

|

VD2 |

|

Rсм |

|

-Ucм |

|

|

|

Рисунок 18. Упрощенная схема ДТЛ 2И-НЕ С небольшими изменениями схема ДТЛ может выглядеть следующим

образом:

|

|

|

+Uп |

|

|

1,6К |

160 |

|

|

|

|

|

VD1 |

|

y |

x1 |

|

|

|

|

|

|

|

x2 |

|

|

|

|

VD2 |

|

1 К |

|

|

|

Рисунок 19. Модифицированный элемент ДТЛ В схеме на рисунке 19 два изменения: дополнительный

последовательный диод в цепи базы и сопротивление в 1 К, шунтирующее база – эмиттерный переход. Для ориентации приведены номиналы резисторов.

+Uп

VT1

VT2

y

… (до 6 входов)

Рисунок 20. Пример серийной микросхемы ДТЛ серии К109

17

В схеме на рисунке 20 транзисторы VT1 и VT2 образуют т.н. «схему Дарлингтона» (иногда говорят: транзистор Дарлингтона), которая характеризуется большей величиной выходного тока (результирующий коэффициент усиления по току определяется, как произведение коэффициентов, составляющих схему). Особенность транзистора Дарлингтона в том, что напряжение между базой и эмиттером (в открытом состоянии) в два раза больше обычного, а напряжение насыщения равно, по крайней мере, падению напряжения на диоде (так как потенциал эмиттера транзистора VТ1 должен превышать потенциал эмиттера транзистора VТ2, на величину падения напряжения на диоде).

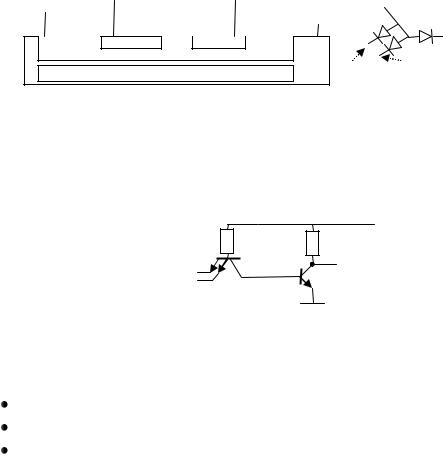

1.1.5 ТТЛ элемент 2И-НЕ

Если в конструкции биполярного транзистора предусмотреть не один, а несколько эмиттеров (обычно 5-8), появляется возможность использовать его в качестве входного каскада. Этим существенно упрощается и удешевляется схема логических элементов, использующих такого рода многоэмиттерный транзистор (МЭТ).

База |

Эмиттер1 |

Эмиттер2 |

Коллектор |

База |

|

|

|||

|

|

|

|

Коллектор |

p |

n1 |

n1 |

|

|

|

|

|

n2 |

Эмиттер2 |

|

n+ |

|

Эмиттер1 |

Рисунок 21. Много эмитерный npn - транзистор

Для исключения паразитных горизонтальных цепочек эмиттер1- база-эмиттер2 расстояния между соседними эмиттерами выполняют больше, чем диффузионная длина носителей заряда в базовом слое.

|

|

+Uп |

|

R1 |

Rк |

|

|

|

|

VT1 |

y |

x1 |

|

|

|

|

|

x2 |

|

VT2 |

|

|

Рисунок 22. Упрощенная схема элемента ТТЛ 2И-НЕ Схема на рисунке 22 называется схемой с простым инвертором и

обладает существенными недостатками: низкая помехоустойчивость; малая нагрузочная способность;

ограниченное быстродействие при работе на емкостную нагрузку.

Быстродействие логического элемента в значительной степени

определяется продолжительностью t01 |

– |

переключения транзистора из |

открытого режима в режим отсечки. |

В |

действительности транзистор |

|

|

18 |

начинает закрываться в тот момент, когда по внешней цепи осуществится рассасывание избыточного заряда в области базы. А время задержки в закрывании напрямую связано с концентрацией электронов в области базы, т.е. со степенью насыщения база – эмиттерного (в – первую очередь) и база– коллекторного (во – вторую) переходов.

Улучшить частотные свойства элемента позволяет включение т.н. добавочного транзистора.

+Uп

|

R1 |

Rк |

|

|

|

|

VT1 |

y |

x1 |

|

|

|

|

|

x2 |

|

VT2 |

|

|

|

|

R3 |

R4 |

VT3

Рисунок 23.Схема ТТЛ – элемента с добавочным транзистором Особенностью схемы является подбор сопротивлений R3 >> R4(т.е.

много больше). При увеличении напряжения на коллекторе VT1(на всех входах высокий уровень) первым открывается транзистор VT2 (в его базу втекает весь ток и поэтому задержки в открытии из-за дополнительной цепи R3, б-э VT3 не происходит). Затем открывается дополнительный транзистор и цепью R4(относительно малого номинала), к-э VT3 шунтирует б-э переход ключевого транзистора, тем самым ограничивая его насыщение.

Дальнейшим развитием ТТЛ - элемента является схема со сложным инвертором или двуполярный ключ (рисунок 24).

|

|

|

R4 |

+Uп |

|

|

|

|

130 |

||

R1 |

4к |

R2 |

1,6к |

||

|

|||||

|

VT1 |

|

|

VT3 |

|

|

|

|

|

||

x0 |

|

|

|

VD |

|

|

VT2 |

|

|

||

x1 |

|

|

y |

||

|

|

|

|||

x2 |

|

R3 |

1к |

VT4 |

|

|

|

|

|||

|

|

|

|

Рисунок 24. Схема со сложным инвертором Структурно схема состоит из трёх блоков:

входной МЭТ (VT1), фазорасщепительный блок (VT2), двухтактный выходной каскад (VT3, VT4).

При подаче 0В хотя бы на один из входов, VT1 открывается и на его базе формируется напряжение Uб VT1 ~ 0,8 В. Этого напряжения не хватает, чтобы открыть три последовательно включённых p-n перехода: б-к VT1, б-э VT2,

б-э VT4 (для этого нужно не менее 0,6 х 3 = 1,8 В). Следовательно, транзистор VT2 закрыт, на базе транзистора VT4 потенциал земли (0 В) и он

19

также закрыт. При этом на коллекторе VT2 (и базе VT3) напряжение, близкое источнику питания Uп = 5В, поэтому транзистор VT3 и диод VD открыты, обеспечивая выходной ток и выходное напряжение Uвых1 > Uвых1 min.

При подаче на все входы Uвх1 увеличивается напряжение на базе VT1 и при его значении в районе 1,2 В открывается б-к переход VT1 и б-э переход VT2. Ток на резисторе R2 увеличивается, снижая напряжение на базе VT3. При этом увеличивающийся ток на резисторе R3 поднимает напряжение на базе VT4 и он открывается. Открывшийся транзистор VT4 шунтирует R3 и ещё больше увеличивает ток через R2. Транзистор VT3 начинает закрываться. В промежуток времени, когда открыты оба транзистора (VT4 и VT3) ток короткого замыкания ограничивается R4 и сопротивлениями VT3, VD, VT4. Затем VT2 и VT4 достигают стадии насыщения. В этом режиме разности напряжений коллектора VT2 (менее 1,2 В ) и коллектора VT4 (около 0,3 В) ∆U< 0,9 В не хватает, чтобы открыть б-э переход VT3 и VD. По этой причине VT3 надёжно заперт и на выходе Uвых0 ~ 0,3 В.

Таким образом, формирование прямого (VT3) и обратного(VT4) фронтов выходного сигнала выполняется путём открытия разных транзисторов и задержки в формировании фронтов связаны, в-основном, с нарастанием концентрации неосновных носителей в базе.

Для ограничения перенапряжений на входах многоэмиттерного транзистора в отрицательной зоне напряжений ~ до – (0,6 ÷ 0,8) В в схему добавлены демпфирующие диоды.

x0

x1

x2

Рисунок 25. Включение демпфирующих диодов.

1.1.6 ТТЛШ – элемент |

|

Способом увеличения рабочей |

частоты элемента является |

ограничение процесса открытия транзистора только первой стадией: открытием перехода база – эмиттер. Для этого между базой и коллектором транзистора выходного (формирующего) каскада элемента ТТЛ подключают особого вида вентиль - диод Шоттки (иначе его называют выпрямляющим контактом). По той причине, что диод Шоттки при нарастании положительной разности потенциала база-коллектор отрывается первым, он своим током ограничивает превышение потенциала базы над потенциалом коллектора уровнем 0,2-0,3 В. Очевидно, что такого напряжения недостаточно для отпирания база-коллекторного pn – перехода. Схема, полученная таким образом, получила аббревиатуру ТТЛШ.

20