конмпект лекций

.pdf

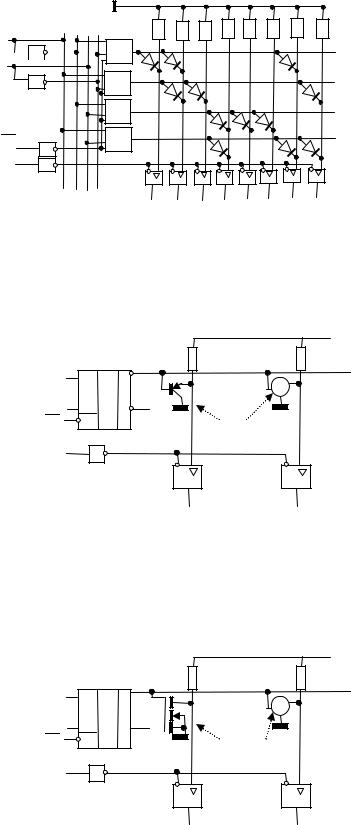

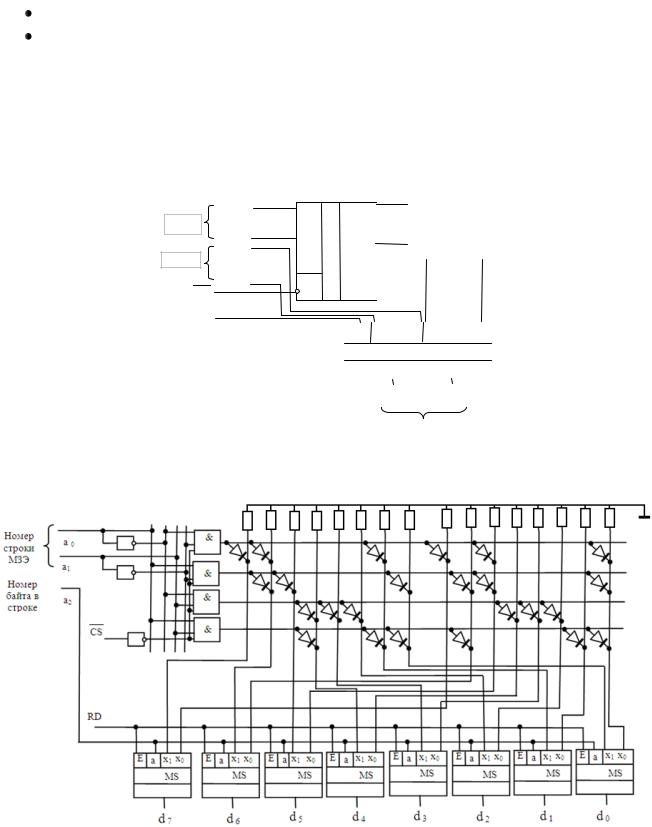

a 0

&

a1

&

&

CS |

& |

RD |

|

d7 |

d6 d5 d4 d3 d2 d1 d0 |

Рисунок 80. Схема диодной ROMМ 4 × 8

На первом этапе изготовления МЗЭ, как следует из схемы, заполняется единицами.

2.3.4.1 Упрощенные схемы масочных ROM 2D устройств

+Uп

|

y0 |

|

a0 |

DC |

|

… |

n |

|

an-1 |

y2 - 1 |

|

|

|

|

CS |

pnp |

|

RD |

ym-1 |

y0 |

|

||

|

dm-1 |

d0 |

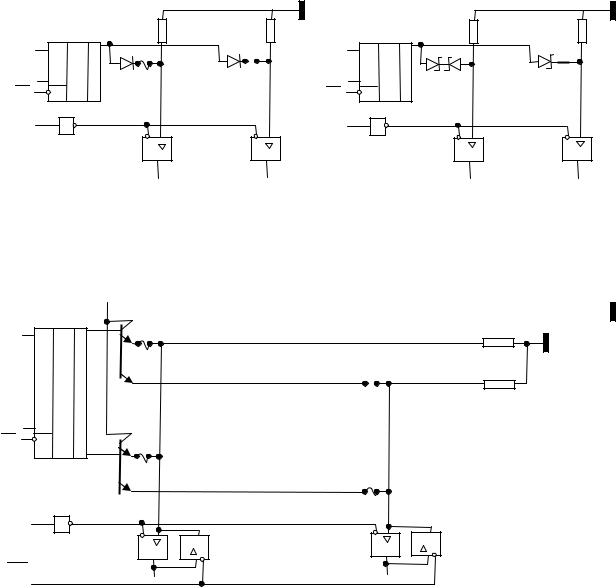

Рисунок 81. Структура биполярной транзисторной ROMM памяти Особенность транзисторной ROMM памяти заключается в том, что при

изготовлении МЗЭ она оказывается заполненной нулями. После этапа выжигания отсутствующий транзистор соответствует записанной в память «единице». Как следует из схемы, в данном случае используется дешифратор с инверсными выходами.

|

|

+Uп |

|

y0 |

|

a0 |

DC |

|

… |

|

|

an-1 |

|

|

CS |

n-МОП |

|

RD |

ym-1 |

y0 |

|

||

|

dm-1 |

d0 |

Рисунок 82. Структура ROMM памяти на МОП - транзисторах

Для ROMM на базе МОП – транзисторов вместо выжигания чаще используют иной приём технологического программирования – изготовление соответствующих транзисторов (там, где должна быть размещена единица) сразу на первом этапе с увеличенной толщиной подзатворного окисла. В

51

этом случае положительного потенциала на линии выборки оказывается недостаточно для формирования n-канала и транзистор остаётся в закрытом состоянии.

2.3.4.2 Упрощенные схемы PROM 2D устройств памяти

PROM – микросхемы памяти при изготовлении также оказываются заполненными единицами или нулями (все горизонтальные и вертикальные линии МЗЭ электрически связываются соответствующими элементами). Программирование микросхем выполняется с помощью сравнительно недорогих устройств – программаторов и сводится к удалению конкретных электрических связей.

Наиболее простые схемы имеют PROM – устройства на базе диодных

схем.

|

y0 |

|

y0 |

a0 |

DC |

a0 |

DC |

|

… |

|

|

|

… |

|

|

an-1 |

|

|

|

an-1 |

|

CS |

|

|

|

CS |

|

|

RD |

|

ym-1 |

y0 |

RD |

ym-1 |

y0 |

|

|

|

||||

|

|

dm-1 |

d0 |

|

dm-1 |

d0 |

а) Схема с высокоомной перемычкой |

|

|

б) Схема с встречновключёнными |

|

||

|

|

|

|

|

диодами |

|

|

|

Рисунок 83. PROM на основе диодных схем |

|

|||

|

|

+Uп |

|

|

|

|

a0 |

DC |

y0 |

|

|

|

|

… |

|

|

|

|

|

|

|

|

… |

|

|

|

|

|

|

|

|

|

|

|

…

an-1

CS

y2n-1

zm-1 |

z0 |

RD

…

EF |

dm-1 |

d0 |

|

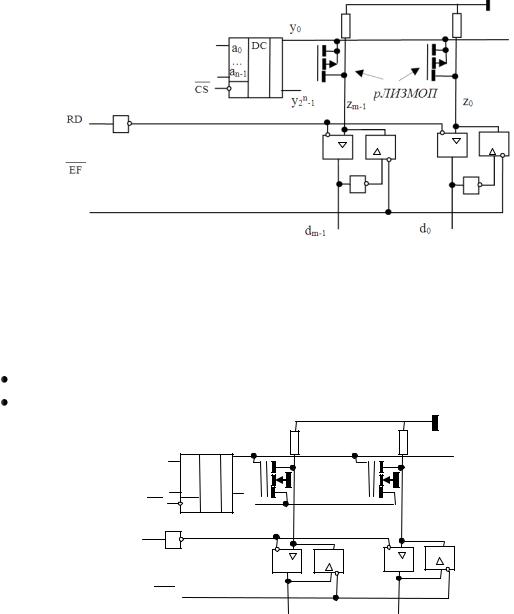

Рисунок 84. PROM на базе МЭТ

52

В микросхемах памяти на базе многоэмиттерных транзисторов количество эмиттеров соответствует разрядности кодового слова, а количество транзисторов – количеству кодовых слов. Двунаправленный буфер используется для программирования микросхемы. Для этого на адресные входы подаётся двоичное значение, соответствующее номеру выбранной ячейки памяти, на линии данных подаётся записываемое значение, управляющие сигналы устанавливают в следующие значения

CS=0, RD=0, EF=0.

2.3.4.3 Упрощенная схема EPROM 2D памяти

EPROM – микросхемы памяти изготавливались на базе ЛИЗМОП – транзисторов, плавающий затвор которых представлял собой слой, как правило, поликристаллического кремния. Количество циклов перезаписи постепенно было доведено до 100. В режиме программирования на d-линии микросхемы сигналы подаются в инверсном коде.

Рисунок 85. Стираемая УФО EPROM – память.

2.3.4.4 Упрощенные схемы EEPROM 2D устройств памяти

EEPROM устройства в настоящее время производятся по одной из двух технологий:

На базе двухзатворных n-ЛИЗМОП; На базе МНОП – структур.

y0

a0 DC

…

an-1

CS |

+Uп |

|

|

|

zm-1 |

z0 |

|

|

|

RD

EF

dm-1 |

d0 |

53

Рисунок 86. EEPROM память на базе двухзатворных nЛИЗМОП Отрицательный остаточный заряд плавающего затвора в данном случае

выполняет противоположную функцию: экранирует положительный потенциал линии адреса, в результате чего транзистор остаётся в закрытом состоянии, обеспечивая на выходной линии нулевой потенциал. В режиме программирования по линиям d0 – dm-1 необходимо подавать исходные значения.

Схема устройств памяти на базе МНОП – транзисторов не отличается от представленной на рис. 86.

Рассмотренные технологии изготовления EEPROM памяти гарантируют 104 – 106 циклов перезаписи.

|

Si3N4 |

|

затвор |

сток |

исток |

|

SiO2 |

n |

n |

|

p |

подложка

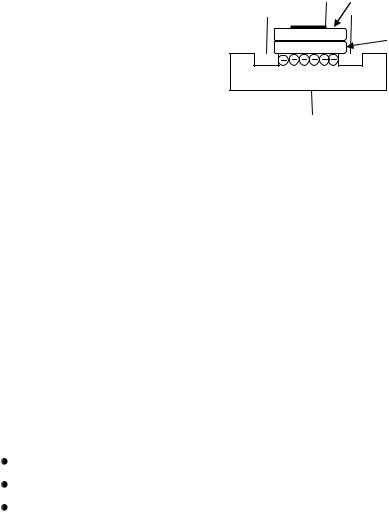

Рисунок 87. Упрощенная схема nМНОП - транзистора

2.3.4.5 Страта –флэш устройства

Flash – устройства памяти выполняются на основе технологии EEPROM со следующими особенностями:

Стирание ранее записанной информации выполняется поблочно. Сам термин flash и происходит от этой особенности: первоначально используемые устройства для хранения секретной информации автоматически стирали всю матрицу при попытке несанкционированного доступа. Размер блоков варьируется от 256 байт до 128 К.

Стирание ранее записанной информации выполняется поблочно. Сам термин flash и происходит от этой особенности: первоначально используемые устройства для хранения секретной информации автоматически стирали всю матрицу при попытке несанкционированного доступа. Размер блоков варьируется от 256 байт до 128 К.

Специальные алгоритмы разравнивания оптимизируют количество перезаписей в разных блоках матрицы.

Специальные алгоритмы разравнивания оптимизируют количество перезаписей в разных блоках матрицы.

Страта-флэш (strata-flash) устройство памяти характеризуется тем, что один запоминающий элемент способен хранить 2 бита данных и состоит из:

двухзатворного ЛИЗМОП – транзистора, аналогового компаратора,

выходной комбинационной схемы, преобразующий сигнал в двухразрядное двоичное значение.

54

|

|

|

|

Аналоговый |

Преобразователь кода |

|||||

y0 |

компаратор |

|||||||||

|

|

|

||||||||

|

Iвых |

|

|

c2 |

|

|

d0 |

|||

|

|

|

|

|

||||||

|

|

|

|

|

|

c1 |

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

c0 |

|

|

d1 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

+Uп

Источник эталонных токов

` I0 <I1 <I2

Рисунок 88. Структура страта-флэш усройства Плавающий затвор n-ЛИЗМОП транзистора заряжают одним из 3-х

уровней потенциала (четвёртым уровнем является разряженное состояние затвора). От этого зависит степень экранирования потенциала основного затвора (в режиме выбора данного запоминающего элемента h – уровнем на линии y0) и, соответственно, значение тока Iвых. Далее этот ток сравнивается с с тремя эталонными значениями токов и формируются выходные сигналы.

Таблица 16

Формирование сигналов

Соотношение токов |

c2 |

c1 |

c0 |

d1 |

d0 |

||

Iвых < I0< I1< I2 |

0 |

0 |

0 |

0 |

0 |

||

I0 |

<Iвых < I1< I2 |

0 |

0 |

1 |

0 |

1 |

|

I0 |

< I1 |

<Iвых < I2 |

0 |

1 |

1 |

1 |

0 |

I0 |

< I1 |

< I2<Iвых |

1 |

1 |

1 |

1 |

1 |

Примечание. Разработайте схему преобразователя кода для страта-флэш памяти.

2.3.5 Запоминающие устройства с селектором данных (2DM)

Изготовление микросхем одномерной памяти сопряжено со сложностью в изготовлении дешифратора адреса. Действительно, любой дешифратор состоит из двух частей :

-схема расщепления входных сигналов на парафазный код;

-схема объединения соответствующих сигналов (или их инверсий) на выходном элементе ИЛИ (или ИЛИ-НЕ).

Сростом объема микросхемы увеличивается количество адресных линий и вместе с тем размерность выходного элемента:

|

|

|

|

|

|

|

|

|

|

|

|

|

x0 |

|

|

|

y0 |

|

|

|

|

|

|

|

x0 |

|

|

|

y0 |

|

x1 |

& |

|

|

|

|

x0 |

|

|

y0 |

|

x1 |

& |

|

|

|

x2 |

|

|

|

|

||

|

|

|

& |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

x1 |

|

|

|

x2 |

|

|

|

|

… |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

E |

|

|

|

|

E |

|

|

|

|

xn-1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

E |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

а) DC на два входа |

|

б) DC на три входа |

|

в) DC на n - входов |

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Рисунок 89. Изменение выходного каскада дешифратора

55

Кроме этого, с добавлением адресной линии у дешифратора удваивается количество выходных коньюнкторов.

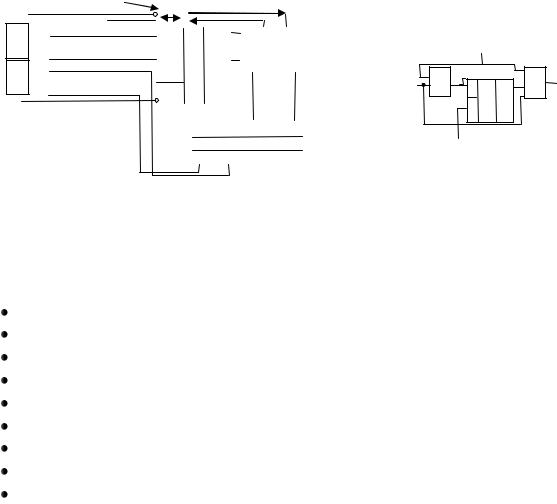

С целью упрощения дешифратора адреса в состав микросхемы памяти включают дополнительный мультиплексор (селектор). При этом n адресных линий разделяются на две группы:

r линий, которые по-прежнему подаются на дешифратор; k = n – r линий, которые управляют селектором.

Таким образом, дешифратор упрощается на k линий. При этом на селектор могут быть поданы, как старшие, так и младшие линии адреса. Селектор данных, обозначенный на структурной схеме (рис. 90), как S, выполняется из m мультиплексоров (по одному на выходную линию) на k адресных входов каждый. Характерно, что МЗЭ имеет формат, не совпадающий с исходным форматом микросхемы.

линий шины |

адреса: |

n – |

|

a0

r линий |

|

|

ar-1 |

k линий |

ar |

|

|

|

ar+k-1 |

CS

RD

a0 |

x0 |

|

|

|

… DC |

|

|

|

|

… |

|

|

МЗЭ |

|

ar-1 |

x2r-1 |

|

2r x (m*2k) |

|

|

|

|

||

|

|

|

|

|

E |

|

ym*2k - 1 |

. . . y0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

E ak-1 … a0 |

|

||

|

|

|

|

S |

|

|

|

|

|

|

|

d m-1 ... |

d0 |

|

|

|

m – линий шины |

||

|

|

|

данных |

|

Рисунок 90.Структурная схема ROM формата 2n × m с селектором данных

Рисунок 91. Схема ROM 2DM 8х8.

56

Карта памяти для микросхемы на рисунке соответствует следующему содержимому:

адрес |

содержимое |

000b |

10100001b |

001b |

01100001b |

010b |

00011100b |

011b |

01000011b |

100b |

11000010b |

101b |

01100001b |

110b |

00011100b |

111b |

00010011b |

Рисунок 92. Содержимое микросхемы

2.3.6Запоминающие устройства с двумерной адресацией (3D)

Вкачестве запоминающего устройства с двумерной адресацией рассматривается статическая RAM 2n x 1.

Двунаправленный буфер

WR/RD |

A0 |

di |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

:адреса n/2 |

линий |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

an/2-1 |

|

|

|

x2 -1 |

|

|

|

|

|

|||||||||

|

|

|

|

… |

… |

a0 |

DC |

x0 |

|

|

МЗЭ |

|||||||

|

|

|

|

|

|

… |

|

|

|

|

|

|||||||

|

|

|

|

An/2-1 |

|

|

|

|

|

… |

|

|

n/2 |

n/2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

n/2 |

|

|

2 |

x2 x 1 |

||

Шина n/2 |

линий |

An/2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

… |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

An-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y2 |

n/2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-1 |

… |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DC |

|

|

|

|

|

|

|

|

|

|

|

|

|

an/2-1…a0 |

|

|

|

|||

а) Структурная схема

Выборстолбца |

|

Выбор строки |

|

D |

|

данных |

|

|

& |

|

& |

|

C |

Т Q |

|

|

|

|

Выход |

|

Вход данных |

|

|

б) Упрощенная схема запоминающего элемента на базе D-триггера

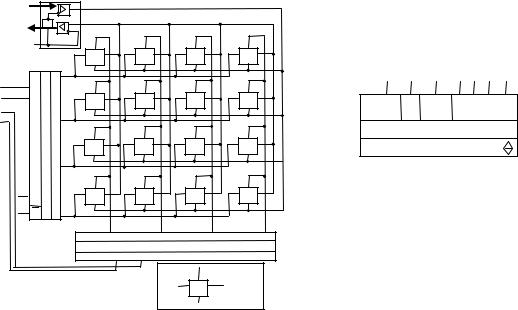

Рисунок 93. RAM 2n x 1 На рисунке 93 обозначены:

WR/RD – сигнал "запись (1) / чтение (0)"; n - разрядность шины адреса ;

Аj - линия шины адреса; DC – дешифратор адреса;

n/2 - количество входов дешифратора адреса; МЗЭ – матрица запоминающих элементов; 2n/2 – количество строк или столбцов МЗЭ

di – линия шины данных;

CS – сигнал "выбор кристалла";

57

Двунаправленный буфер – схема из двух буферов с высокоимпедансными состояниями, обеспечивающая передачу сигнала в противоположных направлениях.

Упрощенная схема SRAM 16 х 1 представлена на следующем рисунке.

d i |

|

|

|

|

d' i |

|

|

|

|

WR/RD |

|

|

|

|

1- записать, |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

0- прочитать |

a 0 |

|

DC y 0 |

|

|

|

|

|

|

x0 |

|

|

|

|

|

|

a 1 |

x1 |

|

|

|

ЗЭ |

|

|

a 2 |

ЗЭ |

ЗЭ |

ЗЭ |

WR/RD CS di |

a3 a2 a1 a0 |

||

|

|

|

|

|

|||

a 3 |

|

y 1 |

|

|

|

|

|

RAM

|

ЗЭ |

ЗЭ |

ЗЭ |

|

ЗЭ |

d'i |

|

y 2 |

|

|

|

|

|

|

ЗЭ |

ЗЭ |

ЗЭ |

|

ЗЭ |

|

CS |

|

|

|

|

|

|

E |

y 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

y 0 |

y 1 |

|

y 2 |

y 3 |

|

|

|

|

|

|

DC |

|

|

x1 |

x0 |

|

|

|

|

|

|

|

|

Выбор |

|

|

|

|

Выбор |

|

столбца |

|

|

|

Назначение выводов |

строки |

ЗЭ |

Выход данных |

|

|

|

|

|

|

|

||

запоминающего элемента : |

|

Вход данных |

|

|

||

|

|

|

|

|

|

|

|

а) упрощенная схема |

|

б) условное обозначение |

|||

|

|

|

||||

Рисунок 94. SRAM 16 х 1

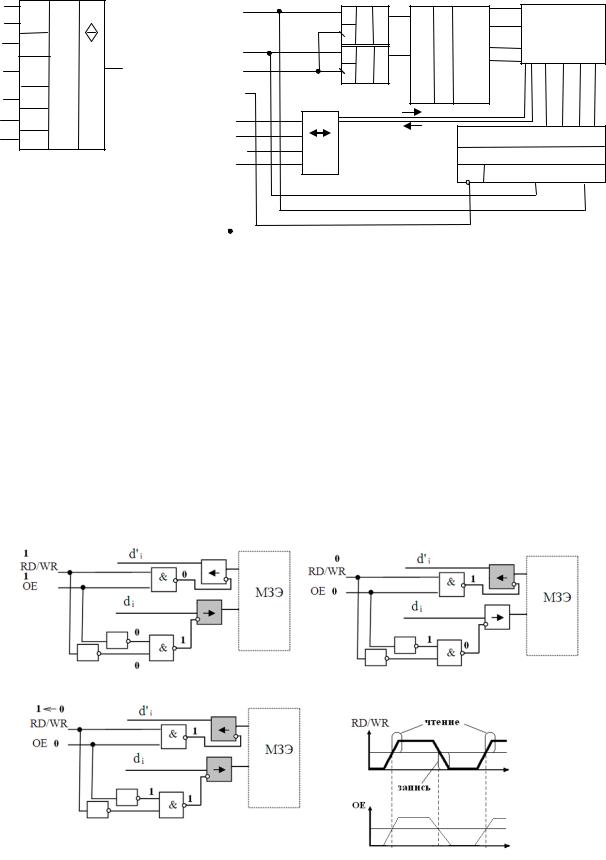

2.3.7 Устройства памяти с мультиплексированием адресного слова

Количество адресных входов микросхем 3D - памяти может быть существенно уменьшено, если адреса строк и столбцов для квадратной МЗЭ передавать поочерёдно. В общем случае для n – разрядного адреса количество входов уменьшается на n/2 - 1. Эффект несколько меньше, чем двукратный за счёт того, что добавляется одна управляющая линия. Первым полуадресом является адрес строки в МЗЭ (как правило, младшая половина адресного слова). Для того, чтобы сохранить это значение до момента передачи второго полуадреса, в состав микросхемы включают регистр – защёлку адреса:

58

a0 |

|

|

|

a0 |

D |

T Q |

x0 DC |

y0 |

|

|

|

|

|

a1 |

SRAM |

|

|

|

|

МЗЭ |

|

||||||

|

|

|

C |

|

|

|

y1 |

|

|

||||

|

|

|

|

|

|

|

|

|

|||||

d i |

|

|

|

a1 |

|

|

|

|

y2 |

|

4x4 |

|

|

|

|

|

D |

T |

Q |

x |

|

|

|

|

|||

|

|

|

|

|

|

1 |

|

|

|

|

|

||

RAS |

|

|

RAS |

C |

|

|

|

y3 |

|

|

|

|

|

|

d` i |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAS |

|

|

|

|

|

|

|

|

|

||

CAS |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RD/WR |

|

|

d i |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y2 |

|

|

|

OЕ |

|

|

d` |

i |

|

|

|

|

|

y3 |

y1 |

y |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

||

|

|

|

RD/WR |

|

|

|

|

|

|

|

DC |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

OE |

|

|

|

|

E |

x1 |

|

x0 |

|

|

a) Обозначение |

b) Структурная схема |

Рисунок 95. SRAM 16х1 с мультиплексированием адресного слова

В реальных микросхемах RAM – памяти линия выбора режима (чтения или записи), как правило, единая и называется линия RD/WR. При этом режим чтения активизируется единичным, а записи - нулевым значением управляющего сигнала, или, соответственно, прямым или обратным фронтом импульса. Для того, чтобы в режиме записи не происходило нежелательного подключения выходной линии матрицы запоминающих элементов на шину данных по прямому фронту сигнала RD/WR (при восстановлении единичного, запрещающего сигнала) в микросхему добавляют еще один управляющий вход ОЕ (output enable)– разрешения выхода.

Рисунок . Управление двунаправленным буфером микросхемы RAM – памяти дополнительным сигналом ОЕ

59

3 Периферийные устройства МПС

Эффективная работа микропроцессорных систем невозможна без зачастую многочисленных и разнообразных периферийных устройств. Термин «периферийные» классифицирует их расположение в архитектура МПС : их взаимодействие с центральными устройствами ( и , прежде всего, доступ к шинам адреса и данных) осуществляется через посредники – специализированные микросхемы (например, контроллер ввода-вывода, контроллер прерываний и т.п.).

Большая часть периферийных устройств выполняют функции источников или приёмников данных и могут быть объединены в категорию устройств ввода – вывода (УВВ). Внутри этой категории устройства можно классифицировать следующим образом:

Устройства ввода и вывода: накопители на магнитных и магнитооптических дисках, flash – матрицы, модемы, сетевые карты;

Устройства ввода: датчики, переключатели, клавиатура, сканеры, CDROM – диски, аналоговые датчики с аналого-цифровыми преобразователями(АЦП);

Устройства вывода: цифроаналоговые преобразователи (ЦАП), коммутаторы, реле, цифровые (транзисторные) ключи, печатающие и рисующие устройства, дисплеи, светодиодные индикаторы.

Основными параметрами УВВ являются : Разрядность; Быстродействие;

Тип протокола обмена. Физической реализацией протокола обмена является интерфейс – схема, соединяющая системную шину с УВВ . Интерфейс включает в себя порт ввода-вывода (микросхема буферного регистра или контроллер, объединяющий несколько, обычно 4, портов) и схему управления. Для случая отдельного буферного регистра интерфейс схема может выглядеть следующим образом:

УВВ |

d0 |

RG |

D0 |

|

|

К ШД

d7 D7

d7 D7

Приём

Приём

CS

К DC

Рисунок 96. Буферный регистр Порт для подключения УВВ может иметь адрес, как в отдельном, так

и в общем адресном пространстве (т.н. ввод с отображением на память).

60