конмпект лекций

.pdfРисунок 113. Структурная схема МПС на базе I8080

Обозначения на схеме :

ПДП – прямой доступ к памяти, ССИ – семисегментные индикаторы,

ГТИ – генератор тактовых импульсов.

5.3 Состав устройств памяти комплекса Микролаб

Таблица 17

Аппаратное распределение памяти

|

Диапазон адресов |

|

Устройство |

|

|||

|

|

|

|

|

|

|

|

|

0000h – 05FFh |

|

ROM |

|

|||

|

|

|

|

|

|

|

|

|

0600h - 7FFFh |

|

не используется |

|

|||

|

|

|

|

|

|

|

|

|

8000h – 83FFh |

|

RAM |

|

|||

|

|

|

|

|

|

|

|

|

8400h - FFFFh |

|

не используется |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 18 |

||

|

Распределение ROM - памяти |

||||||

|

адрес |

|

содержимое |

|

|||

|

0000h - 003Ah |

|

Программы рестарта |

|

|||

|

0055h |

|

Монитор |

|

|||

|

01А1h |

|

Программа вывода на ССИ |

|

|||

|

01С0h |

|

Программа SEGCG |

|

|||

|

0216h |

|

Программа KEYIN |

|

|||

|

|

|

|

|

Таблица 19 |

||

|

Основные разделы RАM - памяти |

||||||

|

адрес |

|

содержимое |

|

|||

|

8000h-83С5h |

|

Область программ пользователя |

|

|

||

|

83С6h |

|

Стек пользователя ( Дно ) |

|

|||

|

83С7h-83D0h |

|

Стек монитора |

|

|||

|

83D1h-83DFh |

|

Адреса переходов RST |

|

|||

|

… |

|

|

|

|

|

|

|

83E0h-83EBh |

|

Область копирования регистров |

|

|||

|

… |

|

|

|

|

|

|

|

83F4h-83F7h |

|

Данные для SEGCG |

|

|||

|

83F8h-83FFh |

|

Буфер для ССИ |

|

|||

71

a0 … |

|

|

|

|

|

|

a8 |

|

|

|

|

|

|

a9 |

|

|

|

|

|

ША |

a10 … |

|

|

|

|

|

|

a15 |

|

|

y0 |

|

ROM 512х8 |

d0 |

|

|

|

|

|||

|

a |

DC |

y1 |

|

a0 |

… |

|

|

|

|

… |

|

|

|

|

|

|

|

d7 |

|

|

|

|

|

& |

a8 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

ROM 512х8 |

… |

|

|

|

|

|

d0 |

|

… |

1 |

|

|

|

a0 |

… |

|

|

|

|

… |

d7 |

|

|

|

|

|

& |

a8 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CS |

d0 … d7 |

|

|

|

|

|

|

|

MemRD |

|

|

|

|

|

|

|

|

|

|

|

|

ШД |

Рисунок 114 . Организация линейного адресного пространства ROM Таблица 20

Распределение адресного пространства

№ ПЗУ |

Адрес10 |

Адрес16 |

Адрес2 |

|

0 |

0000 |

0000 0000 0000 0000 |

1 |

… |

… |

… |

|

511 |

01FF |

0000 0000 1111 1111 |

|

512 |

0200 |

0000 0011 0000 0000 |

2 |

… |

… |

… |

|

1023 |

03FF |

0000 0011 1111 1111 |

5.4 Организация машинного цикла M1

Как было отмечено ранее, любое действие или операция внутри МПС может быть продолжительностью только целое количество машинных тактов (Т). Интервал времени, необходимый для одного обмена по шине (транзакции) с устройством памяти или ввода – вывода, называется машинным циклом. В зависимости от адресата, назначения и направления обмена существует десять различных машинных циклов:

Машинный цикл |

Назначение |

Содержимое байта состояния |

М1 |

Выборка КОП |

a2h |

М2 |

Чтение из памяти |

82h |

М3 |

Запись в память |

00h |

М4 |

Чтение стека |

86h |

М5 |

Запись в стек |

04h |

М6 |

Ввод из ВУ |

42h |

М7 |

Вывод во ВУ |

10h |

М8 |

Прерывание |

23h |

М9 |

Останов |

8ah |

М10 |

Прерывание при останове |

2bh |

72

Примечание:

1.Если команда однобайтная и безоперандная (или операнды – регистры), в машинном цикле М1 осуществляется и выполнение команды;

2.Цикл М2 следует за М1 для загрузки второго и третьего байта команды, а также операнда(ов) из памяти;

3.Тип машинного цикла идентифицируется байтом состояния, который формируется процессором и передаётся шинному формирователю в такте Т1.

Командным циклом называется набор машинных циклов, необходимый для выполнения одной команды. Как было указано ранее, для однобайтных безоперандных команд и однобайтных команд с регистровой адресацией командный цикл совпадает с машинным циклом М1. Для команды, например

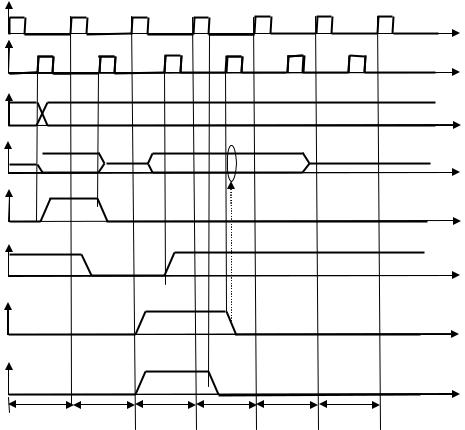

На диаграмме, представленной ниже, воспроизведены сигналы для машинного цикла М1 – выборки и исполнения команды. Машинный такт синхронизируется передним фронтом CL1, а начало микрооперации (действие внутри машинного цикла), как правило, - фронтом CL2.

CL1

t

CL2 |

|

|

|

|

|

|

|

|

|

|

t |

a0 – a15 |

|

|

|

|

|

|

|

|

|

|

t |

|

|

Адрес (PC) |

|

|

|

d0 – d7 |

|

|

|

|

|

|

|

|

|

|

t |

байт состояния |

|

КОП |

|

|

|

SYNC |

|

|

|

|

|

|

|

|

|

|

t |

READY |

|

|

|

|

|

|

|

|

|

|

t |

DBIN |

|

|

|

|

|

|

|

|

чтение |

t |

|

WAIT |

|

|

|

|

|

|

|

|

|

|

t |

T1 |

T2 |

TW |

T3 |

T4 |

T5 |

Выгрузка |

Проверка |

Такт |

Чтение |

Дешиф- |

Выполнение |

адреса и байта |

линии |

ожидания |

КОП |

рация |

|

состояния |

READY |

|

|

КОП |

|

Рисунок 115. Машинный цикл М1 Примечание. Зачастую такт выполнения команды, связанный с работой АЛУ

(Т5), для увеличения быстродействия совмещается с тактом Т1 следующего машинного цикла.

73

Кроме работы под управлением потока команд соответствующей программы, МПС может находиться в одном из особых режимов работы:

Прерывание; Захват шин; Останов;

Прерывание при останове.

5.5 Обработка прерываний

Рассмотрим организацию обслуживания запроса прерывания. Из восьми возможных уровней прерываний для использования доступны только семь, так как прерывание нулевого уровня используется для начального старта системы.

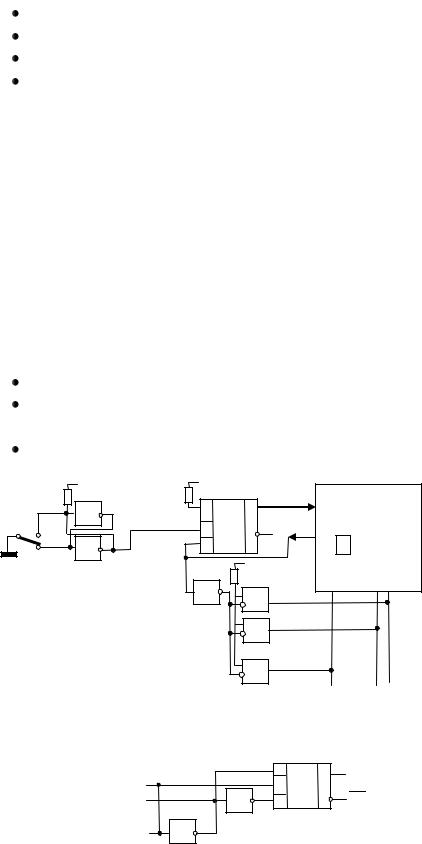

Поступающий запрос по линии INT (h- уровень) принимается триггером прерываний (рис.116). При значении триггера разрешения прерывания (ТП=1) в последнем такте последнего машинного цикла выполнения команды процессор проверяет состояние входа INT и при его единичном значении начинает выполнять машинный цикл прерывание (М8). В свою очередь, этот цикл включает следующие этапы:

Цикл М1 по получению команды RSTi;

Цикл М3 по записи в стек старшего байта программного счётчика

(PC);

Цикл М3 по записи в стек младшего байта программного счётчика (PC);

+5В |

+5В |

|

МП |

|

Q |

INT |

|

|

D Т |

|

|

|

|

|

|

Авт |

C |

INTE (если ТП=1) |

|

|

|

|

|

|

R |

|

ТП |

Шаг |

+5В |

|

|

|

d7 |

d1 d0 |

|

|

|

||

…

Рисунок 116. Схема «вклинивания вектора рестарта»

C |

S |

T |

Q |

|

|

|

|

|

C |

|

|

D |

R |

|

Q |

|

|

|

R

Рисунок 117. D- триггер с установочным входом

74

|

|

|

М1 |

|

|

T1 |

T2 |

|

T3 |

T4 |

|

Выгрузка |

Проверка |

|

Чтение |

||

TW |

Дешиф- |

||||

байта |

линии |

RSTi |

|||

|

рация |

||||

состояния и |

READY |

|

|

||

|

|

|

|||

INTE |

|

|

|

|

CL1

CL2

INT

SYNC

INTE

d0 – d7

байт состояния |

RSTi |

DBIN

чтение

чтение

ТП

a0 – a15

PC

WR

|

М3 |

|

|

М3 |

|

T1 |

T2 |

T3 |

T1 |

T2 |

T3 |

|

|

|

|||

|

|

|

|

|

t

|

|

|

t |

|

|

|

t |

|

|

|

t |

|

|

|

t |

|

запись |

|

запись |

|

|

|

t |

байт состояния |

PС15-8 |

байт состояния |

PС7-0 |

t

t

t

SP-1 |

SP-2 |

|

|

t

Рисунок 118. Машинные циклы обработки запроса прерывания После выполнения этих трех машинных циклов процессор

выполняет первую команду рестарта адрес которой определяется , как N*8. Здесь N – номер рестарта, представляющий собой значение битов с номерами 3-5 кода команды RSTi :

1 1

1 1

1 1

1

1

N

Рисунок 119. Формат команды рестарта

Команды рестарта – это короткие фрагменты памяти (ROM), расположенные в диапазоне 00h – 3Ah. Всего под них выделено 59 байт (7 команд по 8 байт и последняя – 3 байта – команда безусловного перехода. Основное назначение команд рестарта – передача управления программе обработки прерывания с номером N.

75

5.6 Режим «захват шин»

Режим захвата шин сводится к предоставлению одному из устройств МПС (например, видеосистеме) монопольного доступа к шинам, чаще всего, для организации обмена с устройствами памяти. Всё время этого режима линии адреса и данных процессора находятся в высокоимпедансном состоянии.

Начинается режим ПДП установкой устройством ввода-вывода сигнала высокого уровня на линии HOLD. Данная линия сканируется процессором по окончании такта Т2 каждого машинного цикла. Допустим, процессор в момент поступления сигнала HOLD исполнял машинный цикл М1. В таком случае в следующем такте Т3 процессор заканчивает обмен по шине, затем в такте (Т4) переводит выходные буферы ШД и ША в высокоимпедансное состояние и формирует сигнал HLDA. Если запрос захвата шин поступил в машинном цикле, не предусматривающим обмен по шине (например, цикл «останов»), две последние микрооперации выполняются в такте Т3. В завершение цикла М1 в такте Т4 процессор (уже в автономном состоянии) выполняет дешифрацию КОП и, если команде не требуется чтения операндов из памяти, выполняет данную команду.

Завершение режима «захват шин» происходит по сбросу сигнала HOLD, после чего процессор приступает к выполнению следующего машинного цикла.

5.7Режим останова

Всостояние останова процессор переводится программным путём при выполнении команды HLT. Выборка данной команды осуществляется обычным образом (цикл М1), после чего процессор выполняет цикл М9 – «останов». Данный машинный цикл укладывается в два такта :

В такте Т1 шинному формирователю передаётся байт состояния, соответствующий состоянию останов;

В такте Т1 шинному формирователю передаётся байт состояния, соответствующий состоянию останов;

В такте Т2 выходные линии ШД и ША переводятся в СВИ и на линии WAIT устанавливается сигнал h – уровня и далее следует неограниченное количество тактов Тw.

В такте Т2 выходные линии ШД и ША переводятся в СВИ и на линии WAIT устанавливается сигнал h – уровня и далее следует неограниченное количество тактов Тw.

Из состояния останов процессор может выйти следующим образом: По сигналу RESET = 1;

По сигналу HOLD = 1 процессор переходит в состояние «захват шин», по окончании которого возвращается в состояние «останов»;

По сигналу INT=1 процессор начинает обработку запроса прерывания и на команду IRET также возвращается в состояние «останов»;

По сигналу INT=1 процессор начинает обработку запроса прерывания и на команду IRET также возвращается в состояние «останов»;

76