конмпект лекций

.pdf

I |

|

Обеднённый |

+ |

|

|

Uпр |

|

- |

|

|

|

|

|

|

|

|

Cu или Al |

|

|||

|

|

основными |

|

|

|

|

|

Uпр = 0,2 – 0,3 В |

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

носителями |

|

|

+ |

- |

|

|

|

Uобр = 15 В |

|

|

|

|

+ |

|

|

tперекл = 100 нс |

|||

|

|

(запорный) |

|

|

|

|

|

|

||

|

U |

|

|

p |

- |

|

|

|

||

|

|

|

|

|

|

|

||||

|

слой |

|

|

+ |

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

0,2 - 0,3 В |

|

|

|

|

|

|

|

|

|

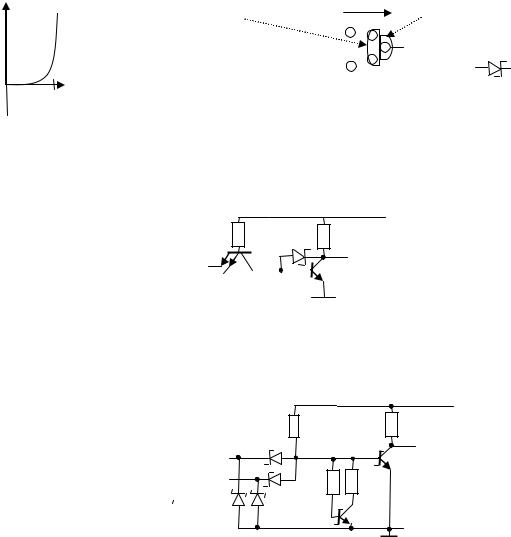

Рисунок 26. Конструкция, основные параметры, вольт-амперная характеристика и условное обозначение диода Шоттки

+Uп

Rк

R1

y

x1

x2

VT2 VT1

VT2 VT1

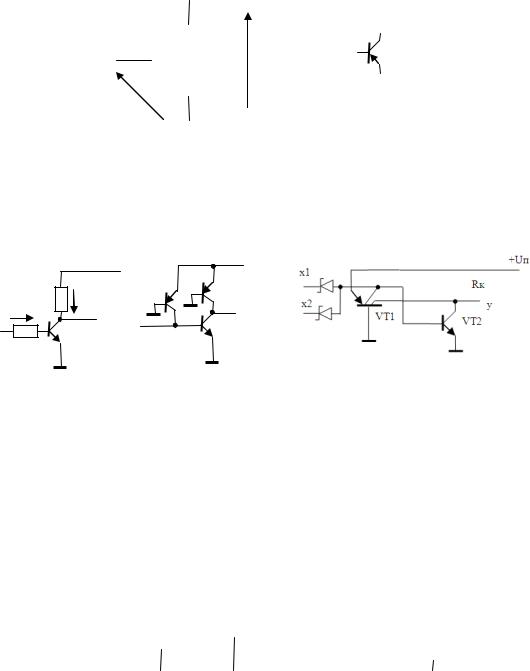

Рисунок 27. Схема шунтирования база – коллекторного перехода ключевого транзистора

+Uп

|

|

R1 |

Rк |

|

|

|

|

|

|

VT1 |

y |

|

|

|

|

x0 |

|

|

VT2 |

x1 |

|

|

|

R3 |

|

R4 |

|

|

|

||

|

VT3 |

|

|

Рисунок 28. Упрощенная схема базового элемента ТТЛШ Отмечают, что энергопотребление схем ТТЛШ не менее, чем в 5 раз

ниже, чем ТТЛ, что позволяет только за счёт этого значительно повысить степень интеграции.

1.1.7 ИИЛ элемент

Наличие в схеме резисторов определяет достаточно серьёзные проблемы при изготовлении интегральных схем, т.к. напыление металла или сплава технологически сложно и достаточно дорого. Решением проблемы может стать замена резисторов нормально открытыми транзисторами.

Процесс подобной модернизации схемы рассмотрим на примере РТЛ

– инвертора. Резисторы Rк и Rб можно рассматривать, как источники, соответственно базового и коллекторного тока. Вместо них в данном случае в схему включают pnp – транзисторы.

21

Коллектор

|

|

|

Коллектор |

База |

p |

|

База |

|

|

||

n |

|

Uкэ |

|

|

|

||

|

|

|

|

|

p |

|

Эмиттер |

|

|

|

|

Uбэ |

|

||

|

Эмиттер |

|

|

Рисунок 29. Упрощенная структура и условное обозначение pnp - транзистора

Этапы преобразования схемы с целью получения элемента интегральной инжекционной логики (ИИЛ или И2Л) представлены на рисунке 30

.

|

|

|

+Uп |

|

|

+Uп |

|

|

|

|

|

|

|

|

Iк |

|

|

|

VT2 |

VT3 |

|

|

|

|

|

||

|

Iб |

|

|

|

|

y |

|

|

|

|

|

|

|

|

|

y |

|

|

|

VT1 |

х |

VT |

|

|

х |

|

|

|

|

|

|

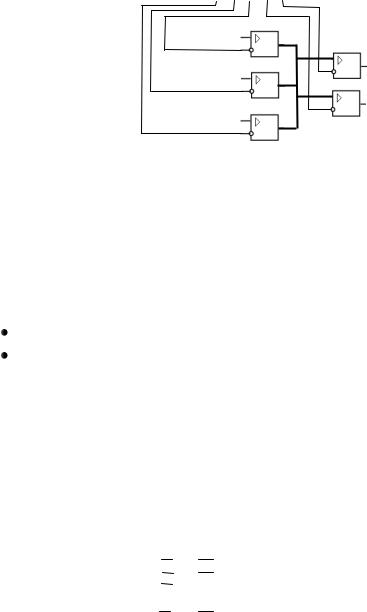

Рисунок 30. Этапы получения элемента ИИЛ Для входных линий в элементах ИИЛ обычно используются диоды Шоттки,

а транзисторы, выполняющие роль источников тока, объединяют в один: Конструктивно многоколлекторный транзистор подобен

многоэмиттерному, включенному по инверсной схеме. Однако при его изготовлении принимаются специальные меры для увеличения коэффициента усиления в расчёте на каждый коллектор до требуемого уровня (сокращение расстояния между коллекторами, приближение скрытого слоя повышенной концентрации в области эмиттера к слою базы).

База |

Коллектор1 |

Коллектор2 |

Эмиттер |

|||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

n |

|

p1 |

|

|

p1 |

|

|

|

|

|

|

|

|

|

|

|

|

p2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

p+ |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Рисунок 31. Структура многоколлекторного pnp транзистора

1.1.8 Инвертор и базисный элемент эмиттерно-связной логики

Иной вариант удерживания транзистора, формирующего выходной сигнал, на границе насыщенного состояния реализован, в так называемой, эмиттерно-связной логике (ЭСЛ). В основе её лежит дифференциальная схема включения npn – транзисторов (токовый ключ).

22

|

|

|

|

|

+Uп |

|

Rк1 |

|

|

Rк2 |

|

|

|

|

|

|

y |

x |

VT1 |

|

|

|

|

|

a |

|

|

|

|

Uвх |

|

|

VT2 |

Uоп ≈ 1,3 В |

|

|

|

|

|||

|

|

|

I2 |

||

I1 |

I∑ |

|

Rэ |

|

|

|

|

|

|

|

|

Рисунок 32. Упрощенная схема токового ключа |

|||||

Транзисторы VT1 и |

VT2 |

|

выполняют с максимально близкими |

||

параметрами. Опорное напряжение (Uоп) ключа подбирается такого номинала, при котором за вычетом падения напряжения на Rэ (Uа), оставшееся (Uбэ2) соответствовало бы начальной стадии открытия базаколлекторного перехода (0,6 В). Пока напряжение

Uвх = Uбэ1+ Uа < Uоп = Uбэ2+ Uа

Uбэ1 < Uбэ2 .

Но напряжение Uбэ2 определено как раз на границе начальной стадии открывания транзистора, следовательно, транзистор VT1 остаётся в отсечке, а VT2 – открытым. Напряжение на выходе формируется по цепи +Uп , Rк1 и соответствует высокому уровню. Режим, когда Uвх = Uоп , для идеально подобранных транзисторов соответствует открытому состоянию их обоих в начальной стадии насыщения. Как самостоятельный, в цифровых схемах данный режим не используется.

Для переключения схемы в нулевое состояние необходимо обеспечить Uвх > Uоп . По мере роста входного напряжения будет увеличиваться ток I1 , суммарный ток I∑ = I1 + I2 и напряжение точки «а» Uа = I∑* Rэ . При этом начнёт уменьшаться напряжение

Uбэ2 = Uоп - Uа

и станет меньше порогового уровня, необходимого для открытого состояния

транзистора VT2, после чего транзистор закроется. |

|

|

|

|||||

Можно также указать, что сопротивление общего резистора |

- около |

|||||||

1кОм, резисторов |

в |

коллекторных цепях |

- несколько |

сотен |

Ом. По |

|||

соотношению u1 и |

u0 |

это также положительная(позитивная) логика, т.к. |

||||||

u1 > u0. |

|

|

|

|

|

|

|

|

|

|

|

|

0 В |

|

|

|

|

|

R1 |

R2 |

R5 |

0 В |

Зона «1» |

x0 |

1 |

y0 |

|

|

x1 |

||||||

|

|

|

|

|

|

|||

|

|

|

y0 |

-0,9 В |

|

|

|

|

|

VT1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

x0 |

VT2 |

|

y1 |

|

|

|

|

|

a |

|

|

|

x0 |

|

|

||

|

|

|

|

|

1 |

y1 |

||

x1 |

|

VT3 |

|

|

|

|

||

|

VT4 |

-1,6 В |

|

x1 |

|

|

||

|

R3 |

R4 |

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

R6 |

|

Зона «0» |

|

|

|

|

|

|

|

|

|

|

|

||

-Uп (-4,5В)

Рисунок 33. Упрощенная схема базового элемента ЭСЛ

23

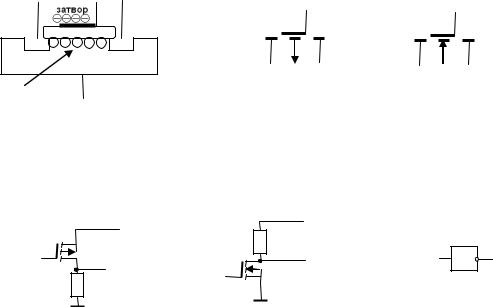

1.2Основы полевой логики. МОП – ключ и элемент, КМОП – ключ и элемент, буфер с высокоимпедансным состоянием.

Полевые транзисторы относятся к группе униполярных, т.к. электрическая проводимость обеспечивается носителями заряда одного знака, а управление осуществляется электрическим полем.

Из многочисленных вариантов этих транзисторов в цифровой технике наибольшее распространение получили транзисторы с изолированным затвором обогащённого типа. При отсутствии напряжения на управляющем электроде эти транзисторы находятся в закрытом состоянии (нормально закрытые). Полевые транзисторы этого типа в соответствии с их конструкцией получили аббревиатуру МОП: металл-оксид-полупроводник

(или MOS – metal-oxide-semiconductor)

сток |

|

исток |

затвор |

|

|

затвор |

|

|

|

|

|

||

p |

+ + + + + |

p |

сток |

исток |

исток |

сток |

|

||||||

|

|

n |

|

|

|

|

проводящий |

|

|

подложка |

|

|

подложка |

подложка |

|

|

|

|

||

канал |

|

|

б) схемное обозначение |

|

в) схемное обозначение |

|

а) упрощенная конструкция |

p- канального транзистора |

n- канального транзистора |

||||

|

|

|

|

|||

Рисунок 34. МОП – транзистор обогащенного типа Наиболее распространённой является схема включения полевого

транзистора с общим истоком.

|

+Uп |

|

|

+Uп |

|

|

|

исток |

|

R |

|

|

|

|

|

|

|

|

||

|

подложка |

|

|

|

y |

|

Uвx |

|

сток |

Uвых |

х |

||

сток |

|

|

||||

|

|

подложка |

|

|

||

|

Uвых |

Uвx |

|

|

||

|

R |

|

исток |

|

|

|

|

|

|

|

|

|

|

а) цифровой ключ на p- канальном МОП |

|

б) цифровой ключ на n- канальном МОП |

в) условное обозначение |

|||

|

транзисторе |

|

|

транзисторе |

|

|

Рисунок 35. Цифровые ключи на полевом транзисторе по схеме общий исток

Уровни сигналов МОП (и КМОП) элементов приняты следующими:

U0 |

U1 |

<= 0,5 В |

>= 0,8 Uп |

Пороговое напряжения открытия полевого транзистора (смещение затвора относительно подложки), при котором индуцируется канал составляет от 0,3 до 3В (среднее 1,65В). Для p – канального транзистора затвор должен быть отрицательнее подложки, а для n- канального – положительнее.

Для формирования единичного уровня сигнала на выходе в схемах МОП – ключа (рисунок 29, а) необходимо дополнительное сопротивление R.

24

Его значение можно оценить из следующих предположений. Пусть при Uпит = 5В необходимо обеспечить уровень U1 = 0,8 Uпит = 4В, считая сопротивление открытого канала равным 10 кОм (в различных вариантах от 1 до 15 кОм).

Выходное напряжение в открытом состоянии транзистора формируется резистивным делителем:

U1 |

Uп |

R |

|

R |

Rк |

||

|

При этом требуемое значение дополнительного сопротивления

R |

U1 |

Rк |

4 Rк |

40кОм |

|

Uп |

U1 |

||||

|

|

|

При переключении в закрытое состояние это сопротивление входит в цепь, по которой стекает отрицательный заряд затвора, ограничивает значение разрядного тока и увеличивает продолжительность формирования нулевого сигнала на выходе элемента. По этой причине максимальная частота МОП – элемента ограничивается значением в несколько сотен кГц.

|

|

Uвх |

|

|

|

U1 |

|

Uвых |

~1,65В |

|

|

|

0,5(U0+U1) |

|

|

Uп |

|

|

|

|

|

|

|

0,8Uп |

|

U0 |

t |

|

|

||

|

|

|

|

|

|

Uвых |

t01 |

|

Uп Uвх |

t10 |

|

|

|

|

|

|

|

|

t10>t01 |

|

0,8Uп |

0,5(U0+U1) |

t |

|

|

||

|

|

|

Рисунок 36. Формирование выходного сигнала МОП - ключом Базисные элементы pМОП – логики в несколько упрощенном

варианте представлены на рисунке 37. Роль дополнительного сопротивления выполняют в данном случае постоянно открытые транзисторы VT3.

|

|

|

+Uп |

x0 |

+Uп |

x0 |

|

VT1 |

|

||

|

|

|

|||

|

|

|

VT1 |

||

|

|

|

|

||

|

VT2 |

|

y |

x1 |

|

|

VT3 |

|

VT2 |

||

|

|

|

|||

|

|

|

|

||

x1 |

|

|

|

|

y |

|

|

|

|

VT3 |

|

|

|

|

|

|

|

а) Штрих Шеффера |

|

|

б) Стрелка Пирса |

||

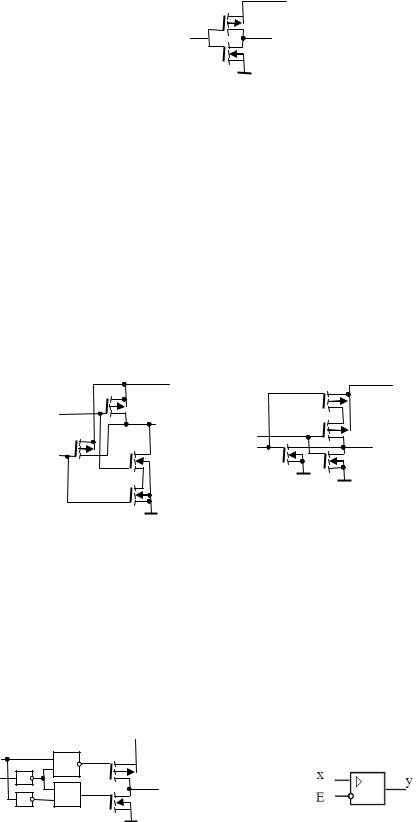

Рисунок 37. Базисные элементы pМОП - логики

Для повышения быстродействия схемы используют пару разноканальных (взаимно дополняющих, т.е. комплементарных) МОП – транзисторов. Подобная схема включения положена в основу КМОП – логики.

25

+Uп

VT1 (pМОП)

x |

y |

|

VT2 (nМОП)

Рисунок 38. КМОП – инвертор

Таблица 4

Состояния транзисторов в схеме КМОП - инвертора

x |

VT1 |

VT2 |

y |

1 |

Закрыт |

Открыт |

0 |

0 |

Открыт |

Закрыт |

1 |

В схеме КМОП – инвертора единичный уровень сигнала формируется сопротивлением канала VT1 (и сопротивлением нагрузки, конечно), а нулевой уровень обеспечивается открытым транзистором VT2. В момент переключения один из транзисторов обеспечивает путь с меньшим сопротивлением для стекания заряда с затвора другого. Переключение происходит быстрее и поэтому рабочая частота КМОП - элементов находится в мегагерцовом диапазоне.

|

VT1 +Uп |

|

+Uп |

x0 |

|

VT4 |

|

|

|

|

|

VT2 |

y |

x0 |

VT3 |

x1 |

|

x1 |

y |

|

|

||

VT3 |

|

|

|

|

|

|

|

|

|

|

VT1 |

|

|

|

VT2 |

|

VT4 |

|

|

а) Штрих Шеффера |

|

б) Стрелка Пирса |

|

|

|

||

Рисунок 39. Базисные элементы КМОП - логики

В схемах базисных элементов одна пара транзисторов включена параллельно, а другая - ярусно.

Комплементарное включение полевых транзисторов используется также в схеме буферного элемента с высокоимпедансным состоянием. Данный элемент используется для объединения на некоторой общей шине произвольного количества отдельных устройств.

x |

VT1 |

|

& |

||

|

||

E |

y |

|

|

||

|

& |

|

|

VT2 |

|

|

б) условное обозначение |

|

|

а) упрощенная схема |

Рисунок 40. Буферный элемент с высокоимпедансным состоянием

26

Таблица состояний элемента

|

|

Е |

|

|

|

|

|

|

х |

y |

|

|

|

1 |

|

|

|

|

любой |

СВИ |

|

||||

|

0 |

|

|

|

|

1 |

1 |

|

||||

|

0 |

|

|

|

|

0 |

0 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Управляющий вектор |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

0 |

1 |

0 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Передатчик 1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Приёмник 1 |

|

Передатчик 2 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Приёмник 2 |

|

Передатчик 3 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 40.1 Пример соединения устройств

2 Логические схемы

Объединение логических элементов в схему для преобразования цифровой информации называется логической схемой. По специфике функционирования логические схемы делятся на:

Комбинационные схемы; Цифровые автоматы;

В комбинационных схемах (КС) сигнал на каждом из выходов однозначно зависит от состояния соответствующих входов (yi = f (x0, x1, … xn-1), где f – булевая функция. К наиболее используемым КС относятся сумматор, дешифратор, мультиплексор, компаратор, мажоритарный элемент. Закон функционирования комбинационной схемы задают или семейством передаточных функций в аналитическом виде или таблицей состояний. Иногда комбинационные схемы называют автоматами без памяти или примитивными автоматами.

x0 |

|

y0 |

y i = f (x0 , x1, x2,…,x n-1) |

x1 |

|

||

|

y1 |

|

|

x2 |

|

|

|

|

|

|

|

… |

|

… |

i= 0,…, m-1 |

x n-1 |

|

||

|

ym-1 |

|

|

|

|

|

|

|

|

|

|

Рисунок 41. Структура комбинационной схемы

27

x0 |

|

|

ЗЭ0 |

|

|

y0 |

x1 |

КС1 |

|

ЗЭ1 |

|

КС2 |

y1 |

x2 |

|

|

|

|||

|

|

|

|

|

||

… |

|

|

|

|

|

… |

x n-1 |

|

|

ЗЭк-1 |

|

|

ym-1 |

|

|

|

|

|

|

|

Рисунок 42. Структура цифрового автомата

В структуре цифровых автоматов (ЦА) имеется блок запоминающих элементов (ЗЭ). По этой причине цифровые автоматы обладают конечным набором внутренних состояний (в данном случае, 2к). Внутренние состояния ЗЭ могут изменяться под действием входных сигналов. Выходной сигнал цифрового автомата формируется на основе входных сигналов и внутреннего состояния ЦА. Зачастую в качестве входных и выходных каскадов ЦА применяются соответствующие комбинационные схемы. Элементарными ЦА являются триггеры. Многочисленные устройства памяти также относятся к цифровым автоматам. Закон функционирования ЦА может быть также задан аналитически, но чаще для этого используются операционные таблицы (похожи на таблицы состояний КС) или временные диаграммы.

2.1 Комбинационные схемы

Знакомство с комбинационными схемами будет иллюстрироваться созданием их с помощью технологии цифрового синтеза на базе карт Карно.

Как известно, картой Карно называется двумерная таблица логических функций, в каждой клетке которой находится произведение входных переменных или их инверсий. Сами переменные идентифицируют строки и столбцы этой таблицы. Используется карта Карно при числе переменных до 6. Алгебраически карта Карно соответствует записи логической (передаточной) функции в совершенной дизъюнктивной нормальной форме (СДНФ) :

F = ∑fi mi

для i = 0,1 …, q-1,

где

fi - значение (требуемое) передаточной функции, mi - минтерм или конъюнкция переменных

q = 2k - количество минтермов,

k – количество входных переменных

Иначе говоря, минтермы представляет собой все возможные комбинации входных сигналов, а с помощью fi выделяются те сочетания, которые должны формировать единичный результат.

Полученную передаточную функцию, как правило, оптимизируют с целью сокращения операций. При этом могут быть использованы, как аналитические выражения для основных логических функций

28

ā = 1- a (НЕ - инверсия),

а^ e = a·e (И - конъюнкция. Поскольку данная операция полностью тождественна арифметическому умножению, далее она будет обозначаться знаком «·»),

аv e = a + e – a·e (ИЛИ - дизъюнкция),

так и аксиомы и законы булевой алгебры :

универсального множества a v 1 = 1,

универсального множества a v 1 = 1,

а · 1 = а,

нулевого множества a v 0 = a,

нулевого множества a v 0 = a,

а · 0 = 0,

дополнительности

дополнительности

аv ā = 1

а· ā = 0

двойственности (де – Моргана)

|

|

|

|

a |

v |

е = ā · ē, |

|

|

|

|

|

a |

· |

е = ā v ē, |

|

|

|

тавтологии |

|

|

|

a v а = а, |

|

|

|

а · а = а, |

|

|

|

коммутативности |

|

аv е = е v а,

а· е = е · а,

ассоциативности

аv (е v i ) = (а v е) v i ,

а· (е · i) = (а · е) · i) ,

ассоциативности

ассоциативности

а v (е v i ) = а · е v а · i, а v е · i = (а v i ) · (а v i ),

поглощения

аv а · i = а,

а· (а v i ) = а,

склеивания

склеивания

а · е v а · ē = a,

(а v e ) · (а v ē) = a

2.1.1 Полный одноразрядный последовательный сумматор

Сумматором называют разновидность комбинационных схем, имеющих как самостоятельное значение, так и являющихся обязательной частью более сложных схем, например контроллеров, процессоров. Назначение сумматоров – выполнять арифметическое сложение двоичных

29

данных. Как известно, остальные арифметические команды (вычитание, умножение и деление) можно выполнить через суммирование. Правда, в этом случае необходимы такие вспомогательные действия, как инверсия и сдвиг.

Выполним синтез сумматора для использования в простейшей схеме последовательного суммирования:

|

|

|

|

|

|

|

b |

n-1 |

bi |

b0 |

|

|

an-1 |

|

ai |

a0 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

полусумматор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

Σ |

s |

|

|

|

|

|

|

|

a |

Σ |

|

s |

|

|

|

a |

Σ |

s |

|

|

|

|

|

b |

c` |

|

|

|

|

|

|

|

b |

c` |

|

|

|

b |

c` |

|

|||||

|

|

|

c |

|

|

|

к i+1 сумматору |

|

c |

|

|

|

|

|

|

|

||||||||

|

CF |

|

|

|

|

|

|

|

|

i-ый |

из i-1 -го |

к 1-му |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

dn-1 di+1 di |

|

d0 |

|

|

|

|

|||||||||||||||

|

|

|

|

|

сумматор |

сумматора |

сумматору |

|||||||||||||||||

из n-2 сумматора |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Рисунок 43. Сумматор с последовательным переносом Таблица 5

Карта Карно одноразразрядного сумматора для выхода s

|

s |

|

|

ab |

|

||

|

00 |

01 |

|

10 |

11 |

||

|

|

|

|

||||

c |

|

0 |

0 |

1 |

|

1 |

1 |

|

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|||||

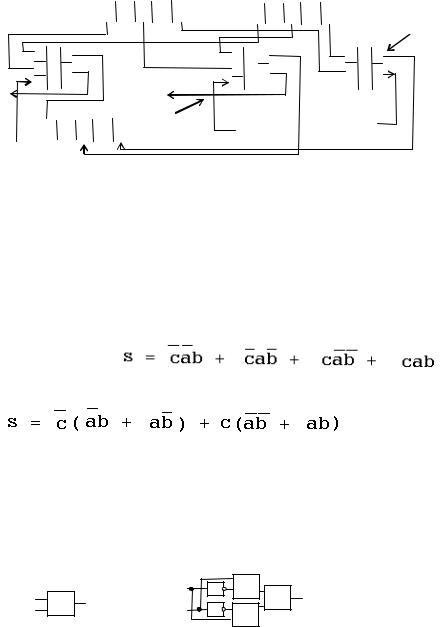

Передаточная функция до преобразования:

Передаточная функция после преобразования:

При этом выражение в первой скобке соответствует логической функции «исключающее ИЛИ», а во второй - «исключающее ИЛИ-НЕ». Таким образом, относительно входа с и результата операции «исключающее ИЛИ» для входов a и b передаточная функция представляет собой ещё одну операцию «исключающее ИЛИ».

x0 |

|

x0 |

& |

|

y |

|

|

1 |

|||

|

=1 |

y |

|

|

|

|

|

|

|

|

|

x1 |

|

x1 |

& |

|

|

|

|

|

|

||

|

|

|

|

|

x0 |

x1 |

«искл. |

|

|

ИЛИ» |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

а) Условное изображение |

б) Схема |

в) Таблица состояния |

Рисунок 44. Элемент исключающее ИЛИ

Таблица 6

Карта Карно одноразразрядного сумматора для выхода с`

c` |

|

|

ab |

|

||

00 |

01 |

|

10 |

11 |

||

|

|

|

||||

c |

0 |

0 |

0 |

|

0 |

1 |

30