- •2.1 Описание структуры устройства

- •2.2.1 Описание работы устройства по функциональной схеме

- •2.2.2 Описание функционирования операционного блока по функциональной схеме

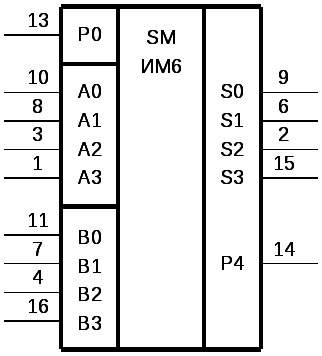

- •2.4 Разработка принципиальной схемы устройства

- •2.4.1 Описание функционирования управляющего автомата по принципиальной схеме

- •2.4.2 Описание функционирования операционного автомата по принципиальной схеме

- •4 Моделирование схемы устройства

- •Заключение

2.4 Разработка принципиальной схемы устройства

Принципиальная схема проектируемого устройства представлена в приложении Б. Она реализована на элементах серий К555, КР573. Приведем УГО и краткие технические характеристики некоторых используемых элементов. УГО универсального регистра сдвига DL194D представлено на рисунке 2.

Он предназначен для

записи, хранения и сдвига четырехразрядного

двоичного кода. Назначение выводов

регистра представлено ниже.

ниже.

Рисунок 2- УГО универсального регистра сдвига DL194D.

Микросхема имеет 4 параллельных входа и четыре выхода. При S0=1,S1=0 происходит сдвиг влево на один разряд, при S0=0,S1=1 выполняется сдвиг вправо на один разряд. Регистр имеет тактовый вход C.

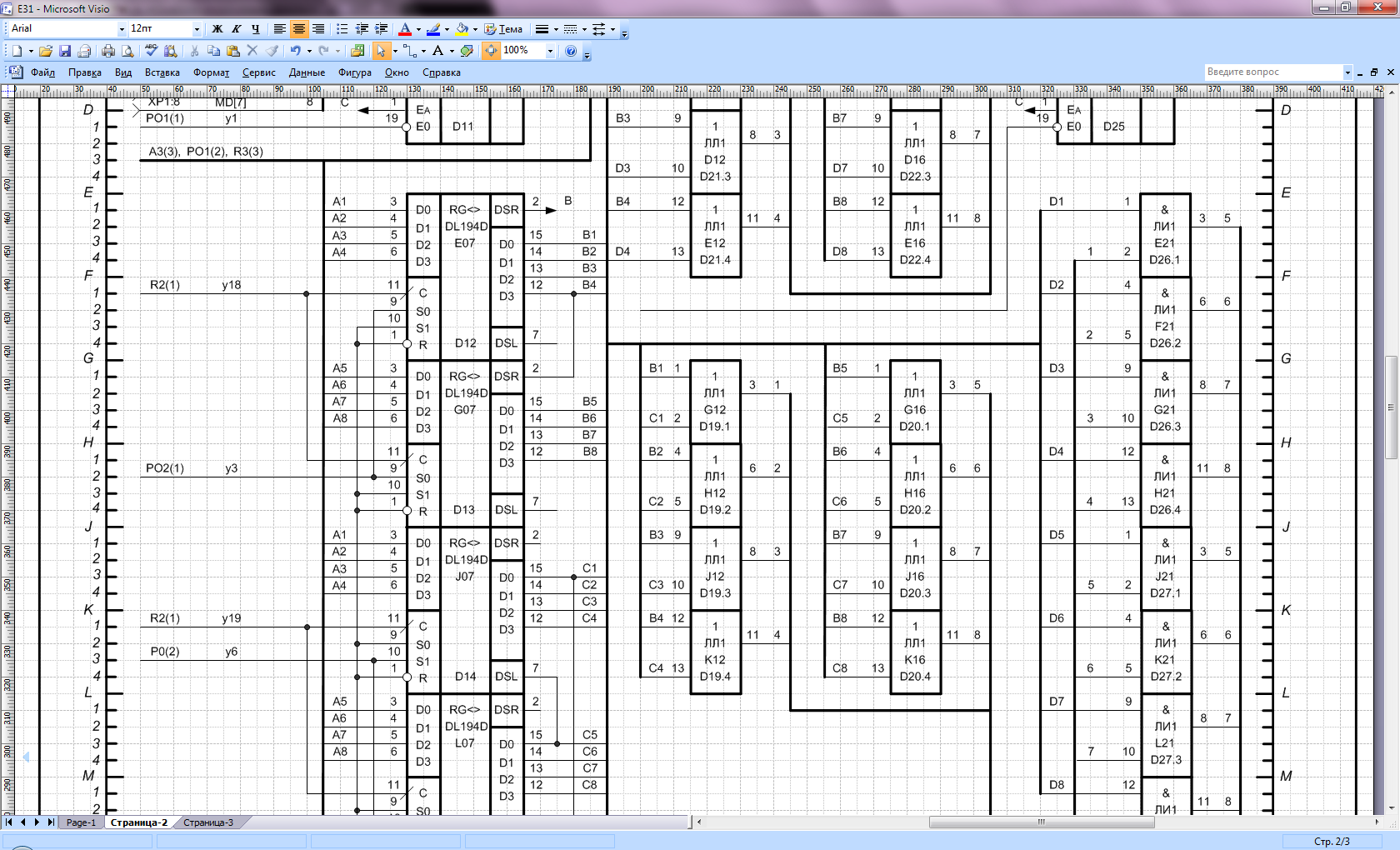

Сумматор реализован на микросхеме К555ИМ6. УГО микросхемы представлено на рисунке 3.

Рисунок 3 - УГО микросхемы

Микросхема предназначена для

осуществления операций сложения над

двумя четырехразрядными двоичными

словами. Назначение выводов элемента

представлено ниже.

Микросхема предназначена для

осуществления операций сложения над

двумя четырехразрядными двоичными

словами. Назначение выводов элемента

представлено ниже.

- А(0-3)- входы слова 1;

- В(0-3)- входы слова 2;

- Р0 - вход переноса;

- Р4- выход переноса.

Для реализации сумматора необходимы 2 такие микросхемы.

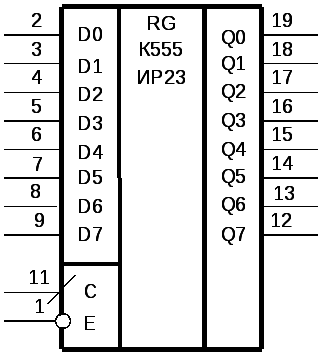

8-разрядный буферный регистр с тремя состояниями на выходе реализован на микросхеме К555ИР23. УГО элемента представлено на рисунке 4.

Рисунок 4 -УГО элемента

Микросхема представляет собой 8-разрядный регистр с умощненными выходами для управления большой емкостной или низкоомной нагрузкой и может быть использована в качестве магистрального формирователя. Базовый элемент микросхемы D-триггер спроектирован по типу проходной защелки, что позволяет при высоком уровне на входе стробированияСпроходить входному сигналу на выход минуя триггер. При подаче низкого уровня сигнала на вход С включается обратная связь и регистр запоминает поданную на входDинформацию и переходит в режим хранения.

Высокий уровень на входе Zпереводит выводы микросхемы в высокоимпедансное состояние, при этом в регистр может записываться новая информация или храниться предыдущая.

Поясняющиережимы работы регистра, представленав таблице 2.

Таблица 2- Поясняющиережимы работы регистра

Микросхема представляет собой два идентичных двоичных 4-разрядных счетчика с раздельными входами тактирования и сброса. Сброс счетчика в исходное состояние (0000) осуществляется при подаче на входы R сигнала низкого уровня. При высоком уровне сигнала на входе R переключение выходов счетчика происходит по положительному перепаду сигнала на входах С.

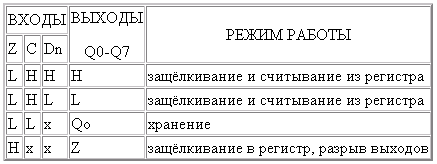

Схема

генератора тактовых импульсов представлена

на рисунке 7. Она реализована по стандартной

схеме с применением элементов НЕ

микросхемы К555ЛН1 и кварцевого резонатора

Z1. Расчет параметров генератора приведен

в разделе 4.

Схема

генератора тактовых импульсов представлена

на рисунке 7. Она реализована по стандартной

схеме с применением элементов НЕ

микросхемы К555ЛН1 и кварцевого резонатора

Z1. Расчет параметров генератора приведен

в разделе 4.

Рисунок 7 -Схема генератора тактовых импульсов

Схему электрическую принципиальную спецпроцессора можно условно разделить на две части: управляющий автомат (лист 1) и операционный автомат (листы 2,3). Опишем работу устройства.

2.4.1 Описание функционирования управляющего автомата по принципиальной схеме

Низкий уровень сигнала сброса ¬RST, поступая на вход сброса R триггера D1.1, устанавливает его в нулевое состояние. Низкий уровень сигнала с прямого выхода триггера поступает на входы сброса R счетчика D7, устанавливая его выходы в нулевое состояние. Одновременно сигнал

низкого уровня с прямого выхода триггера поступает на вход элемента D2.1, запрещая прохождение тактовых импульсов на вход С счетчика D7. Таким образом состояние счетчика не изменяется и управляющий автомат находится в режиме ожидания.

Выполнение микроопераций

спецпроцессором начинается с поступления

низкого уровня сигнала ¬START на вход

установки S триггера D7. Триггер

устанавливается в 1, что влечет за собой

снятие блокирующего сигнала с входа R

счетчика D7 и разрешение прохождения

тактовых импульсов с генератора (D3.1,

D3.2) через элемент D2.1 на вход С счетчика.

Импульсы, поступающие на вход С счетчика

изменяют его состояние. Двоичный код с

выходов счетчиков поступает на адресные

входы элементов ПЗУ (D8…D10), на выходах

которых формируются управляющие сигналы.

Эти сигналы поступают на входы регистров

и буферного элемента (D4…D6). Эти элементы

предназначены для буферизации сигналов

управления и обеспечения их синхронизации.

Временные диаграммы формирования

сигналов управления представлены на

рисунке 8.

Выполнение микроопераций

спецпроцессором начинается с поступления

низкого уровня сигнала ¬START на вход

установки S триггера D7. Триггер

устанавливается в 1, что влечет за собой

снятие блокирующего сигнала с входа R

счетчика D7 и разрешение прохождения

тактовых импульсов с генератора (D3.1,

D3.2) через элемент D2.1 на вход С счетчика.

Импульсы, поступающие на вход С счетчика

изменяют его состояние. Двоичный код с

выходов счетчиков поступает на адресные

входы элементов ПЗУ (D8…D10), на выходах

которых формируются управляющие сигналы.

Эти сигналы поступают на входы регистров

и буферного элемента (D4…D6). Эти элементы

предназначены для буферизации сигналов

управления и обеспечения их синхронизации.

Временные диаграммы формирования

сигналов управления представлены на

рисунке 8.

Рисунок 8-Временные диаграммы формирования сигналов управления

Выполнение каждой микрооперации разбивается на несколько элементарных операций (например: запись на регистр, считывание с регистра), причем число этих операций может быть различным. Каждой элементарной операции соответствует один период ГТИ и свой набор управляющих сигналов.