- •2.1 Описание структуры устройства

- •2.2.1 Описание работы устройства по функциональной схеме

- •2.2.2 Описание функционирования операционного блока по функциональной схеме

- •2.4 Разработка принципиальной схемы устройства

- •2.4.1 Описание функционирования управляющего автомата по принципиальной схеме

- •2.4.2 Описание функционирования операционного автомата по принципиальной схеме

- •4 Моделирование схемы устройства

- •Заключение

4 Моделирование схемы устройства

Для проверки правильности функционирования устройства, была составлена модель на языке VHDL, позволяющая проследить поведение устройства на каждом шаге работы. Моделирование производилось в системе моделирования Quartus II 7.2

Программа на языке VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity algorithm is

Port ( y1 : in STD_LOGIC;

y2 : in STD_LOGIC;

y3 : in STD_LOGIC;

y4 : in STD_LOGIC;

y5 : in STD_LOGIC;

y6 : in STD_LOGIC;

y7 : in STD_LOGIC;

y8 : in STD_LOGIC;

y9 : in STD_LOGIC;

y10 : in STD_LOGIC;

y11 : in STD_LOGIC;

y12 : in STD_LOGIC;

y13 : in STD_LOGIC;

y14 : in STD_LOGIC;

y15 : in STD_LOGIC;

clk : in STD_LOGIC;

D : in STD_LOGIC_VECTOR (7 downto 0):= x"00";

E : out STD_LOGIC_VECTOR (7 downto 0));

end algorithm;

architecture Behavioral of algorithm is

signal r1, r2, r3, rsm : STD_LOGIC_VECTOR (7 downto 0) := x"00";

begin

process (clk) begin

if clk'event and clk = '1' then

if y1 = '1' then

rsm <= rsm + r2 + 1;

elsif y6 = '1' then

rsm <= (r1 or r3) + rsm;

elsif y8 = '1' then

rsm <= rsm + r1;

elsif y10 = '1' then

rsm <= r1 and r2;

elsif y11 = '1' then

rsm <= rsm(7) & rsm (7 downto 1);

elsif y13 = '1' then

rsm <= r2;

elsif y14 = '1' then

rsm <= r2 + r3;

end if;

if y2 = '1' then

r1 <= D;

elsif y5 = '1' then

r1 <= r1 or (r2 and r3);

elsif y7 = '1' then

r1 <= r2(7) & r2(7 downto 1);

end if;

if y3 = '1' then

r2 <= D;

elsif y12 = '1' then

r2 <= r2(6 downto 0) & r2(7);

end if;

if y4 = '1' then

r3 <= D;

elsif y9 = '1' then

r3 <= rsm;

end if;

if y15 = '1' then

E <= r3;

end if;

end if;

end process;

end Behavioral;

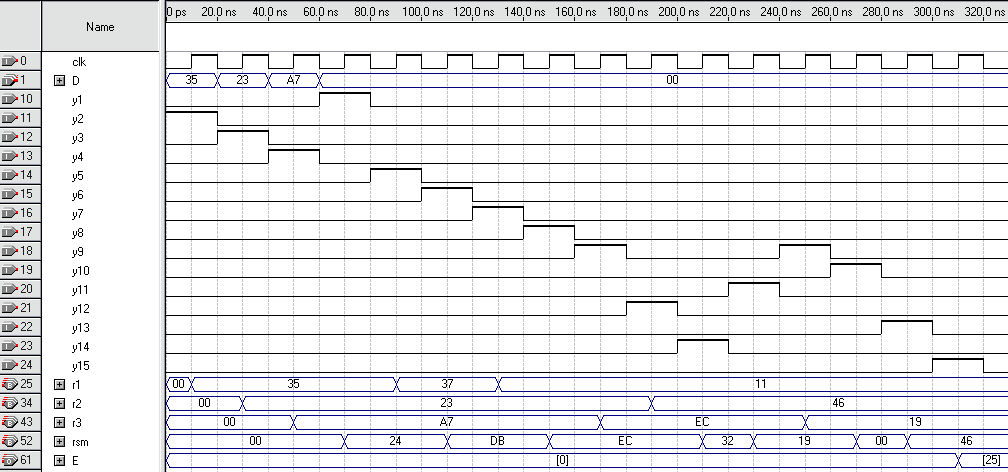

В результате моделирования были получены временные диаграммы работы, которые представлены на рисунке 11.

Рисунок 11-Временные диаграммы

При проверке временных диаграмм, было установлено, что требуемые операции выполняются корректно.

Заключение

В результате выполнения курсовой работы был произведен анализ требований к разрабатываемому устройству, разработана функциональная и принципиальная электрические схемы устройства с учетом требований на курсовое проектирование.

Осуществлен выбор элементной базы, произведен расчет частоты генератора тактовых импульсов с расчетом на самую длинную микрооперацию, построены временные диаграммы выполнения нескольких микроопераций.

Выполнено моделирование устройства в среде Quartus II, поясняющее ее работу, приведены результаты моделирования.

При разработке электрических схем и пояснительной записки использовалась программное обеспечение Microsoft Visio и Microsoft Word.

Работа выполнена в полном соответствии с техническими требованиями и удовлетворяет всем требованиям технического задания.

Список литературы

1. Зельдин Е. А. Цифровые интегральные схемы. М:-Энергоатомиздат,1986.

2.  Шевкопляс

Б. В. Микропроцессорные структуры.

Инженерные решения. Справочник-М:-Радио

и связь,1990.

Шевкопляс

Б. В. Микропроцессорные структуры.

Инженерные решения. Справочник-М:-Радио

и связь,1990.

3. Схемотехника ЭВМ: Учебник для студентов вузов С92 спец. ЭВМ/ Под ред. Г.Н. Соловьёва. – М.: Высшая школа, 1985. – 391 с.

4. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ: Учебное пособие для спец. ЭВМ вузов. – М.: Высшая школа, 1987. – 318 с.

5.М.И. Богданович, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо.– Мн.: Беларусь, 1991.– 493 с.: ил. Цифровые интегральные микросхемы: Справочник

Приложение А

Таблица А.1 - Перечень элементов

|

|

Наименование |

Кол |

Примечание |

|

|

Конденсаторы |

|

|

|

С1 |

К53-14-20В-33 мкФ±10% |

1 |

|

|

С2…С32 |

К10-17а-М750-0,1 мкФ±10% |

31 |

|

|

|

Микросхемы |

|

|

|

DD1 |

К555ТМ2 |

1 |

|

|

DD2 |

К555ЛА4 |

1 |

|

|

DD3 |

К555ЛН1 |

1 |

|

|

DD4,DD5 |

К555ИР23 |

2 |

|

|

DD6 |

К555АП6 |

1 |

|

|

DD7 |

К555ИЕ19 |

1 |

|

|

DD8…DD10 |

К573РФ2 |

3 |

|

|

DD11 |

К555АП6 |

1 |

|

|

DD12,DD13 |

К555ИР24 |

2 |

|

|

DD14 |

К555АП6 |

1 |

|

|

DD15,DD16 |

К555ЛИ1 |

2 |

|

|

DD31 |

К555ИР23 |

1 |

|

|

|

Резисторы С2-33 ОЖО.467.173ТУ |

|

|

|

R1 |

C2-33-0,125-1 кОм+5% |

1 |

|

|

|

Разъемы |

|

|

|

Х1 |

СНП346-40РП21-2В |

1 |

|

Поз.

обозн.

Поз.

обозн.