- •Схемотехника в системах управления

- •1 Аналоговая схемотехника

- •1.1 Резисторы (сопротивления)

- •1.2 Конденсаторы

- •1.3 Индуктивность

- •1.4 Диоды

- •1.5 Биполярные транзисторы

- •1.6 Униполярные транзисторы

- •1.7 Тиристоры

- •1.8 ТранзисторыIgbt(Ай Жи Би Ти)

- •1.9 Сит транзисторы и сит-тиристоры

- •1.10 Новые разработки транзисторов и тиристоров

- •1.11 Обратные связи

- •1.12 Операционные усилители

- •2 Логические схемы

- •2.1 Основные определения

- •2.2 Диодные логические схемы

- •2.3 Ттл логические схемы

- •2.4 Особенности 530, 531, 533, 555 серий

- •2.5 Логика на униполярных транзисторах

- •2.6 Логика с оптическими связями

- •2.7 Программируемые логические интегральные схемы (плис)

- •2.8 Обобщенная модель плис

- •2.9 Микросхема плм (к556 рт 1)

- •3 Триггеры

- •3.1 Триггеры на биполярных транзисторах

- •3.2 Триггеры на униполярных транзисторах

- •3.3 Триггеры на логических элементах

- •3.4 СинхронныйRs–триггер

- •3.5 Счетный триггер на логических элементах

- •3.8 Интегральный шестиэлементныйD–триггер тм2

- •3.10 Прозрачные триггеры–защелки

- •3.11 Гонки

- •3.12 Триггеры на приборах с отрицательным сопротивлением. Триггеры на туннельных диодах.

- •3.13 Триггеры на тиристорах

- •3.14 Триггеры на двухбазовых диодах

- •3.15 Триггеры на операционных усилителях

- •4 Генераторы импульсов

- •4.1 Мультивибраторы на биполярных транзисторах

- •4.1.1 Мультивибраторы в ждущем режиме

- •Мультивибраторы на биполярных транзисторах в автоколебательном режиме.

- •4.2 Ждущий мультивибратор на униполярных транзисторах

- •4.3 Генератор импульсов на двух логических элементах с двумя конденсаторами в автоколебательном режиме

- •4.4 Генератор импульсов на четырех логических элементах с одним конденсатором

- •4.5 Генераторы импульсов на логических элементах в ждущем режиме

- •4.6 Генератор импульсов на туннельном диоде в ждущем режиме

- •4.7 Генератор импульсов на туннельном диоде в автоколебательном режиме

- •4.8 Генератор импульсов на тиристоре в ждущем режиме

- •4.9 Генератор импульсов на тиристоре в автоколебательном режиме

- •4.10 Таймеры

- •4.11 Генератор импульсов в ждущем режиме на таймере

- •4.12 Генератор импульсов в автоколебательном режиме на таймере

- •4.13 Блокинг–генераторы в ждущем режиме

- •4.14 Блокинг–генератор в автоколебательном режиме

- •4.15 Магнито–транзисторный преобразователь двухплечевой

- •4.16 Схема с дополнительным трансформатором

- •4.17 Мостовая и полумостовая схемы магнито–транзисторных преобразователей

- •4.18 Генераторы импульсов на оу в автоколебательном режиме

- •4.19 Генератор импульсов на оу в ждущем режиме

- •4.20 Кварцевая стабилизация импульсных генераторов

- •4.21 Генератор импульсов, стабилизированный кварцем

- •5 Генераторы синусоидальных колебаний

- •5.1 Общие определения

- •5.2 Генератор синусоидальных колебаний сLCконтуром и трансформаторной ос

- •5.3 Схемы с индуктивной, емкостной трехточками

- •5.4RCцепи для генераторов синусоидальных колебаний

- •5.5 Генераторы синусоидальных колебаний сRиC–параллелями

- •5.6 Генераторы синусоидальных колебаний с кварцевой стабилизацией

- •5.7 Генераторы синусоидальных колебаний на оу

- •6 Цифроаналоговые и аналого–цифровые преобразователи

- •6.1 Цифроаналоговые преобразователи

- •6.1.1 Цап с весовыми резисторами

- •6.1.2 Цап с матрицей r–2r

- •6.1.3 Цап с сигма–дельта модуляцией

- •6.1.4 Цап с прямым преобразованием

- •6.2 Аналого–цифровые преобразователи

- •6.2.1 Следящие ацп

- •6.2.2 Развертывающие ацп

- •6.2.3 Ацп с регистром последовательного приближения

- •6.2.4 Ацп с двойным интегрированием

- •6.2.5 Ацп параллельного преобразования

- •6.2.6 Ацп с сигма–дельта () модуляцией

- •6.2.7 Микросхема кр1108 пп–1

- •7 Источники питания электронных устройств

- •7.1 Общие определения

- •7.2 Выпрямители

- •7.3 Параметрические стабилизаторы напряжения

- •7.4 Компенсационные стабилизаторы напряжения

- •7.5 Импульсные стабилизаторы напряжения

- •7.6 Импульсные корректоры коэффициента мощности

4.5 Генераторы импульсов на логических элементах в ждущем режиме

Схемы генераторов импульсов на логических элементах в ждущем режиме строятся аналогично схемам триггеров на логических элементах, но одна из непосредственных связей заменяется на емкостную, кроме того вводится цепь смещения посредством резистора R (рисунок 4.13).

Рисунок 4.13 — Схема генератора импульсов на логических элементах в ждущем режиме

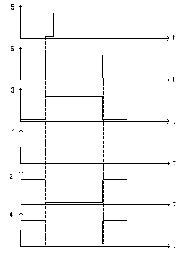

При этом схема может формировать короткий или длинный импульсы, все зависит от величины сопротивления R. Если сопротивление R невелико, т.е. на вход 4 свободно проходит уровень земли – логический нуль, то следовательно схема &2 находится под запретом, управлять ею по входу 5 бесполезно. Единица с выхода 6 поступает на вход 3 схемы &1, поэтому можно управлять по входу 1, т.е. подавать на него нули или единицы. Примем в режиме ожидания на входах 1, 5 единицы, подадим затем на вход 1 длительный нуль, как показано на рисунке 4.14.

На выходе 2 получаем обычное инвертирование входного сигнала. Но фронт выхода 2 практически свободно проходит через конденсатор C на вход 4 (график 4), следовательно, на обоих входах &2 – единицы, выделяют на выходе 6 &2 – нуль. Причем, этот нуль (импульс нуля) короче входящего импульса (график 1), так как сопротивление резистора R невелико, конденсатор C заряжается и разряжается быстро. Более точно, графики 4 и 6 на рисунке 4.14 – это экспоненты, т.к. заряд–разряд происходит по экспонентам, но здесь, с целью упрощения, импульсы изображены прямоугольными.

Рисунок 4.14 — Генерирование короткого импульса.

В том случае, когда сопротивление R велико, образует разрыв в цепи входного электрода 4 логического элемента &2 схемы рисунка 4.13, то это эквивалентно присутствию единицы на входе 4, следовательно, на двух входах &2 – единицы; на выходе &2 – нуль, поступающий на 3 вход &1, запрещающий передачу сигналов через вход 1. Т.е. в этом случае электрод 1 схемы &1 нельзя использовать в качестве входного, как это было в предыдущем случае. Остается только электрод 5 схемы &2, он может быть входным. Процессы генерирования представлены на рисунке 4.16.

Короткий входной импульс (график 5 рисунка 4.15) своим низким уровнем выделяет на выходе 6 схемы &2 высокий уровень (единицу), которая поступает на вход 3 схемы &1, следовательно, две единицы &1 логически умножаясь, выделяют на выходе &1 нуль (низкий уровень, график 2). Этот низкий уровень, нуль, проходит через конденсатор C на вход 4 логической схемы &2, заряд конденсатора C происходит длительно (график 4), так как сопротивление резистора R велико, как было принято. До тех пор, пока будет заряжаться конденсатор C, т.е. на входе 4 – низкий уровень, на выходе 6 сохраняется высокий уровень (график 6), поэтому на обоих входах &1 единицы, логически умножаясь, они образуют нуль на выходе 2 (график 2). В итоге, схема генерирует длинный импульс при запускающем коротком.

Рисунок 4.15 — Генерирование длинного импульса

Расчет длительности

генерируемого импульса может быть

сделан по формуле:

где

,

– уровни нулей, единиц и напряжения

питания в схеме.

,

– уровни нулей, единиц и напряжения

питания в схеме.