- •Федеральное агентство по образованию Российской Федерации

- •Тема 12. Основы теории электронных приборов

- •Тема №2.Электрическое поле.Электрические цепи постоянного тока.

- •Тема №3. Магнитное поле.Магнитные цепи. Индуктивность и ёмкость в электрических цепях.

- •Свойства ферромагнитных материалов. Гистерезис.

- •Тема №4. Однофазные электрические цепи синусоидального тока.

- •Тема№5.Общие свойства четырёхполюсников.

- •Тема №6. Переходные процессы в электрических цепях.

- •Тема№7.Методы расчёта переходных процессов.

- •Какому знаку подчиняется сигнал на выходные цепи (вывод формулы)

- •Тема №8. Трехфазные электрические цепи.

- •Тема №9.Периодические и апериодические несинусоидальные сигналы.

- •Тема№10.Расчёт электрических цепей с помощью оператора Лапласа.Спектры.

- •Передаточная функция и ее связь с дифференциальным уравнением, импульсной и частотной характеристикой

- •Раздел 2. Электроника Тема 12. Основы теории электронных приборов

- •Параметры, характеристики выпрямительных диодов. Типы полупроводниковых диодов.

- •Параметры диодов.

- •Выпрямительные диоды

- •Усиление электрических сигналов с помощью биполярного транзистора.

- •Параметры транзистора:

- •Общая характеристика схем включения транзисторов p-n-p типа.

- •Полевые транзисторы.

- •Полевые транзисторы с изолированным затвором.

- •Полевой транзистор со встроенным каналом (мдп- транзистор).

- •Транзистор с индуцированный каналом (моп- транзистор).

- •Транзистор с затвором Шотки.

- •Силовые полупроводниковые приборы.

- •Оптоэлектроника.

- •Светодиод.

- •Тема 13. Транзисторные усилители электрических сигналов.

- •Коэффициент усиления.

- •Импульсные усилители (иу).

- •Электрические фильтры.

- •Дифференцирующие цепи.

- •Дифференцирующая rl-цепь

- •Интегрирующие цепи(фнч) (фильтр высоких частот)

- •Интегрирующая rc-цепь.

- •Интегрирующая rl-цепь

- •Активные фильтры.

- •Интегральные микросхемы

- •Тема 14. Аналоговые и цифровые элементы и устройства.

- •Логические элементы в дискретном исполнении

- •Триггеры в интегральном исполнении.

- •Тема 15. Комбинационные цифровые устройства.

- •Сумматоры

- •Демультиплексор

- •Регистры (узлы накапливающего типа)

- •Набор элементарных операций:

- •Параллельный статический регистр.

- •Расшифровка временной диаграммы.

- •Цифроаналоговые преобразователи (цап).

- •Аналого-цифровые преобразователи (ацп).

- •Запоминающие устройства (зу).

- •Классификация зу.

- •Тема 16. Источники вторичного питания. Генераторы.

- •Internet-ресурсы.

- •Http://ktf.Krk.Ru/courses/foet/(Сайт содержит информацию по разделу «Электроника»)

- •Http://www.College.Ru/enportal/physics/content/chapter4/section/paragraph8/theory.Html(Сайт содержит информацию по теме «Электрические цепи постоянного тока»)

Триггеры в интегральном исполнении.

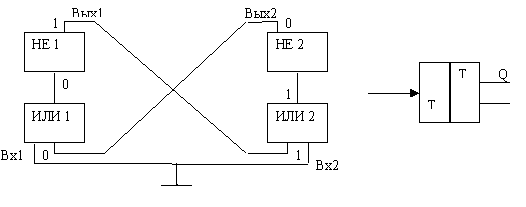

Обычно триггеры выполняют в виде интегральных микросхем. Такие триггеры состоят из логических элементов и блок-схема такого симметричного триггера со счетным входом изображена на рис. 14-18

Он состоит из алогических элементов «ИЛИ» (цепь запуска) и «НЕ» (однокаскадные усилители -инверторы), соединенных цепями перекрестной обратной связи.

Симметричный триггер работает следующим образом. Предположим, что на вход первого инвертора HE1 сигнал не подан - «О». В этом случае на его выходе появится сигнал «1». Этот сигнал, пройдя через логический элемент ИЛИ2, поступит на инвертор НЕ1. В результате на выходе инвертора НЕ2 установится напряжение, соответствующее «О». Сигнал «О» поступит на вход элемента ИЛИ1 а далее на вход инвертора HE1. Если учесть предположение, что входные сигналы триггера равны «О» то триггер все время будет находится в устойчивом состоянии. Это состояние изменится только тогда, когда на Bxl будет подан сигнал «1». Процесс перехода триггера в новое устойчивое состояние произойдет аналогично описанному выше.

Рис. 14-18 Блок-схема и условное обозначение статического триггера.

Рис. 14-19. Схема для установочного запуска триггеров.

Симметричные триггеры, применяемые в ЭВМ, должны отвечать следующим требованиям:

1.Триггер должен сохранять устойчивое состояние в реальных условиях эксплуатации ЭВМ, т.е.при суммарном воздействии всех дестабилизирующих факторов и помеховых импульсов.

2.При каждом воздействии запускающего импульса триггер должен бесперебойно срабатывать.

3.Триггер должен обладать заданной нагрузочной способностью, т.е. он должен нормально рабо тать на нагрузку, включаемую по мере необходимости на выход триггера.В логических схемах ЭВМ, в устройствах памяти, регистрах, счетчиках, преобразователях кода и т.д. применяются цепочки из рядов последовательно - соединенных триггеров. Часто возникает необходимость возвратить всeтриггеры данного ряда в исходное состояние, т.е. осуществить «сброс» триггеров. Это обычно производится при помощи одновременной подачи на входы всех триггеров данного ряда специального сбрасывающего (или установочного) импульса. Для этой цели используется один общий источник импульсов, работающий по схеме, приведенной на рис.3-19.

Резисторы R1, R2,..., Rn включаются для выравнивания токов во всех каналах запуска, диоды VД1,... VДn применяются для разделения цепей установочного запуска.

В случае применения триггеров со счетным входом установочный импульс может подаваться на коды триггеров после дифференцируемых емкостей.

Интегральная технология и использование методов алгебры логики позволили создать большое число различных триггеров на базе логических элементов, различающихся структурой цепей управления и режимами работы. Триггер состоит из цепей управления и запоминающих устройств и имеет один, два (или более) входа и два выхода. Каждый из входов имеет определенное функциональное назначение, которое отражается в обозначении данного входа (R, S, К, D и т. д.). Цепи управления, в которые поступают входные (информационные) сигналы, преобразуют их в сигналы для запоминания и считывания.

Запоминающие устройства состоят

из двух плеч, в каждом из которых

одновременно хранятся сколь угодно

долго два сигнала, один из которых

соответствует логической 1, другой —

логическому0. Выход

триггера Q,

с которого в

исходном состоянии снимается высокий

потенциал, обычно называютпрямым,

другой —инверсным (обозначается![]() ).

).

Кроме симметричных триггеров в зависимости от выполняемых функций различают еще триггеры с раздельный запуском (RS-триггер), синхронный (RCS- триггер),со счетным запуском (Т-триггер), сэлементами задержки илилогическими переключающими схемами в цепях управления (D-триггер),универсальные JK-триггеры), на базе которых могут быть реализованы остальные типы триггеров.

По способу записи информации все триггеры подразделяют на асинхронные, в которых информация записывается непосредственно при поступлении входного сигнала, и тактируемые (синхронные), записывающие входную информацию только при поступлении разрешающего тактового импульса.

Названия триггеров составляют из типов входов. Синхронные триггеры бывают со статическими и динамическими входами. Динамическим называют такой вход, действие поданных уровней сигналов, на который прекращается после соответствующего переключения триггера. Рассмотрим примеры построения некоторых типов триггеров на базе логических элементов либо «ИЛИ — НЕ», либо «И — НЕ»

.

RC-триггер.

Б уквыR

и

S

означают:

R

-

раздельный вход установки в состояние

О, S

—

раздельный

вход установки в состоянии 1.

Схема

асинхронного RS

триггера на двух логических элементах

и его

графическое обозначение в схемах

показано нак рисунке 3-20. Триггер имеет

два прямых входа R

и

S

и

два выхода: прямой Q

и

инверсный

уквыR

и

S

означают:

R

-

раздельный вход установки в состояние

О, S

—

раздельный

вход установки в состоянии 1.

Схема

асинхронного RS

триггера на двух логических элементах

и его

графическое обозначение в схемах

показано нак рисунке 3-20. Триггер имеет

два прямых входа R

и

S

и

два выхода: прямой Q

и

инверсный

![]() .

Перекрестная

связь выхода каждого элемента ИЛИ — НЕ

со входом другого обеспечивает

схеме два устойчивых состояния.

Предположим, что на входах R

и

S

действуют

уровни логического 0, не влияющие на

состояние триггера. Примем для

определенности, что на прямом выходе

триггера Q

имеет

место уровень логического 0. Этот сигнал

совместно с нулевым уровнем на входе S

образуют

на

инверсном выходе

.

Перекрестная

связь выхода каждого элемента ИЛИ — НЕ

со входом другого обеспечивает

схеме два устойчивых состояния.

Предположим, что на входах R

и

S

действуют

уровни логического 0, не влияющие на

состояние триггера. Примем для

определенности, что на прямом выходе

триггера Q

имеет

место уровень логического 0. Этот сигнал

совместно с нулевым уровнем на входе S

образуют

на

инверсном выходе ![]() триггера

уровень логической 1. Уровень логической

1, в свою очередь, формирует

совместно с 0,на входе R

на

прямом выходе Q

уровень

логического 0. Это устойчивое состояние

триггера называют нулевым

по уровню на прямом выходе.

триггера

уровень логической 1. Уровень логической

1, в свою очередь, формирует

совместно с 0,на входе R

на

прямом выходе Q

уровень

логического 0. Это устойчивое состояние

триггера называют нулевым

по уровню на прямом выходе.

Таюлица истинности асинхронного RS триггера (С).

|

вход |

выход |

Режим работы | |||

|

S |

R |

Q |

|

| |

|

0 |

0 |

0 |

0 |

хранение | |

|

1 |

0 |

1 |

0 |

Запись 1 | |

|

0 |

1 |

0 |

1 |

Запись 0 | |

|

1 |

1 |

x |

x |

запрещено | |

рис. 14-20. Асинхронный RS триггер на двух логических элементах ИЛИ-НЕ , а

и его графические обозначения(б)

Переключают триггер в другое состояние тподачей на один из входов сигнала логической 1, при подаче на вход R уровня 1, а на вход S уровня 0 на инверсном выходе устанавливается сигнал Q=0, который переводит триггер в состояние 1, соответствующее Q = 1. Аналогично происходит переключение триггера и при подаче уровня логической единицы на вход S.

Для RS-триггера существует запретная комбинация входных сигналов. Триггер теряет свойства (его состояние становится неопределенным) при одновременной подаче на входы R и S уровня логической 1. Если отпирающие импульсы действуют одновременно, то триггер оказывается временно в симметричном состоянии, из которого он может выйти равновероятно в любое из двух устойчивых состояний. Таким образом, результат неоднозначный, что недопустимо.

В схеме рис. 14-21 элементы «ИЛИ — НЕ» могут быть заменены элементами «И — НЕ». Свойства триггера при этом сохраняются, но управление им должно производиться уровнями логического 0. Такой триггер можно рассматривать как RS-триггер с инверсными входами. Более сложные триггеры D-, Т- и JK-типов выполняют на базе одного или двух RS-триггеров с использованием в цепях управления элементов задержки или логических переключающих схем. Наибольшее распространение получили триггеры с логическими переключающими схемами в цепях управления, поскольку интегральное исполнение элементов задержки затруднено.

c)

|

вход |

выход |

Режим работы | |||

|

S |

R |

Q |

|

| |

|

0 |

0 |

0 |

0 |

хранение | |

|

1 |

0 |

1 |

0 |

Запись 1 | |

|

0 |

1 |

0 |

1 |

Запись 0 | |

|

1 |

1 |

x |

x |

запрещено | |

Таблица истинности асинхронного RS триггера.

рис. 14-21 Асинхронный RS триггер на двух логических элементах И-НЕ (a )

и его графическое изображение(б)

RCS-триггер (синхронный)

Если необходимо, чтобы триггер реагировал на изменение входного сигнала только в определённый интервал времени, то используют триггерные устройства с синхронизацией (рис.14-22).

Это - триггеры RSC - типа. Они имеют дополнительный синхронизирующий вход С.

Если С = 0 , то при любых значениях R и S сигналы на входах RS-триггера логические "1" и состояние RS-триггера не меняется.

Если

C

= 1,S=1,R

= 0,to

формируется

нулевой сигнал на выходе Э1 и RS-триггер

устанавливается

в "1" (Q=

1, ![]() =0).

=0).

Если С = 1, S = 0, R = 1 , то появляется "0" на выходе Э2 и RS-триггер устанавливается в "0").

Значение входных сигналов S = 1,R=1,C=1 приводит к неопределенному состоянию устройства. Следовательно, такое состояние схемы является запрещенным.

в)

|

С |

S |

R |

Q |

|

Составляющие | |

|

1 |

1 |

1 |

x |

x |

Запрещено | |

|

1 |

1 |

0 |

0 |

1 |

Сост. 1 | |

|

1 |

0 |

1 |

1 |

0 |

Сост . 2 | |

|

0 |

1 |

0 |

0 |

1 |

не меняется | |

|

0 |

0 |

1 |

0 |

1 |

не меняется | |

Рис.14-22 Синхронный RCS-триггер (a) , графическое изображение(б) и таблица истинности(в)

D-триггер.

D-триггер построен на логических элементах «И-НЕ» и изображен на рис 14-23.

Рис 14-23. Логическая схема D-триггер

D-триггер- это триггер, который повторяет на своем выходе состояние входа. Из рис 3-23 видно, чтоD-триггер можно образовать изRS-триггеров, если на их входы одновременно подавать инверсные сигналы. Информация вD-триггерах хранится за счет синхронизации и в этой связиD-триггеры имеют информационный входDи вход синхронизации С. В описываемом триггере сигнал на входе передается на выход только по сигналу синхронизации и этот триггер называется триггером с запоминанием информации (триггер задержки).

Условное графическое обозначение D-триггера показано на рис 14-24.

Рис 14-24. D-триггер в интегральном исполнении.

Таблица истинности D-триггера.

-

C

D

1

0

0

1

1

1

1

0

![]() - логический уровень на этом выходе

после подачи импульса синхронизации.

- логический уровень на этом выходе

после подачи импульса синхронизации.

Т-триггер.

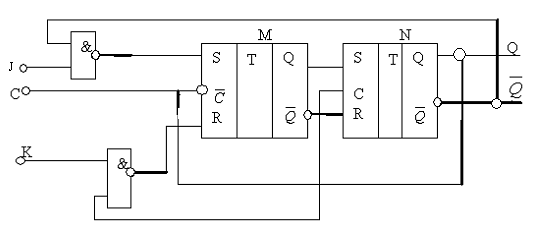

Т-триггер состоит из двух синхронных RS-триггеровMиN, которые имеют синхронизирующие входы С и счетный вход Т и логический элемент НЕ (рис 14-25).

Рис 14-25. Т- триггер с синхронизирующим «С» входом в интегральном исполнении

Если![]() ,

то на выходных триггера М будут такие

же сигналы, а на входеSтриггера М появится 1, (на выходеR=0).

При подаче сигнала «1» на Т автоматически

отключает триггерNотMи в то же время обеспечивает запись в

него сигналов наS=1, наR=1.

При условии, что Т=0 обеспечивает

отключение триггера М и запись сигналов

с его выходов проходит в триггерN,

который переводится в состояниеQ= 0,

,

то на выходных триггера М будут такие

же сигналы, а на входеSтриггера М появится 1, (на выходеR=0).

При подаче сигнала «1» на Т автоматически

отключает триггерNотMи в то же время обеспечивает запись в

него сигналов наS=1, наR=1.

При условии, что Т=0 обеспечивает

отключение триггера М и запись сигналов

с его выходов проходит в триггерN,

который переводится в состояниеQ= 0,

![]() = 1. И тем самым переходит в

состояние, противоположное предыдущему.

= 1. И тем самым переходит в

состояние, противоположное предыдущему.

JK-триггер.

Это наиболее универсальный триггер, который строится на основе двухступенчатого RS-триггера и двух логических элементов И-НЕ (рис 14-26).

Рис 14-26. Схема JK-триггера в интегральном исполнении.

При комбинации сигналов если J=1 и к=0, то приQ=0 получают наS(триггер М) единицу. После подачи первого синхронизирующего импульса на С, триггер установится в состояниеQ=1.

При комбинации сигналов J=1 иk=0,то приQ=1 наSиR(триггера М) будут равны “0” и при подаче синхронизирующего импульса на С, триггер не будет изменять своего состояния.

Таким же образом по отношению к состоянию Q=0 действует сигналk=1 приj=0.

При комбинации сигналов J=K=1, то получаютS=1 (триггер М) иR=0 (триггер М) приQ=0 иS=0(триггер М) иR=0 (триггер М) приQ=1. Таким образом триггер переключается в противоположное состояние при соответствующем фронте сигнала на С.

Условное графическое изображение JK-триггера показано на рис 14-27.

Рис 14-27. Условное графическое изображение JK-nhbuuthf/

Таблица истинности JK-триггера.

-

J(t)

K(t)

Q(t+1)

Q

(t+1)

(t+1)Примечание

0

0

Q(t)

Q

(t)

(t)RS- режим

0

1

0

1

RS- режим

1

0

1

0

RS- режим

1

1

Q

(t)

(t)Q(t)

Режим Т триггера

Таблица получения из JK-триггерa.RS, T, D-триггеров

|

JK |

|

|

RS |

|

|

T |

|

|

D |

|