- •Конспект лекций оглавление

- •Общие с ведения о микроконтроллерах

- •Обобщенная структурная схема микроконтроллера

- •Система прерываний

- •Работа системы прерываний

- •Стек данных

- •Микроконтроллеры Intel, Motorola и Microchip

- •Краткое описание особенностей микроконтроллеров

- •Работа сср в режиме шим

- •Примеры контроллеров 18еххх, 16еххх. Характеристики 16 и 18 серии.

- •Периферийные модули

- •Основные характеристики микроконтроллеров

- •Рекомендации по схематическому решению для портов (16 серия)

- •Структура памяти

- •Банк памяти быстрого доступа

- •Регистр выбора банка памяти данных bsr (18 серия)

- •Косвенная адресация, регистра indf и fsr

- •Операция косвенной адресации

- •Механизм косвенной адресации

- •Работа с памятью рiс16fххх

- •Чтение из еерrом-памяти

- •Запись еерrом данных

- •Управление прерываниями Серия рiс16ххх

- •Система прерывании рiс18fхх2

- •Обработка прерываний

- •Контроллеры pic16f87x

- •Карта памяти микроконтроллеров:

- •Структурная схема микроконтроллеров pic16f87x:

- •Служебные регистр:

- •Контроллеры 18 серии

- •Карта памяти микроконтроллеров рiс18f242/442:

- •Регистры конфигурации контроллера:

- •Аппаратный умножитель 8х8

- •Модуль ацп

- •Конфигурация выводов модуля ацп (рiс16f873/76)

- •Источник опорного напряжения

- •Параллельные порты ввода/вывода

- •Последовательный синхронный порт (мssр)

- •Временные диаграммы работы mssp

- •Пример соединения двух мк через spi

- •Режим i2c последовательного порта mssp.

- •Асинхронно-синхронный последовательный порт (usart)

- •Временные диаграммы работы usart в асинхронном режиме

- •Ведомый параллельный порт (psp)

- •Временные диаграммы порта psp

- •Способы кодирования данных

- •Универсальная последовательная шина (usb) Краткий обзор шины

- •Протоколы передачи

- •Питание

- •Оконечные точки

- •Нумерация устройств

- •Описатели

- •Классы устройств / Драйверы класса

- •Микроконтроллеры с модулем usb

- •Приемопередатчик

- •Регистры управления и состояния модуля usb

- •Регистр флагов прерываний модуля usb (uir)

- •Регистр разрешения прерываний модуля usb (uie)

- •Регистр флагов ошибок модуля usb (ueir)

- •Регистр разрешения прерывания по ошибкам модуля usb (ueie)

- •Регистр состояния модуля usb (ustat)

- •Регистр управления модулем usb (uctrl)

- •Регистр адреса usb (uaddr)

- •Регистр состояния программного обеспечения usb

- •Регистры управления оконечными точками (uepn)

- •Буферы оконечных точек

- •Программирование модуля usb

- •Программное обеспечение usb

- •Основные функции и подпрограммы

- •Ресурсы процессора

- •Уровни стека

- •Память программ

- •Память данных

- •Буферные регистры

- •Выбор страниц/Выбор банков

- •Интегрирование подпрограмм usb в программу

Последовательный синхронный порт (мssр)

МSSР - ведущий синхронный последовательный порт - для связи с внешними периферийными устройствами и микросхемами (ЕЕРRОМ, АЦП драйверы ЖКИ и т.д.)

МSSР имеет 2 режима:

• Последовательный периферийный интерфейс (SРI)

• I2С.

Выводы МSSР в режиме SРI:

• SDI - вход данных SРI

• SDO - выход данных SРI

• SCK - тактовый сигнал.

• -SS - выбор ведомого.

Основные режимы SPI: ведущий (SСК - выход), ведомый (SСК - вход).

Дополнительные режимы SРI: 4 режима тактирования отличающиеся полярностью и фронтом SСК; управление фазой выборки бита данных: частотой приема/передачи в режиме Маster, режим выбора ведомого в режиме Slave.

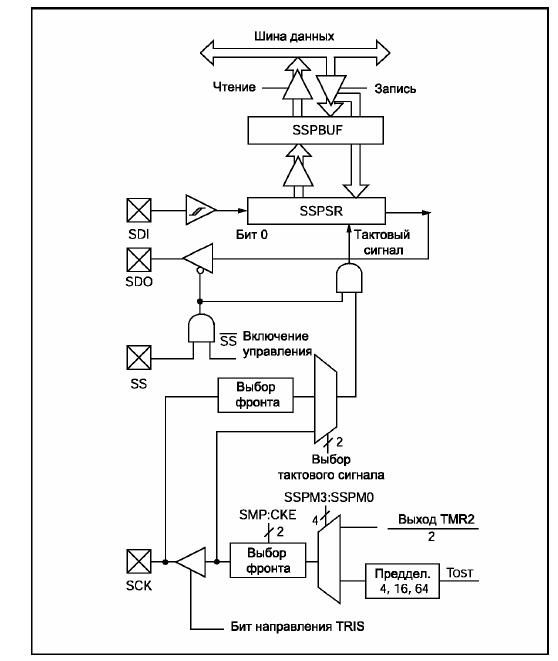

Структурная схема модуля в режиме SРI

Регистры SFR, связанные с работой SРI: управления SSРСОN, статуса SSРSТАТ и данных SSРВUF.

Регистр SSРСОN:

WCOL |

SSPOV |

SSPEN |

CKP |

SSPM3 |

SSPM2 |

SSPM1 |

SSPM0 |

Бит 7 |

|

|

|

|

|

|

Бит 0 |

WCOL: Флаг - Режим "ведущий" 1/0 - конфликт - попытка записи SSРВUF во время передачи/нет конфликта; "ведомый" 1/0 - конфликт - запись в SSРВUF во время передачи байта/нет конфликта;

SSPOV: 1/0 - есть/нет переполнение SSРВUF (при передаче значения не имеет);

SSPEN: 1/0 - включение/выключен не последовательного порта;

CKP: 1/0 - полярность тактирующих импульсов, ожидание высокий/низкий уровень;

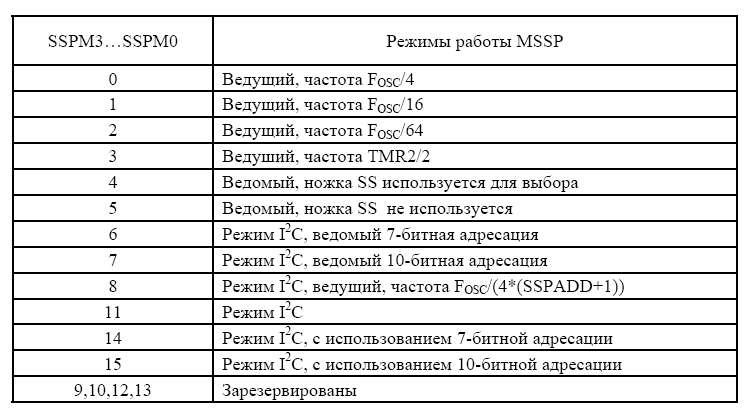

SSPM3… SSPM0: режим работы последовательного порта (ведущий/ведомый, SPI/I2C) и скорость передачи данных.

Регистр SSРSТАТ:

SMP |

CKE |

D/-A |

P |

S |

R/W |

UA |

BF |

Бит 7 |

|

|

|

|

|

|

Бит 0 |

SMP: 1/0 - входные данные защелкиваются в конце/середине выходных

СКЕ: Для режима SРI: при СКР=0: 1/0 - данные передаются по фронту/падению тактового импульса; при СКР=1: 1/0 - данные передаются по падению/фронту тактового импульса. Для режима I2C: 1/0 - уровни на шине соответствуют спецификации Smbus/ I2C

D/-A: последний принятый или переданный байт - данные/адрес (I2С)

Р: последний принятый бит - SТОР (I2C)

S: последний принятый бит - SТАRТ (I2C)

R/W: чтение/запись (действителен при совпадении адреса и до принятия битов SТАRТ, SТОР или АSК)

UA: обновить/нет адрес в регистре SSРАDD (10 разрядный I2C)

BF: буфер SSРВUF заполнен/пуст (при передаче - I2C). 1 - прием завершен/идет передача, 0 - идет прием/завершена передача.

Для передачи байта необходимо записать его в регистр SSРВUF. Во время приема информация записывается в регистр SSРSR и по его окончанию перемещается в регистр SSРВUF с одновременной установкой флага ВF. Запись в регистр SSРВUF во время осуществления передачи/приема игнорируется, однако при этом устанавливается бит WCOL сигнализирующий о коллизии. Для передачи следующего байта содержимое регистра SSРВUF должно быть прочитано, иначе не произойдет аппаратный сброс флага ВF и передача производится не будет.