- •Конспект лекций оглавление

- •Общие с ведения о микроконтроллерах

- •Обобщенная структурная схема микроконтроллера

- •Система прерываний

- •Работа системы прерываний

- •Стек данных

- •Микроконтроллеры Intel, Motorola и Microchip

- •Краткое описание особенностей микроконтроллеров

- •Работа сср в режиме шим

- •Примеры контроллеров 18еххх, 16еххх. Характеристики 16 и 18 серии.

- •Периферийные модули

- •Основные характеристики микроконтроллеров

- •Рекомендации по схематическому решению для портов (16 серия)

- •Структура памяти

- •Банк памяти быстрого доступа

- •Регистр выбора банка памяти данных bsr (18 серия)

- •Косвенная адресация, регистра indf и fsr

- •Операция косвенной адресации

- •Механизм косвенной адресации

- •Работа с памятью рiс16fххх

- •Чтение из еерrом-памяти

- •Запись еерrом данных

- •Управление прерываниями Серия рiс16ххх

- •Система прерывании рiс18fхх2

- •Обработка прерываний

- •Контроллеры pic16f87x

- •Карта памяти микроконтроллеров:

- •Структурная схема микроконтроллеров pic16f87x:

- •Служебные регистр:

- •Контроллеры 18 серии

- •Карта памяти микроконтроллеров рiс18f242/442:

- •Регистры конфигурации контроллера:

- •Аппаратный умножитель 8х8

- •Модуль ацп

- •Конфигурация выводов модуля ацп (рiс16f873/76)

- •Источник опорного напряжения

- •Параллельные порты ввода/вывода

- •Последовательный синхронный порт (мssр)

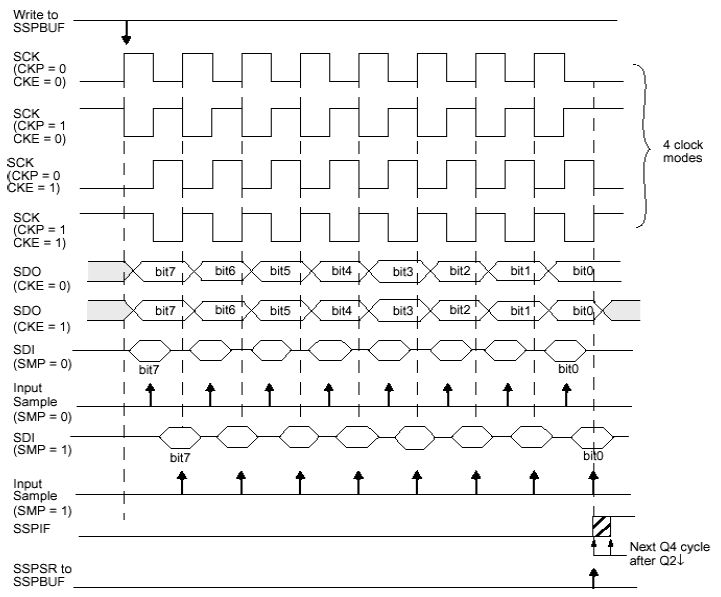

- •Временные диаграммы работы mssp

- •Пример соединения двух мк через spi

- •Режим i2c последовательного порта mssp.

- •Асинхронно-синхронный последовательный порт (usart)

- •Временные диаграммы работы usart в асинхронном режиме

- •Ведомый параллельный порт (psp)

- •Временные диаграммы порта psp

- •Способы кодирования данных

- •Универсальная последовательная шина (usb) Краткий обзор шины

- •Протоколы передачи

- •Питание

- •Оконечные точки

- •Нумерация устройств

- •Описатели

- •Классы устройств / Драйверы класса

- •Микроконтроллеры с модулем usb

- •Приемопередатчик

- •Регистры управления и состояния модуля usb

- •Регистр флагов прерываний модуля usb (uir)

- •Регистр разрешения прерываний модуля usb (uie)

- •Регистр флагов ошибок модуля usb (ueir)

- •Регистр разрешения прерывания по ошибкам модуля usb (ueie)

- •Регистр состояния модуля usb (ustat)

- •Регистр управления модулем usb (uctrl)

- •Регистр адреса usb (uaddr)

- •Регистр состояния программного обеспечения usb

- •Регистры управления оконечными точками (uepn)

- •Буферы оконечных точек

- •Программирование модуля usb

- •Программное обеспечение usb

- •Основные функции и подпрограммы

- •Ресурсы процессора

- •Уровни стека

- •Память программ

- •Память данных

- •Буферные регистры

- •Выбор страниц/Выбор банков

- •Интегрирование подпрограмм usb в программу

Временные диаграммы работы mssp

Пример соединения двух мк через spi

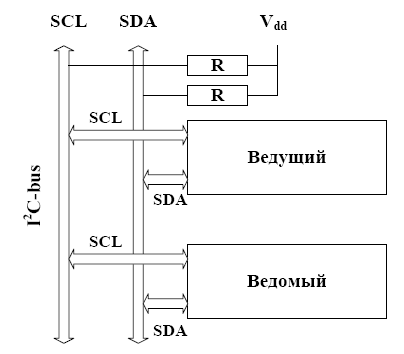

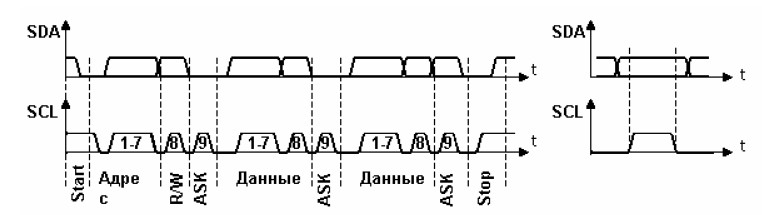

Режим i2c последовательного порта mssp.

Порт I2C

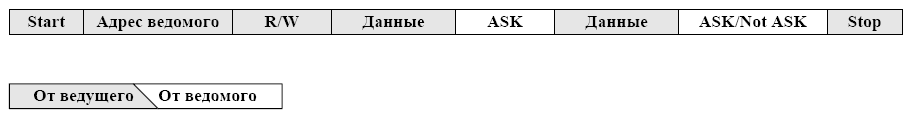

R/W = 0/1 - Запись/Чтение;

Start/Stop - стартовая/стоповая комбинация;

АSК - подтверждение (низкий уровень);

Not ASK - без подтверждения; Адрес ведомого - 7 бит

Формат кадра

Порядок шагов «ведущий передатчик». Ведущий -

1) обнаруживает свободное состояние шины

2) формирует на шине Start-состояние

3) выставляет адрес ведомого, ожидая АSК от адресованного ведомого.

4) передает байты данных, ожидая АSК после каждого байта.

5) формирует на шине Stop -состояние.

Порядок шагов «ведущий приемник» такой же, но ведущий принимает байты данных, посылая АSК в ведомый передатчик после каждого байта и выставляя Not ASK после получения последнего байта.

Порт МSSР в режиме I2C поддерживает все функции ведущих и ведомых устройств, поддержку общего вызова, аппаратные прерывания по обнаружению состояния на шине I2C-bus.

Поддерживает 7-10 разрядные адреса ведомых устройств. Имеет фильтры на 100 и 400 кГц для повышения помехоустойчивости.

Для работы используются 2 вывода: SDA – данные и SCL – синхросигнал.

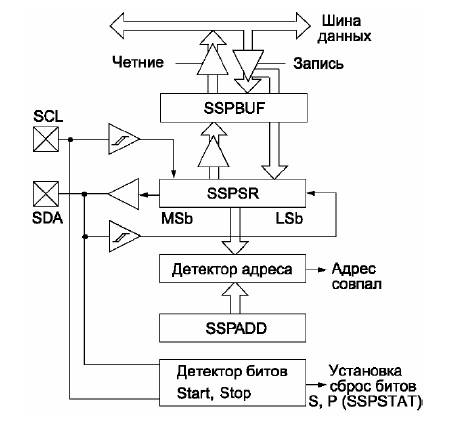

Регистры, связанные с работой MSSP в режиме I2C:

• SSPCON, SSPCON2 – управления

• SSPSTAT – состояния

• SSPBUF – буфер данных

• SSPSR – внутренний сдвиговый регистр

• SSPADD – адреса.

Режимы I2C:

• ведомый, 7-разрядный адрес (в SSDADD – адрес)

• ведомый, 10-разрядный адрес (в SSDADD – адрес)

• ведущий, тактовая частота = Fosc/4/(SSDADD+1)

• программная поддержка ведущего режима (для совместимости)

Включается установкой 5-го бита (SSPEN) регистра SSPCON.

SSPSTAT содержит биты: обнаружение START, STOP, флаг приема данных/адреса, указатель загрузки старшего байта адреса, бит операции (прием/передача).

Все операции по реализации протокола I2C должны быть реализованы программно с помощью управляющих и статусных битов, так как MSSP осуществляет только аппаратную поддержку.

Структурная схема модуля MSSP в режиме I2C

Регистр управления SSPCON2

GSEN |

ASKSTAT |

ASKDT |

ASKEN |

RCEN |

PEN |

RSEN |

SEN |

Бит 7 |

|

|

|

|

|

|

Бит 0 |

GSEN: разрешить прерывание при приеме адреса 0000h – общего вызова (Slave)

ASKSTAT: передача ведущего, 1/0 – нет/есть сигнал ASK от ведомого (Master)

ASKDT: прием ведущего, 1/0 – передать/нет ASK ведомому (Master).

ASKEN: сформировать сигнал ASKDT; аппаратно сбрасывается (Master).

RCEN: разрешить прием данных (Master).

PEN: сформировать STOP (Master).

RSEN: сформировать второй START (Master).

SEN: сформировать START (Master).

Асинхронно-синхронный последовательный порт (usart)

Режимы работы:

• Асинхронный (полнодуплексный)

• Ведущий синхронный (полудуплекс).

• Ведомый синхронный (полудуплекс).

Связан с регистрами SFR:

• TXSTA и RCSTA – регистры контроля и статуса передающей и приемной частей соответственно,

• RSR – внутренний сдвиговый регистр USART.

• RCREG – хранящего принятый байт и TXREG – регистра передаваемой информации. Имеет двойную буферизацию на приеме (можно принять 2 байта в буфер FIFO регистра RCREG и один – в регистр RSR).

• SPBRG – регистр скорости USART.

Для работы с портом необходимо осуществить его конфигурирование путем установки нужных битов в регистрах TXSTA и RCSTA.

Регистр TXSTA:

CSRC |

TX9 |

TXEN |

SYNC |

- |

BRGH |

TRMT |

TX9D |

Бит 7 |

|

|

|

|

|

|

Бит 0 |

CSRC: 1/0 – ведущий/ведомый только в синхронном режиме

TX9: 1/0 - выбор формата посылки 9/8 бит

TXEN: 1/0 - разрешение/запрет передачи

SYNC: 1/0 - синхронный/асинхронный режим работы порта

BRGH: 1/0 - выбор скорости работы - высокая/низкая

TRMT: 1/0 - флаг состояния сдвигающего регистра передатчика (пустой/полный)

TX9D: 9-й бит передаваемых данных (может быть битом проверки на четность)