- •Конспект лекций оглавление

- •Общие с ведения о микроконтроллерах

- •Обобщенная структурная схема микроконтроллера

- •Система прерываний

- •Работа системы прерываний

- •Стек данных

- •Микроконтроллеры Intel, Motorola и Microchip

- •Краткое описание особенностей микроконтроллеров

- •Работа сср в режиме шим

- •Примеры контроллеров 18еххх, 16еххх. Характеристики 16 и 18 серии.

- •Периферийные модули

- •Основные характеристики микроконтроллеров

- •Рекомендации по схематическому решению для портов (16 серия)

- •Структура памяти

- •Банк памяти быстрого доступа

- •Регистр выбора банка памяти данных bsr (18 серия)

- •Косвенная адресация, регистра indf и fsr

- •Операция косвенной адресации

- •Механизм косвенной адресации

- •Работа с памятью рiс16fххх

- •Чтение из еерrом-памяти

- •Запись еерrом данных

- •Управление прерываниями Серия рiс16ххх

- •Система прерывании рiс18fхх2

- •Обработка прерываний

- •Контроллеры pic16f87x

- •Карта памяти микроконтроллеров:

- •Структурная схема микроконтроллеров pic16f87x:

- •Служебные регистр:

- •Контроллеры 18 серии

- •Карта памяти микроконтроллеров рiс18f242/442:

- •Регистры конфигурации контроллера:

- •Аппаратный умножитель 8х8

- •Модуль ацп

- •Конфигурация выводов модуля ацп (рiс16f873/76)

- •Источник опорного напряжения

- •Параллельные порты ввода/вывода

- •Последовательный синхронный порт (мssр)

- •Временные диаграммы работы mssp

- •Пример соединения двух мк через spi

- •Режим i2c последовательного порта mssp.

- •Асинхронно-синхронный последовательный порт (usart)

- •Временные диаграммы работы usart в асинхронном режиме

- •Ведомый параллельный порт (psp)

- •Временные диаграммы порта psp

- •Способы кодирования данных

- •Универсальная последовательная шина (usb) Краткий обзор шины

- •Протоколы передачи

- •Питание

- •Оконечные точки

- •Нумерация устройств

- •Описатели

- •Классы устройств / Драйверы класса

- •Микроконтроллеры с модулем usb

- •Приемопередатчик

- •Регистры управления и состояния модуля usb

- •Регистр флагов прерываний модуля usb (uir)

- •Регистр разрешения прерываний модуля usb (uie)

- •Регистр флагов ошибок модуля usb (ueir)

- •Регистр разрешения прерывания по ошибкам модуля usb (ueie)

- •Регистр состояния модуля usb (ustat)

- •Регистр управления модулем usb (uctrl)

- •Регистр адреса usb (uaddr)

- •Регистр состояния программного обеспечения usb

- •Регистры управления оконечными точками (uepn)

- •Буферы оконечных точек

- •Программирование модуля usb

- •Программное обеспечение usb

- •Основные функции и подпрограммы

- •Ресурсы процессора

- •Уровни стека

- •Память программ

- •Память данных

- •Буферные регистры

- •Выбор страниц/Выбор банков

- •Интегрирование подпрограмм usb в программу

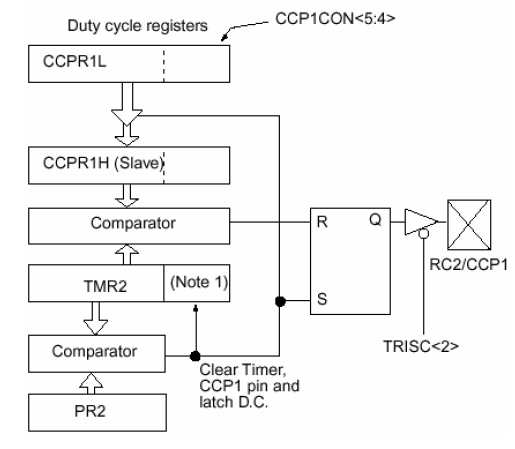

Работа сср в режиме шим

В режиме ШИМ модуль ССР формирует на выводы ССР1 ШИМ - процесс с 10-битной точностью установки длительности импульса и периода.

Период ШИМ - рассчитывается по формуле:

PWMper = 4*(PR2+1)*Tosc*TMR2presc

Длительность ШИМ- импульса задается значением регистра ССРR1L и двух бит ССР1СОN<5:4>:

PWMimp = (ССРR1L:ССР1СОN<5:4>)*Tosc*TMR2presc

и может быть обновлена в любой момент, однако изменение производится также как и для периода ШИМ в момент окончания формирования периода (т.е. когда ТМR2 = РR2). При этом значение ССРR1L переписывается в регистр ССРR1H и 2-битную защелку для хранения всего 10-битного значения.

В случае если длительность ШИМ - импульса больше периода, сброс вывода порта в 0 не производится. Таким образом, для перевода, модуля ССР в режим ШИМ необходимо выполнить следующие операции:

• Установить период ШИМ - сигнала записью соответствующего значения в регистр РR2;

• Установить длительность ШИМ - импульса с помощью регистра ССРR1L и 2-х битов ССР1СОN<5:4>;

• Конфигурация вывода ССР1 в режим вывода сбросом бита ТRISC<2> в регистре конфигурации порта С;

• Установить значение предделителя ТМR2 и включить ТМR2 установкой бита ТМR2ОN(Т2СОN<2>);

• Сконфигурировать модуль ССР в режим ШИМ установкой требуемых битов ССРхМЗ...ССРхМ0.

Схема модуля ССР в режиме ШИМ

Модуль ССР1:

Регистр ССРR1 модуля ССР состоит из двух 8-разрядных регистров: ССРR1L (младший байт), ССРК1Н (старший байт). В регистре ССР1СОN находятся управляющие биты модуля ССР1, доступные для записи и чтения. В режиме сравнения триггер специального события сбрасывает таймер ТМR1.

Модуль ССР2:

Регистр ССРR2 модуля ССР состоит из двух 8-разрядных регистров: ССРR2L (младший байт), ССРR2Н (старший байт). В регистре ССР2СОN находятся управляющие биты модуля ССР2, доступные для записи и чтения. В режиме сравнения триггер специального события сбрасывает таймер TМR1 и запускает преобразование АЦП (если АЦП включено).

• Режим пониженного энергопотребления SLЕЕР

Переход в режим энергосбережения происходит по команде SLЕЕР. При переходе в режим SLЕЕР сторожевой таймер WDТ сбрасывается, но продолжает работать. В регистре STATUS бит –РD сбрасывается в '0', бит -ТО устанавливается в '1', тактовый генератор микроконтроллера выключен. Порты ввода/вывода остаются в том же состоянии, что и до выполнения команды SLЕЕР (высокий уровень, низкий уровень, третье состояние).

Для снижения энергопотребления в SLЕЕР режиме все каналы ввода вывода должны быть подключены к VDD или VSS при отсутствии токов из внешней схемы через выводы портов, выходы модуля компараторов и источника опорного напряжения выключены. Выводы находящиеся в третьем состоянии должны иметь высокий или низкий уровень сигнала, чтобы избежать токов переключения входных буферов. Вход Т0СК1 должен быть подключен к VDD или VSS для снижения энергопотребления. Должны учитываться внутренние подтягивающие резисторы, включенные на входах РОRТВ. На входе -МСLR должен быть высокий уровень сигнала.

У контроллеров с буквой 'L' в маркировке самое низкое энергопотребление.

Пример потребления контроллером РIС16F877:

при тактовой частоте 4 МГц и UDD = 3 В потребляет < 0.6 мА

при тактовой частоте 32 кГц и UDD =3 В потребляет 20 мкА (меньше в 30 раз)

Порт А (РОRТА): цифровой ввод-вывод, входы АЦП и таймеров. Выходы с открытым коллектором для управления нагрузкой (6 выводной).

Все каналы РОRTA имеют соответствующие биты направления в регистре TRISA, позволяющие настраивать канал как вход или выход. Запись '1' в TRISA переводит соответствующий выходной буфер в 3-е состояние. Запись '0' в регистр ТRISА определяет соответствующий канал как выход, содержимое защелки РОRТА передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Порт В (РОRТВ): управление клавиатурой, внешнее прерывание, низковольтное программирование.

РОRТВ – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра ТRISB определяют направление каналов порта. Установка бита в ‘1’ регистра ТRISB переводит выходной буфер в 3-е состояние. Запись '0' в регистр ТRISB настраивает соответствующий канал как выход, содержимое защелки РОRТВ передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Три вывода РОRТВ мультиплицированы со схемой низковольтного программирования: RВЗ/РGМ, RВ6/РGС, RВ7/РGD.

Порт С (РОRТС): цифровой ввод-вывод (байтовый). Шины SPI, I2C, USART.

Биты регистра TRISC определяют направление каналов порта. Установка бита в ‘1’ регистра TRISC переводит выходной буфер в 3-е- состояние. Запись ‘0’ в регистр TRISC настраивает соответствующий канал как выход, содержимое защелки РОRТС передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Выводы РОRТС мультиплицированы с несколькими периферийными модулями. На каналах РОRТС присутствует входной буфер с триггером Шмидта.

Порты D и Е (РОRТD, РОRТЕ): программно реализуемый параллельный порт.