- •Конспект лекций оглавление

- •Общие с ведения о микроконтроллерах

- •Обобщенная структурная схема микроконтроллера

- •Система прерываний

- •Работа системы прерываний

- •Стек данных

- •Микроконтроллеры Intel, Motorola и Microchip

- •Краткое описание особенностей микроконтроллеров

- •Работа сср в режиме шим

- •Примеры контроллеров 18еххх, 16еххх. Характеристики 16 и 18 серии.

- •Периферийные модули

- •Основные характеристики микроконтроллеров

- •Рекомендации по схематическому решению для портов (16 серия)

- •Структура памяти

- •Банк памяти быстрого доступа

- •Регистр выбора банка памяти данных bsr (18 серия)

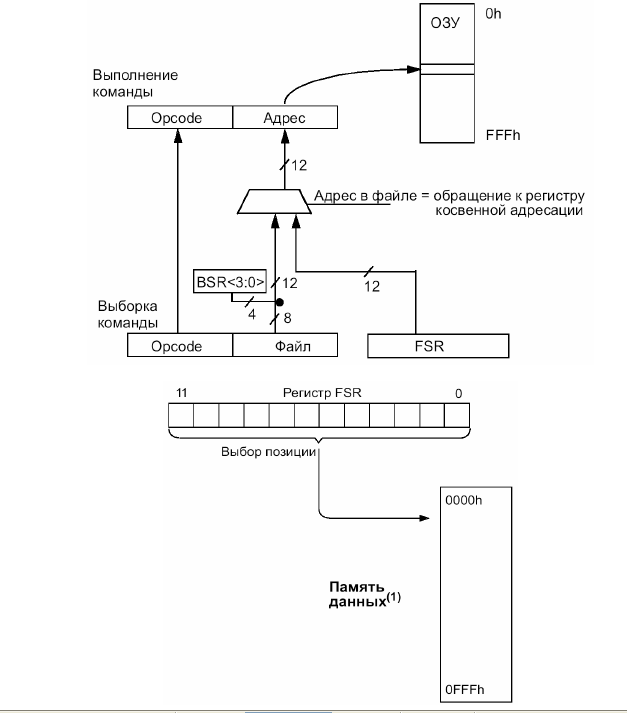

- •Косвенная адресация, регистра indf и fsr

- •Операция косвенной адресации

- •Механизм косвенной адресации

- •Работа с памятью рiс16fххх

- •Чтение из еерrом-памяти

- •Запись еерrом данных

- •Управление прерываниями Серия рiс16ххх

- •Система прерывании рiс18fхх2

- •Обработка прерываний

- •Контроллеры pic16f87x

- •Карта памяти микроконтроллеров:

- •Структурная схема микроконтроллеров pic16f87x:

- •Служебные регистр:

- •Контроллеры 18 серии

- •Карта памяти микроконтроллеров рiс18f242/442:

- •Регистры конфигурации контроллера:

- •Аппаратный умножитель 8х8

- •Модуль ацп

- •Конфигурация выводов модуля ацп (рiс16f873/76)

- •Источник опорного напряжения

- •Параллельные порты ввода/вывода

- •Последовательный синхронный порт (мssр)

- •Временные диаграммы работы mssp

- •Пример соединения двух мк через spi

- •Режим i2c последовательного порта mssp.

- •Асинхронно-синхронный последовательный порт (usart)

- •Временные диаграммы работы usart в асинхронном режиме

- •Ведомый параллельный порт (psp)

- •Временные диаграммы порта psp

- •Способы кодирования данных

- •Универсальная последовательная шина (usb) Краткий обзор шины

- •Протоколы передачи

- •Питание

- •Оконечные точки

- •Нумерация устройств

- •Описатели

- •Классы устройств / Драйверы класса

- •Микроконтроллеры с модулем usb

- •Приемопередатчик

- •Регистры управления и состояния модуля usb

- •Регистр флагов прерываний модуля usb (uir)

- •Регистр разрешения прерываний модуля usb (uie)

- •Регистр флагов ошибок модуля usb (ueir)

- •Регистр разрешения прерывания по ошибкам модуля usb (ueie)

- •Регистр состояния модуля usb (ustat)

- •Регистр управления модулем usb (uctrl)

- •Регистр адреса usb (uaddr)

- •Регистр состояния программного обеспечения usb

- •Регистры управления оконечными точками (uepn)

- •Буферы оконечных точек

- •Программирование модуля usb

- •Программное обеспечение usb

- •Основные функции и подпрограммы

- •Ресурсы процессора

- •Уровни стека

- •Память программ

- •Память данных

- •Буферные регистры

- •Выбор страниц/Выбор банков

- •Интегрирование подпрограмм usb в программу

Операция косвенной адресации

Каждому регистру FSR соответствует регистр INDF, плюс еще четыре дополнительных регистра, которые определяют, как изменится FSR при выполнении косвенной адресации:

• При косвенной адресации регистр FSRn не изменяется (обращение к INDFn)

• Автодекремент FSRn после косвенной адресации (обращение к POSTDECn)

• Автодекремент FSRn после косвенной адресации (обращение к POSTINCn)

• Автодекремент FSRn перед косвенной адресацией (обращение к PREINCn)

Значение в регистре WREG используется как смешение к FSRn. После косвенной адресации значение WREG и FSR не изменяется (обращение к PLUSWn).

Состояние FSR не отображается в регистре STATUS при использовании автоинкремента или декремента при косвенной адресации. Например, если значение в FSR становиться равным ‘0’, то бит 7 не будет установлен в ‘1’.

Инкремент и декремент FSR затрагивает все 12 разрядов адреса. Например, переполнение FSRnL вызовет автоматическое увеличение FSRnН. Эти особенности позволяют использовать FSRn как указатель программного стека, в дополнение к операциям с таблицами в памяти данных.

Обращение к PLUSWn позволяет реализовать индексированную косвенную адресацию. К регистру FSR добавляется значение регистра WREG, чтобы сформировать адрес ячейки. Значение регистра при этом не изменяется.

Если регистр FSR содержит значение, которое указывает на один из регистров INDFn, косвенной чтение будет давать результат ‘0’, а запись эквивалентна команде NOР (биты регистра STATUS изменяются).

Если адресатом при косвенной адресации являются регистры FSRnН или FSRnL, то операция записи имеет более высокий приоритет, чем автоинкремент и автодекремент.

Механизм косвенной адресации

Работа с памятью рiс16fххх

Память делится на:

- память программ;

- flash-память;

- оперативная память.

Доступ к функциям записи/чтения ЕЕРRОМ памяти данных и FLASH памяти программ выполняется через шесть регистров специального назначения:

- ЕЕDАТА;

- ЕЕDАТН;

- ЕЕАDR;

- ЕЕАDRН;

- ЕЕСОN1;

- ЕЕСОN2.

Операции чтения/записи ЕЕРRОМ памяти данных не приостанавливают выполнение программы. В регистре ЕЕАDR сохраняется адрес ячейки ЕЕРRОМ памяти данных. Данные сохраняются/читаются из регистра ЕЕDАТА. В микроконтроллерах РIС16F873/874 объем ЕЕРRОМ памяти 128 байт. Старший бит адреса в регистре ЕЕАDR всегда должен равняться нулю, потому что не поддерживается циклическая адресация (т.е. ячейка с адресом 0х80 не отображается на 0х00). В РIС16F876/877 объем ЕЕРRОМ памяти данных 256 байт (используются все 8-разрядов регистра ЕЕАDR).

Чтение FLASH памяти программ не влияет на выполнение программы, а во время операции записи выполнение программы приостановлено. В спаренных регистрах ЕЕАDRН:ЕЕАDR сохраняется 13-разрядный адрес ячейки памяти программ, к которой необходимо сделать обращение. Спаренные регистры ЕЕАDRН:ЕЕАDR содержат 14-разрядные данные для записи или отображают значение из памяти программ при чтении. Также как для ЕЕРRОМ памяти данных, в регистры ЕЕАDRН:ЕЕАDR должен быть загружен адрес физически реализованной памяти программ, потому что циклическая адресация не поддерживается.

При работе с памятью не выполняется проверка на правильность и качество записи. Если попадается некорректное значение адреса или данных, то выполняется NОР.

ЕЕРRОМ рассчитана на 100 000 циклов чтения/записи, а flash-память на 10000 циклов.