- •Кафедра радиотехники

- •Информация о дисциплине

- •1.2. Содержание дисциплины и виды учебной работы

- •1.2.2. Объём дисциплины и виды учебной работы

- •1.2.3. Перечень видов практических занятий и контроля

- •Раздел 6.

- •Раздел 7.

- •Тематический план дисциплины для студентов заочной формы обучения

- •2.4. Временной график изучения дисциплины при использовании информационно-коммуникационной технологии

- •2.5. Практический блок

- •2.5.1. Практические занятия

- •2.5.1.1 Практические занятия (очно-заочная форма обучения)

- •2.5.1.2 Практические занятия (заочная форма обучения)

- •2.5.2. Лабораторные работы

- •2.5.2.1 Лабораторные работы (очно-заочная форма обучения)

- •2.5.2.2 Лабораторные работы (заочная форма обучения)

- •2.6. Балльно-рейтинговая система оценки знаний

- •3. Информационные ресурсы дисциплины

- •Показатели и характеристики аналоговых электронных устройств

- •3.2.1.1.Основные определения и классификация аналоговых электронных устройств

- •3.2.1.2. Основные энергетические показатели усилителя и количественная оценка усиления

- •3.2.1.3. Искажения, вносимые усилителем

- •Частотные искажения

- •Фазочастотные искажения

- •3.2.1.5. Переходные искажения

- •3.2.1.6. Связь между переходной и частотной характеристиками

- •Нелинейные искажения

- •Методы количественной оценки нелинейных искажений

- •3.2.1.8. Помехи и шумы

- •Вопросы для самопроверки

- •3.2.2. Обратная связь и её влияние на показатели и характеристики аналоговых электронных устройств

- •3.2.2.1. Основные определения и классификация видов обратной связи

- •3.2.2.2. Эквивалентные параметры усилителя с обратной связью Обратная связь по напряжению последовательного типа

- •Обратная связь по току последовательного типа

- •Обратная связь по напряжению параллельного типа

- •Эквивалентное входное сопротивление усилителя с обратной связью Последовательное введение обратной связи

- •Вопросы для самопроверки

- •3.2.3. Транзисторный усилительный каскад

- •3.2.3.1. Постановка задачи и упрощающие предположения

- •3.2.3.2. Схемы включения транзистора и их обобщение.

- •3.2.3.3. Первичные параметры транзистора и методы расчёта технических показателей каскада для включения об, оэ, ок

- •Вопросы для самопроверки

- •3.2.4. Обеспечение и стабилизация режима работы транзисторов по постоянному току

- •3.2.4.1. Основные способы осуществления исходного режима транзистора

- •Дестабилизирующие факторы

- •3.2.4.2. Стабилизация исходного режима

- •Коллекторная стабилизация

- •Эмиттерная стабилизация

- •Вопросы для самопроверки

- •3.2.5. Каскады предварительного усиления

- •3.2.5.1. Резистивный каскад оэ

- •Выбор исходного режима

- •Вопросы для самопроверки

- •3.2.6. Оконечные усилительные каскады

- •3.2.6.1. Работа транзистора при больших уровнях сигнала Построение динамических характеристик

- •Выходная динамическая характеристика

- •Входная динамическая характеристика

- •Проходная и сквозная динамические характеристики

- •Режимы работы транзистора

- •3.2.6.3. Двухтактные оконечные каскады

- •Двухтактный каскад усиления в режиме «а»

- •3.2.6.4. Схемы двухтактных оконечных каскадов и их свойства

- •Двухтактные каскады с параллельным питанием

- •Двухтактные каскады с последовательным питанием

- •Вопросы для самопроверки

- •Операционные усилители

- •Вопросы для самопроверки

- •3.2.8. Устройства регулировки усиления, перемножения и деления сигналов Регуляторы усиления

- •Плавная регулировка усиления

- •Ступенчатые регуляторы

- •Устройства перемножения и деления сигналов

- •Вопросы для самопроверки

- •3.2.9. Усилители высокой чувствительности

- •Вопросы для самопроверки

- •3.2.10. Активные rc–фильтры

- •Звенья фнч и фвч первого порядка

- •Вопросы для самопроверки

- •Заключение

- •3.3. Глоссарий (краткий словарь терминов)

- •3.4. Методические указания к выполнению лабораторных работ общие указания

- •Охрана труда и техника безопасности

- •Работа 1 исследование свойств отрицательной обратной связи

- •I. Цель работы

- •II. Основные теоретические положения

- •III. Описание лабораторной установки

- •IV. Порядок выполнения работы

- •V. Содержание отчёта

- •III. Описание лабораторной установки

- •IV. Порядок выполнения работы

- •V. Содержание отчёта

- •III. Описание лабораторной установки

- •IV. Порядок выполнения работы

- •V.Содержание отчёта

- •Работа 4 исследование оконечного каскада при работе транзисторов в режиме «а»

- •I. Цель работы

- •II. Основные теоретические положения

- •III. Описание лабораторной установки

- •IV. Порядок выполнения работы

- •V. Содержание отчёта

- •III. Порядок выполнения работы

- •IV. Содержание отчёта

- •3.5. Методические указания к проведению практических занятий

- •Практическое занятие № 1

- •Расчёт делителя в цепи базы транзистора Каскады предварительного усиления представляют собой обычно резис-тивный каскад оэ или ок с эмиттерной стабилизацией исходного режима ра-боты транзистора.

- •Для каскада ок, схема которого изображена на рис. 2:

- •Практическое занятие № 2 Расчёт элементов низкочастотной и высокочастотной коррекции частотных характеристик каскада

- •Практическое занятие № 3 Расчёт транзисторов оконечного каскада по выходной и входной цепям

- •4. Блок контроля освоения дисциплины Общие указания

- •4.1. Задание на контрольную работу и методические указания к её выполнению.

- •Методические указания к выполнению контрольной работы

- •Содержание расчётов

- •4.2. Задание на курсовой проект и методические указания по его выполнению

- •Задачи проектирования и порядок выполнения курсового проекта

- •4.2.2. Варианты заданий в зависимости от функционального назначения рассчитываемые усилите-ли делятся на основные четыре группы.

- •4.2.3. Выбор технических решений

- •4.2.3.1. Оконечный каскад

- •4.2.3.2. Выбор типа оконечных транзисторов

- •4.2.3.3. Энергетический расчёт режима оконечного каскада

- •Расчёт по выходной цепи и далее был выполнен в контрольной работе (раздел 4.1, пункты 1…15).

- •4.2.3.4. Расчёт коэффициента гармоник оконечного каскада

- •4.2.3.5. Предоконечный каскад

- •4.2.3.6. Блок предварительного усиления

- •Резистивные каскады оэ и ок

- •Каскад ои на полевом (униполярном) транзисторе

- •Дифференциальный каскад

- •4.2.3.7. Входные цепи

- •4.2.4. Построение схем и расчёт цепей общей отрицательной обратной связи

- •4.2.4.1. Выбор глубины общей оос

- •4.2.4.2. Построение схем общей оос

- •Цепь общей отрицательной обратной связи по переменному току

- •Расчёт цепи общей оос по переменному току

- •4.2.5. Проверка чувствительности усилителя

- •4.2.6. Питающие устройства

- •4.2.7. Построение структурных схем усилителей

- •Оформление курсового проекта

- •Курсовой проект должен содержать пояснительную записку с необходи-мым графическим материалом.

- •Тесты текущего контроля

- •Тест № 1

- •Тест № 2.

- •Тест № 3.

- •Тест № 4.

- •Тест № 5

- •Тест № 6

- •Тест № 7

- •Тест № 8

- •Правильные ответы на тренировочные тесты текущего контроля

- •Итоговый контроль вопросы к экзамену по дисциплине «схемотехника аналоговых электронных устройств»

- •Справочные данные транзисторов большой мощности

- •Содержание

Каскад ои на полевом (униполярном) транзисторе

Полевой транзистор применяется в усилителях звуковых частот в основ-ном для реализации каскада с весьма высоким входным сопротивлением. При этом каскад имеет коэффициент усиления по напряжению Ku > 1 (практически порядка 8...10). В целях снижения шумов следует выбирать полевой транзистор с управляющим p-n переходом как имеющий малый коэффициент шума Fш.

Рис. 5. Каскад с ОИ на полевом транзисторе

Известно, что в таком транзисторе исходные напряжения питания стока и затвора должны быть противоположной полярности относительно истока. По-этому подача смещения на затвор наиболее просто осуществляется по схеме, изображённой на рис. 5.

Направление исходного тока Ic0 и полярности питающих напряжений, по-казанные на этой схеме, относятся к полевому транзистору с p-каналом.

Вследствие крайне малого тока затвора (он имеет порядок 10-8 А) падение напряжения на сопротивлении Rз, выбираемом в соответствии с требуемым входным сопротивлением каскада (его порядок 2...5 МОм), практически отсут-ствует, напряжение смещения затвора Uзи0 = Ic0Rз.

Задаваясь минимальным напряжением Ucи0, достаточным для работы тран-зистора в области линейных участков его проходных характеристик и принимая ток Ic0 = (0,5...1) мА, определяют из указанных характеристик необходимое на-пряжение смещения затвора Uзи0. При этом сопротивление в цепи истока

,

(39)

,

(39)

напряжение Uзи = (0,5...0,7) В, Ic0 0,5 мА,

сопротивление в цепи стока

, (40)

, (40)

где Eк0 пр – общее напряжение питания каскада, Uси 0 = (3...5) В.

Коэффициент усиления каскада по напряжению в пределах рабочего диа-пазона частот

КuSRc~ , (41)

где S = (5…7) мА/В – статическая крутизна транзистора по току, а

,

,

где Rвх сл – входное сопротивление каскада, следующего за каскадом на поле-вом транзисторе (см. выражения 13 и 25).

В указанных частотных пределах входное сопротивление каскада Rвх = Rз, а его выходное сопротивление Rвых = Rс. При этом частотные искажения можно считать практически отсутствующими.

Температурная стабилизация вследствие относительно малой температур-ной зависимости тока Iс0, а также ввиду некритичности положения исходной рабочей точки в каскаде с малыми амплитудами напряжений и токов сигнала может не предусматриваться.

Дифференциальный каскад

В последнее время в качестве входного каскада усилителя широко приме-няется дифференциальный каскад, подавляющий синфазные шумы и помехи, а также обеспечивающий существенные преимущества при построении цепи об-щей ООС.

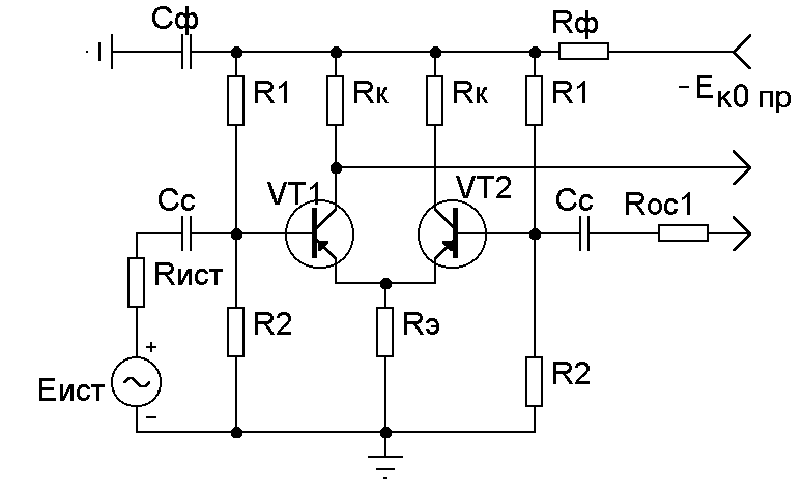

Схема дифференциального каскада приведена на рис. 6. В этой схеме на-пряжение сигнала подаётся на инвертирующий вход (транзистор VT1), а на-пряжение обратной связи – на неинвертирующий (транзистор VT2).

По цепи сигнала плечо дифференциального каскада на транзисторе VT1, работающем при включении ОЭ, изменяет фазу напряжения на . По цепи об-ратной связи сдвиг фаз отсутствует, так как транзистор VT2 используется при включении ОК, а транзистор VT1 – при включении ОБ.

Рис. 6. Дифференциальный каскад

Для эффективного подавления синфазных помех необходимо, чтобы вы-полнялось неравенство

.

.

В этом случае с достаточной точностью могут применяться такие прибли-жённые выражения:

входное сопротивление каскада по инвертирующему входу:

Rвх VT1 2Rвх оэ + Rдел ос ; (42)

коэффициент усиления по напряжению инвертирующего плеча

(43)

(43)

(коэффициент усиления этого плеча по отношению к петле общей ООС при оговорённом условии выбора Rэ можно считать также равным Ku VT1);

входное сопротивление каскада по инвертирующему входу:

Rвх VT2 2Rвх оэ + Rист ; (44)

коэффициент передачи по напряжению неинвертирующего плеча:

; (45)

; (45)

входное сопротивление инвертирующего и неинвертирующего плеч с учё-том делителя

Rвх VT1=Rвх VT1||Rдел;Rвх VT2=Rвх VT2||Rдел. (46)

В выражениях (40) ... (43):

Rвх оэ = rб + rэ (0 +1), (47)

Rдел ос = Rдел || Rос , (48)

Rист = Rист || Rдел; Rдел = R1 || R2 (49)

Rк ~ определяется из выражения (23).

В приведённых выражениях параметры транзисторов VT1 и VT2 предпо-лагаются одинаковыми.

Выбор и расчёт режима транзисторов выполняется следующим образом:

Uкэ0 = (0,1…0,2)Eк0 пр; URк = (0,4…0,5)Eк0 пр;

Iк0 = (0,2…0,5)мА; URф = 0,1Eк0 пр; (50)

;

;  , (51)

, (51)

причем необходимо, чтобы выполнялось неравенство

.

(52)

.

(52)