Гаврилов Основы ядерной електроники ч.1 2010

.pdf

цировать с шириной канала, то рассмотренная процедура позволяет уменьшить отклонение эффективной ширины канала от идеальной в (М+1) раз по сравнению с прямым измерением (без сдвига).

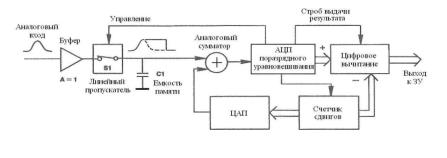

Упрощенная структурная схема АЦП поразрядного уравновешивания со скользящей шкалой приведена на рис. 3.21. К собственно АЦП ПУ добавлены М-разрядные счетчик и ЦАП, а также два сумматора: аналоговый и цифровой. Число сдвигов фиксируется

Рис. 3.21. Структурная схема АЦП поразрядного уравновешивания со скользящей шкалой

счетчиком, сдвиг имеет место после обработки каждого нового входного импульса. Выходное напряжение добавочного ЦАП, которое соответствует состояниям разрядов счетчика, складывается с очередным анализируемым напряжением в аналоговом сумматоре. Эта сумма оцифровывается АЦП ПУ. Таким образом реализуется скользящая шкала, но результат оцифровки оказывается больше истинного значения на произведенное число сдвигов. Поэтому на выходе используется цифровой сумматор, в котором из выходного кода АЦП ПУ вычитается код со счетчика, соответствующий произведенному числу сдвигов. Вычитание осуществляется по сигналу “Конец преобразования”, на выходе получается истинный цифровой эквивалент анализируемой амплитуды.

Основные характеристики некоторых отечественных и зарубежных САЦП поразрядного уравновешивания со скользящей шкалой приведены в табл. 3.2.

3.4.4. ПАРАЛЛЕЛЬНЫЕ И ПАРАЛЛЕЛЬНОПОСЛЕДОВАТЕЛЬНЫЕ АЦП

Параллельные АЦП – самые скоростные. Они позволяют как бы “мгновенно” (параллельно) получить все разряды кода, соответст-

131

Таблица 3.2 Основные параметры САЦП поразрядного уравновешивания

со скользящей шкалой

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Число |

Макс. ампл. |

Время |

Нелинейность, % |

Температ. нестаб, %/ºС |

Дополнит. |

|||

|

Модель |

Фирма |

вх. сигнала, |

преобраз., |

|

|

|

|

|

||

|

каналов |

|

|

|

|

|

данные |

||||

|

|

|

В |

мкс |

Ки |

Кд |

нуля |

|

наклона |

||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

АЦП-8К-П1 |

НПЦ «Аспект» |

8192–1024 |

5 |

3,5 |

0,03 |

0,3–1 |

- |

|

- |

PCI-плата в ПК |

|

АЦП-8К-П2 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Модуль Евро- |

|

БПА-03-8К-П1 |

НПЦ «Аспект» |

8192–1024 |

5 |

3,5 |

0,03 |

0,3–1 |

- |

|

- |

механика, |

|

|

|

|

|

|

|

|

|

|

|

Compact PCI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Приборное |

132 |

АЦП-USB-8К-П1 |

НПЦ «Аспект» |

8192–1024 |

5 |

3,5 |

0,03 |

0,3–1 |

- |

|

- |

исполнение, |

|

|

|

|

|

|

|

|

|

|

USB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Приборное |

|

АЦП-RS-8К-П1 |

НПЦ «Аспект» |

8192–1024 |

5 |

3,5 |

0,03 |

0,3–1 |

- |

|

- |

исполнение, |

|

|

|

|

|

|

|

|

|

|

|

RS232/485 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAMAC, |

|

AD 114 |

ORTEC |

16128 |

10 |

5 |

0,025 |

1 |

0,005 |

|

0,005 |

быстрая шина |

|

|

|

|

|

|

|

|

|

|

|

FERAbus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAMAC, |

|

AD 413A |

ORTEC |

8064 |

10 |

6 |

0,025 |

1 |

0,005 |

|

0,005 |

4-входовый, |

|

|

|

|

|

|

|

|

|

|

|

FERAbus |

|

|

|

|

|

|

|

|

|

|

|

|

|

ADC 8715 |

CANBERRA |

8192–56 |

10 |

0,9 |

0,025 |

0,9 |

0,005 |

|

0,005 |

NIM-модуль |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Программи- |

|

9635 |

CANBERRA |

8192–256 |

10 |

0,8 |

0,025 |

0,9 |

0,005 |

|

0,005 |

руемый NIM |

|

|

|

|

|

|

|

|

|

|

|

модуль |

|

|

|

|

|

|

|

|

|

|

|

|

вующего измеряемому напряжению. Фактически таким АЦП является входная часть рассмотренного в разделе 3.3 многоканального анализатора с параллельно включенными пороговыми схемами и индивидуальными регистраторами в каналах (рис. 3.10). Правда, выходные коды этой схемы специфичны. Действительно, цифровой эквивалент измеряемой амплитуды на выходах схем антисовпадений формируется как позиционный код, в котором единственное единичное состояние указывает на старшую из сработавших пороговых схем. Если же выходной код снимать непосредственно с пороговых схем, то это будет унитарный код, в котором единичные состояния соответствуют всем сработавшим схемам сравнения. Так как обычно результатом преобразования АЦП является двоичный код, то схема на рис. 3.10 требует дополнения в виде шифратора, преобразующего либо унитарный, либо позиционный код в двоичный. И конечно, для временного хранения выходного кода нужен буферный регистр результата.

Для n-разрядного АЦП требуется (2n–1) пороговых устройств (компараторов) и резистивный делитель, обеспечивающий эквидистантное распределение пороговых уровней. Резистивная линейка делителя из 2n резисторов должна быть достаточно низкоомной, чтобы входные токи компараторов не влияли на пороговые напряжения. Можно показать, что наибольшая относительная погрешность имеет место для порогового напряжения, равного половине максимального значения:

(δUпор)макс = δUэт + δUкп + δR/2,

где: δUэт – относительная погрешность эталонного источника напряжения; δUкп – максимальная погрешность из-за изменения порога чувствительности компараторов; δR – относительная погрешность резисторов делителя. Требование однородности и стабильности пороговых напряжений влечет за собой довольно жесткие ограничения на разброс параметров компараторов и резисторов, особенно при увеличении разрядности параллельного АЦП. Проблемы подобного рода лучше всего решаются при интегральном исполнении схемы. Такие АЦП выпускаются в виде монолитных ИС с разрешением 6–8 разрядов и временем преобразования от единиц до нескольких десятков наносекунд (табл. 3.3).

133

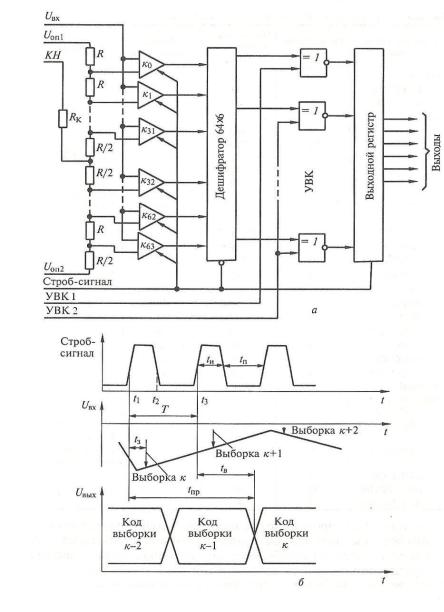

Рис. 3.22. Схема монолитного АЦП К1107ПВ1 (а) и временнáя диаграмма (б)

134

Рассмотрим особенности их применения на примере отечественного преобразователя К1107ПВ1 (рис. 3.22,а). Это 6-разрядный АЦП, содержащий 63 компаратора, делитель опорного напряжения из 64 резисторов, задающий пороговые уровни, дешифратор, элементы управления выходным кодом и регистр результата. Результат в данном случае может быть представлен в прямом или обратном двоичном коде, а также в прямом или обратном дополняющем коде. Тип выходного кода задается по выводам управления выходными кодами УВК1 и УВК2. Это может быть сделано как цифровыми сигналами с уровнями ТТЛ, так и постоянными уровнями “0”

и “1”.

Чтобы устранить ошибки считывания выходного кода, возможные при оцифровке меняющегося входного напряжения, используется принцип «мгновенной фиксации» унитарного кода на выходах компараторов. Для этого в состав компараторов введены запоминающие элементы (триггеры-защелки) и применено стробирование компараторов. Временная́ диаграмма работы АЦП приведена на рис. 3.22,б. Выборка («мгновенная фиксация») производится с задержкой 10–15 нс относительно положительного фронта стробимпульса. Кодирование результата стробирования начинается по заднему фронту стробирующего сигнала в момент t2 , а передача результата кодирования в выходной регистр – по переднему фронту следующего строб-импульса в момент t3. Время установления кода в выходном регистре не превышает минимально допустимого периода следования строб-импульсов. Это позволяет тем же передним фронтом второго строб-импульса производить новую выборку. Таким образом, полное время преобразования не превышает двух периодов следования сигналов стробирования Т, т.е. кодовое слово, соответствующее N-й выборке, появляется на выходе во время выборки (N+1). Такой алгоритм работы позволяет поднять частоту дискретизации преобразователя.

Для повышения быстродействия параллельных АЦП используются как технологические приемы (повышение граничных частот транзисторов), так и структурные. В последнем случае такие ИС содержат параллельные каналы с поочередным стробированием (рис. 3.23). Например, пока устройство выборки-хранения УВХ А следит за входным сигналом, АЦП А находится в режиме ожида-

135

ния и на его выходе присутствует код предыдущей выборки. В это время УВХ В работает в режиме хранения и его выходное напряжение преобразуется в цифровой код в АЦП В. После завершения преобразования код записывается в выходной регистр-фиксатор РВ.

Рис. 3.23. Структура АЦП с поочередным стробированием

Теперь УВХ А переходит в режим хранения, а УВХ В – в режим слежения за уровнем входного сигнала. Очередное преобразование осуществляет АЦП А и т.д. Организованная подобным образом 8-разрядная ИС ТКАД10С фирмы Tektronix обеспечивает эффективную частоту дискретизации 500 МГц при частоте преобразования отдельных АЦП 250 МГц.

Еще одним достоинством этой схемы является наличие встроенного согласующего усилителя. Вход обычного параллельного АЦП, объединяющий входы (2n–1) компараторов, имеет большую суммарную емкость (до нескольких сотен пикофарад) и нелинейное переменное (в зависимости от числа сработавших компараторов) входное сопротивление. Широкополосное согласование такого входа с линией передачи, по которой поступает входной сигнал, требует включения буферного каскада. С учетом встроенного усилителя ИС ТКАД10С имеет входную емкость 1 пФ и входное сопротивление 50 Ом. Дифференциальный вход усилителя помогает решать проблемы помехоустойчивости.

До недавнего времени параллельные АЦП в основном использовались в экспериментах физики высоких энергий (на ускорителях), где принципиально важно малое мертвое время преобразователя и могут быть снижены требования к разрешающей способности. Однако в последние годы получили распространение цифровые спектрометрические тракты (см. раздел 3.7), когда оцифровка сигнала выполняется возможно раньше, ближе к детектору и вся

136

последующая работа производится уже с цифровой копией сигнала. Быстродействие параллельных АЦП как раз и позволяет получать «мгновенные» цифровые копии анализируемого сигнала.

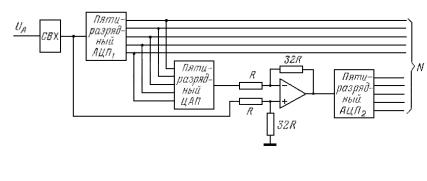

Увеличение разрядности параллельных АЦП сопряжено со значительными трудностями: удвоением аппаратных средств на каждый новый разряд, ужесточением требований к однородности и стабильности пороговых уровней, разрастанием шифратора, снижающим быстродействие и создающим проблемы разводки межсоединений. Поэтому при необходимости улучшить разрешение с сохранением приемлемого быстродействия обращаются к ступенчатым параллельно-последовательным схемам. В этих преобразователях используются два или более (по числу ступеней) параллельных АЦП, которые работают последовательно во времени. На рис. 3.24 приведена структурная схема десятиразрядного парал- лельно-последовательного АЦП, состоящего из двух пятиразрядных параллельных преобразователей, параллельного пятиразрядного ЦАП, операционного усилителя ОУ, включенного по дифференциальной схеме, и схемы выборки-хранения СВХ.

Рис. 3.24. Параллельно-последовательный АЦП

Анализируемый сигнал поступает на вход первого параллельного АЦП, который осуществляет грубое кодирование, выдавая на выходе старшие 5 разрядов кода. Одновременно сигнал запоминается СВХ на все время преобразования. Параллельная работа АЦП1 и СВХ организована для повышения быстродействия схемы в целом и возможна, если в АЦП1 использованы компараторы со стробированием, имеющие в своем составе запоминающие триггерызащелки. Результат грубого кодирования преобразуется ЦАП

137

Таблица 3.3 Параллельные и параллельно-последовательные АЦП

в монолитном исполнении

|

|

|

|

Время преобра- |

Диапазон |

|

Тип |

Производитель |

Число |

зования, нс |

входных |

|

разрядов |

(частота дискре- |

напряжений, |

||

|

|

|

|||

|

|

|

|

тизации, МГц) |

В |

|

К1107ПВ1 |

РФ |

6 |

100 |

0–2 |

|

К1107ПВ3 |

РФ |

6 |

20 |

0–2 |

|

HS9582 |

Hybrid Systems |

6 |

70 |

0–5 |

Параллельные |

К1107ПВ2 |

РФ |

8 |

100 |

0–2 |

AD9002 |

Analog Devices |

8 |

7 |

–2–0 |

|

CXA1176K |

Sony |

8 |

3 |

–2–0 |

|

ADC081500 |

National |

8 |

(1500) |

|

|

Semiconductor |

|

||||

|

|

|

|

||

MAX 108 |

Maxim |

8 |

(1500) |

|

|

|

HADC77600 |

Honywell |

10 |

20 |

±0,5; ±2 |

|

AD9410 |

Analog Devices |

10 |

(200) |

|

|

MAX 1215N |

Maxim |

12 |

(250) |

|

|

AD9233 |

Analog Devices |

12 |

(145) |

|

-последовательные |

AD7820 |

Analog Devices |

8 |

|

0–5 |

|

|

|

|

|

|

ADC1175-50 |

National |

8 |

(50) |

|

|

Semiconductor |

|

||||

|

|

|

|

||

|

|

|

|

|

|

ADC08200 |

National |

8 |

(200) |

|

|

Semiconductor |

|

||||

|

|

|

|

||

|

|

|

|

|

|

AD9201 |

Analog Devices |

10 |

(20) |

|

|

Параллельно |

|

||||

|

|

|

|

|

|

ADC10030 |

National |

10 |

(30) |

|

|

Semiconductor |

|

||||

|

|

|

|

||

AD9003 |

Analog Devices |

12 |

|

0–5 |

|

|

|

|

|

|

в напряжение, которое поступает на один из входов усилителявычитателя на ОУ. На другой вход ОУ подается анализируемое напряжение, запомненное на СВХ. Разность усиливается в 25 раз, чтобы можно было использовать АЦП2 с тем же диапазоном входного напряжения, что и АЦП1. Усиленная разность поступает на АЦП2, на выходе которого формируются младшие разряды кода.

Для получения малого времени преобразования ступенчатого АЦП необходимо использовать быстродействующий ОУ и ЦАП с малым временем установления. Погрешность рассматриваемого

138

АЦП определяется прежде всего ЦАП и дифференциальным усилителем. Их погрешности приводят к некомпенсируемым ошибкам, так как их выходные напряжения передаются на вход следующего преобразователя. Поэтому их приведенная погрешность должна быть не более 2–n, т.е. единицы младшего разряда всего АЦП. Тем не менее обеспечение приемлемой дифференциальной нелинейности каналов в местах стыковки старших и младших разрядов остается узким местом. Поэтому для улучшения однородности ширины каналов иногда применяют рассмотренный в предыдущем разделе метод скользящей шкалы. Погрешность АЦП1 также не должна превышать единицу младшего разряда всего ступенчатого АЦП.

Восьми–двенадцатиразрядные параллельно-последовательные АЦП выпускаются серийно в виде монолитных ИС. Параметры некоторых из них приведены в табл. 3.3.

3.4.5. ИНТЕГРИРОВАННЫЕ СИСТЕМЫ СБОРА ДАННЫХ

Естественным направлением развития технологии сбора и преобразования аналоговой информации в цифровую и обратно является объединение на кристалле высокопроизводительного АЦП и цифровых средств последующей обработки информации. Результатом этих усилий стали полностью интегрированные системы сбора данных – системы на кристалле, часто называемые аналоговыми микроконтроллерами (микроконверторами). Рассмотрим некоторые их особенности на примере одной из первых БИС такого рода

C8051F020 фирмы Silicon Laboratories (рис.3. 25).

В аналоговый блок рассматриваемой БИС входят один 8-раз- рядный и один 12-разрядный АЦП поразрядного уравновешивания, а также два 12-разрядных ЦАП. Кроме того, имеются операционный усилитель с программируемым коэффициентом усиления (PGA), аналоговый мультиплексор (8 и 9 каналов), 2 компаратора, источник опорного напряжения и температурный датчик. Источник опорного напряжения 2,43 В, поддерживающий работу АЦП и ЦАП, имеет температурную нестабильность 15 ppm/ºC и обеспечивает максимальный ток нагрузки 200 мкА. При использовании внешнего источника опорного напряжения этот узел может быть программно отключен.

139

140

Рис. 3.25. Структурная схема БИС микроконтроллера C8051F020