- •Лабораторная работа 1 температурная зависимость проводимости полупроводниковых материалов

- •1.1 Основные понятия и определения

- •1.2. Описание образцов, использованных в работе

- •1.3. Описание установки

- •1.4. Проведение испытаний

- •1.5. Обработка результатов.

- •1.6. Контрольные вопросы

- •Лабораторная работа 2 исследование полупроводниковых выпрямительных диодов

- •2.1. Основные понятия и определения

- •2.2. Описание установки

- •2.3. Проведение исследований

- •2.3.1. Исследование прямой ветви вольт-амперной характеристики

- •2.3.2. Исследование обратной ветви вольт-амперной характеристики

- •2.3.3. Исследование частотных свойств выпрямительного диода

- •2.3.4 Исследование вольт-амперной характеристики диодов при повышенной температуре

- •2.4. Обработка результатов

- •2.5. Контрольные вопросы

- •Лабораторная работа 3 исследование статических характеристик и параметров биполярного транзистора

- •3.1. Основные понятия и определения

- •3.2. Исследование статических характеристик биполярного транзистора методом характериографа

- •3.2.1. Описание установки

- •3.2.2. Исследование статических характеристик транзистора

- •3.2.3. Исследование статических коэффициентов передачи тока транзистора

- •3.2.4. Измерение обратного тока коллектора

- •3.2.5. Исследование пробивного напряжения транзистора

- •3.3. Обработка результатов и расчет параметров

- •3.5. Контрольные вопросы

- •Лабораторная работа 4 исследование статических характеристик и параметров полевых транзисторов

- •4.1. Основные понятия и определения

- •4.2. Описание установки

- •4.3. Проведение измерений

- •4.4. Обработка результатов и расчет параметров

- •4.5. Контрольные вопросы

- •Лабораторная работа 5 исследование биполярного транзистора при работе на малом переменном сигнале

- •5.1. Основные понятия и определения

- •5.2. Описание установки

- •5.3. Проведение испытаний

- •5.3.1. Исследование h-параметров транзистора в схеме с общей базой

- •5.3.2. Исследование h-параметров транзистора в схеме с общим эмиттером

- •5.3.3. Исследование частотных зависимостей коэффициентов передачи токов эмиттера и базы

- •5.4. Обработка результатов

- •5.5. Контрольные вопросы

- •Лабораторная работа 6 исследование импульсных свойств биполярного транзистора

- •6.1. Основные понятия и определения

- •6.2. Схема установки

- •6.3. Проведение испытаний

- •6.3.1. Подготовка к испытаниям

- •6.3.2. Исследование зависимости времени нарастания и времени рассасывания от напряжения источника питания в цепи коллектора

- •6.3.3. Исследование зависимости времени нарастания и времени рассасывания от амплитуды импульса тока эмиттера

- •6.4. Обработка результатов

- •6.5. Контрольные вопросы

- •Лабораторная работа 7 исследование интегральных микросхем

- •7.1. Основные понятия и определения

- •7.2. Описание установки

- •7.3. Проведение испытаний

- •7.3.1. Определение логических операций, выполняемых полупроводниковой микросхемой

- •7.3.2. Исследование входной и прямой передаточной характеристик логической полупроводниковой микросхемы

- •7.3.3. Определение мощности, потребляемой логической полупроводниковой микросхемой

- •7.3.4. Изучение конструкции гибридной имс

- •7.4. Обработка результатов и расчет параметров

- •7.5. Контрольные вопросы

- •Лабораторная работа 8 исследование полупроводниковых источников излучения

- •8.1. Основные понятия и определения

- •8.2. Описание установки

- •8.3 Проведение измерений

- •8.3.1. Исследование спектральных характеристик сид

- •8.3.2. Исследование яркостных и вольт-амперных характеристик сид

- •8.3.3. Исследование яркостной характеристики ил

- •8.3.4. Исследование спектральных характеристики ил

- •8.4. Обработка результатов

- •9.1. Основные понятия и определения

- •9.2. Описание установки

- •9.3. Проведение испытаний

- •9.3.1. Исследование спектральной характеристики фд

- •9.3.2. Исследование световых характеристик фд

- •9.4. Обработка результатов

- •9.5. Контрольные вопросы

- •Лабораторная работа 10 исследование полупроводниковых стабилитронов и стабистора

- •10.1. Основные понятия и определения

- •10.2. Установка для исследований

- •10.3. Порядок проведения исследований

- •10.3.1. Исследование вах стабилитрона

- •10.3.2. Исследование параметров стабилитронов

- •10.3.3. Исследование параметрического стабилизатора напряжения

- •10.4. Обработка экспериментальных результатов и расчет параметров

- •10.5. Контрольные вопросы

- •Лабораторная работа 11 исследование тиристора

- •11.1. Основные понятия и определения

- •11.2. Описание установки

- •11.3. Проведение исследований

- •11.3.1. Исследование вольт-амперной характеристики тиристора

- •11.3.2. Измерение параметров тиристора

- •11.3.3. Исследование зависимости напряжения включения тиристора от тока управляющего электрода

- •11.3.4. Исследование параметров тиристора при повышенной температуре

- •11.3.5. Исследование регулятора мощности

- •11.4. Обработка результатов

- •11.5. Контрольные вопросы

- •Лабораторная работа 12 исследование туннельных диодов

- •12.1. Основные понятия и определения

- •12.2. Описание установок для проведения исследований

- •12.2.1. Схема для исследования вольт-амперной характеристики тд

- •12.2.2. Схема для изучения эффекта дискретно-аналоговой памяти

- •12.2.3. Схема для исследования эффектов усиления и генерации электрических сигналов

- •12.3. Порядок проведения исследований

- •12.3.1. Исследование вольт-амперной характеристики

- •12.3.2. Исследование функции дискретно-аналоговой памяти

- •12.3.3. Изучение эффекта усиления

- •12.3.4. Изучение эффекта генерации

- •12.4. Обработка результатов

- •12.5. Контрольные вопросы

- •Список рекомендованной литературы

- •Содержание

Лабораторная работа 7 исследование интегральных микросхем

7.1. Основные понятия и определения

Интегральные микросхемы (ИМС) по функциональному назначению разделяют на аналоговые и цифровые. Аналоговые ИМС предназначены для преобразования и обработки сигналов, изменяющихся по закону непрерывной функции. Цифровые ИМС предназначены для преобразования и обработки сигналов, изменяющихся по закону дискретной функции. Они могут быть изготовлены как по полупроводниковой, так и по гибридной технологии. Цифровые ИМС, выполняющие различные логические операции, обычно называют логическими. В логических микросхемах входные и выходные сигналы могут принимать только два значения, соответствующие логическому нулю и логической единице.

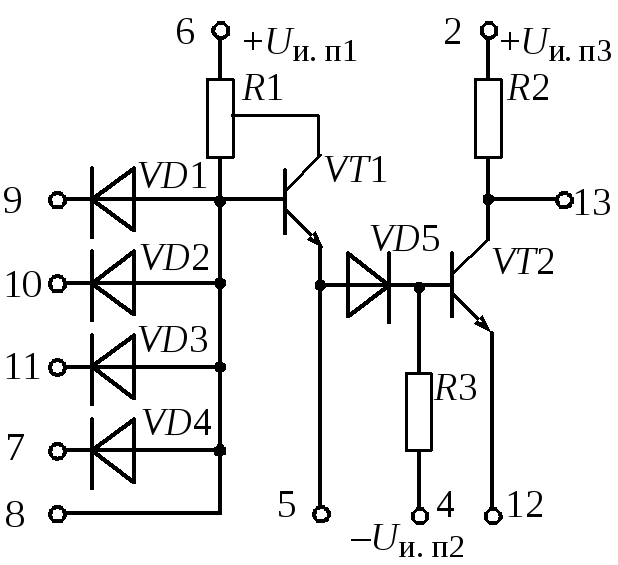

В исследуемой в работе цифровой полупроводниковой ИМС (рис. 7.1, а) логическому нулю соответствует небольшое положительное напряжение (низкий уровень), а логической единице – более высокое положительное напряжение (высокий уровень). При малых входных напряжениях (логических нулях на входе) входные диоды VD1–VD4 открыты, и ток, определяемый резистором R1 и напряжением источника питания Uи. п1, проходит через эти диоды в источники входных сигналов. При этом отсутствуют базовые токи у транзисторов VT1 и VT2, транзистор VT2 оказывается в выключенном состоянии (в режиме отсечки). Потенциал на коллекторе транзистора VT2 практически равен Uи. п3, т. е. соответствует логической единице. Такое состояние схемы сохраняется, если хотя бы на одном входе есть низкий потенциал.

При появлении на всех входах высоких потенциалов логической единицы произойдет закрывание всех входных диодов. Ток от источника Uи. п1, текущий в базу транзистора VT1 и усиленный этим транзистором, откроет транзистор VT2, и он перейдет во включенное состояние (в режим насыщения). На коллекторе транзистора при этом будет низкий потенциал, что соответствует напряжению логического нуля. Следовательно, исследуемая микросхема выполняет логическую операцию И–НЕ, т. е. отрицание логического умножения.

|

|

|

|

|

а |

б |

в |

|

Рис. 7.1. Полупроводниковая логическая микросхема: а – схема; характеристики: б – входная; в – передаточная |

||

В работе исследуются основные характеристики полупроводниковой логической микросхемы – входная и прямая передаточная (см. рис. 7.1, б и в). Состояние полупроводниковой микросхемы, при котором транзистор VT2 выключен, называют выключенным состоянием. Переход транзистора в режим насыщения переводит микросхему во включенное состояние.

На

передаточной характеристике показаны

точки, соответствующие выключенной

(точка А)

и включенной (точка D)

микросхеме. Точки В

и С

определяют границы переходной области

между выключенным и включенным состояниями

– область активного режима работы

транзистора VT2,

при котором модуль коэффициента передачи

схемы по напряжению

![]() .

.

На рис. 7.2 изображена топология полупроводниковой ИМС (форма, геометрические размеры и взаимное расположение элементов). В монокристалле полупроводника (его границы обозначены жирной линией) путем избирательного введения примесей создаются области с различным типом электропроводности (диодные и транзисторные структуры), а также участки с определенным сопротивлением – диффузионные резисторы (на рис. 7.2 они имеют серую заливку). Объединение элементов в соответствии с электрической схемой осуществляется пленочными проводниками (рис. 7.2, б, темная заливка) – они оканчиваются темными окружностями на краю монокристалла. К этим окружностям привариваются навесные проводники, соединенные с выводами ИМС, закрепленными на прямоугольных контактных площадках (на рис. 7.2 они не показаны), расположенных вблизи монокристалла по его периметру. Выводы ИМС нумеруются против часовой стрелки, номера выводов указаны на рис. 7.1, а.

|

|

|

|

а |

б |

|

Рис 7.2. Топология полупроводниковой ИМС: а – без электрических соединений б – с пленочными проводниками |

|

Основой гибридной ИМС является диэлектрическая подложка из ситалла или керамики, на которую послойно наносят пленки различных материалов (проводниковых, диэлектрических или магнитных) с одновременным формированием из них элементов и их соединений.

Существенным недостатком пленочной технологии является невозможность изготовления активных элементов схемы. Поэтому ИМС, изготовленные по пленочной технологии, содержат пленочные пассивные элементы (резисторы, конденсаторы, катушки индуктивности) и навесные активные полупроводниковые приборы – компоненты (транзисторы, диоды и бескорпусные кристаллы полупроводниковых микросхем), изготовленные по полупроводниковой технологии. Таким образом, ИМС является гибридом двух технологий, откуда и происходит название такого типа схем. Необходимость использования активных компонентов в гибридных ИМС позволяет применить в них и навесные пассивные компоненты (конденсаторы и катушки индуктивности) больших номиналов, которые невозможно изготовить по пленочной технологии. Однако использование навесных компонентов и необходимость подсоединения их контактов к схеме существенно снижает надежность гибридных ИМС по сравнению с полупроводниковыми. Другим недостатком гибридных ИМС является меньшая степень интеграции, что связано с размерами навесных компонентов и контактов к ним. Однако стоимость разработки и изготовления гибридных ИМС существенно ниже, чем полупроводниковых, что позволяет изготавливать специализированные схемы небольшими партиями. Кроме того, качество пассивных элементов (диапазон номиналов, точность номинала, температурная стабильность) в гибридных ИМС может быть существенно выше, чем в полупроводниковых, что определяет их широкое использование в аналоговой схемотехнике.

Целью работы является исследование электрических параметров и топологии полупроводниковой логической и гибридной аналоговой ИМС.