- •Краткие правила по технике безопасности при проведении лабораторных работ в лаборатории.

- •Правила проведения занятий в лаборатории. Подготовка к работе.

- •Подготовка к лаборатории

- •Оформление отчёта:

- •Описание лабораторной установки.

- •Порядок подготовки к работе и включения стенда.

- •Система моделирования Electronics Workbench

- •Структура окна и система меню

- •Меню File

- •Меню Edit

- •Меню Circuit

- •Меню Analysis

- •Меню Window

- •Меню Help

- •Создание схем

- •Технология подготовки схем

- •Группа Favorites

- •Группа Sources

- •Группа Basic

- •Группа Diodes

- •Группа Transistors

- •Мультиметр

- •Функциональный генератор

- •Осциллограф

- •Измеритель ачх и фчх

- •Лабораторная работа №1.

- •Результаты измерений, проведенных на осциллографах с1-55, 6502

- •Органы управления и регулировки.

- •Осциллограф 2-х лучевой с1-55

- •Органы управления и регулировки. Передняя панель.

- •Осциллограф 2-х лучевой (Electronics Workbench)

- •Органы управления и регулировки.

- •Проведение измерений с помощью осциллографа.

- •1) Измерение постоянного напряжения.

- •2) Измерение синусоидального сигнала.

- •3) Измерение временных интервалов и амплитуды с помощью калибратора.

- •4) Измерение угла сдвига фаз.

- •5) Измерение длительности импульсов.

- •6) Режимы развертки.

- •7) Непрерывная развертка с синхронизацией исследуемым сигналом.

- •8) Синхронизация от внешнего источника.

- •9) Внешняя модуляции луча но яркости.

- •Структурная схема осциллографа

- •Выполнение работы.

- •Лабораторная работа № 2. Исследование полупроводникового диода.

- •Часть I.

- •Пример расчета

- •Пояснения к работе

- •Условно графические обозначения п/п диодов.

- •Лабораторная работа № 3 Исследование неуправляемых выпрямительных устройств

- •Контрольные вопросы:

- •Лабораторная работа №4 Изучение свойств усилителя при различных способах включения транзистора.

- •Лабораторная работа №5 Исследование усилительного каскада на биполярном транзисторе, включённом по схеме с общим эмиттером (оэ) в режиме класса а.

- •Входные и выходные характеристики транзисторов:

- •Лабораторная работа №6.

- •Лабораторная работа №7.

- •Лабораторная работа №8.

- •Лабораторная работа 9 исследование конъюнктура диодной логики

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания для самопроверки

- •Лабораторная работа 10 исследование дизъюнктора диодной логики

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания и порядок выполнения работы

- •Задания для самопроверки

- •Лабораторная работа 11

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Особенности принципиальной схемы

- •Задания и порядок выполнения работы

- •Задания для самопроверки

- •Лабораторная работа 12

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания для самопроверки

- •Лабораторная работа 13 исследование основного элемента транзисторно-транзисторной логики

- •Краткие сведения из теории Общие сведения

- •Логика работы

- •Задания для самопроверки

- •Лабораторная работа 14 исследование основного элемента эмиттерно-связанной логики

- •Краткие сведения из теории Общие сведения

- •Логика работы

- •Задания для самопроверки

- •Лабораторная работа 15 исследование триггерных схем

- •Краткие сведения из теории

- •Асинхронные триггеры

- •Асинхронный т-триггер

- •Задания для самопроверки

Задания для самопроверки

1. Объяснить работу элемента положительной и отрицательной логики. Использовать для этого временные диаграммы работы (см. рис. 6.1, б, д).

2. Объяснить принцип работы элемента, назначение компонентов схемы. Дать анализ статического режима работы схемы. Объяснить основные аналитические соотношения.

3. Объяснить методику получения основных статических характеристик: входной, передаточной и выходной. Дать анализ основных аналитических соотношений, касающихся указанных характеристик. Пояснить методику получения и семантику основных статических параметров.

4. Дать анализ динамического режима работы элемента по этапам: включение, выключение. Пояснить основные аналитические выражения. Дать анализ временных диаграмм по переходным процессам.

5. Пояснить методику определения мощности потребления элементом для статического и динамического режимов. Дать анализ основных аналитических выражений, относящихся к данному вопросу.

6. Рассказать об особенностях установки для исследования элементов ЭСЛ. Указать назначение элементов управления, контроля и индикации. Объяснить порядок работы с установкой.

Лабораторная работа 15 исследование триггерных схем

Цель работы: ознакомление с основными схемами асинхронных и синхронных триггеров; изучение принципа действия и логики работы асинхронных и синхронных триггеров; освоение методики исследования асинхронных и синхронных триггеров в статическом и динамическом режимах, определение основных параметров асинхронных и синхронных триггеров.

Краткие сведения из теории

Триггер

– релейный

элемент с двумя устойчивыми состояниями,

выходной сигнал которого может изменяться

в зависимости от входных сигналов,

принимая лишь одно из двух устойчивых

состояний. Как элемент ЭВМ триггер

предназначен для хранения двоичной

информации, т. е.

«1» или «0».

Специальной организацией схемы элемента

можно обеспечить запись, считывание,

стирание и индикацию состояний

двоичной информации триггера. Триггер

в общем случае является сложным элементом

и состоит из двух частей: управляющей

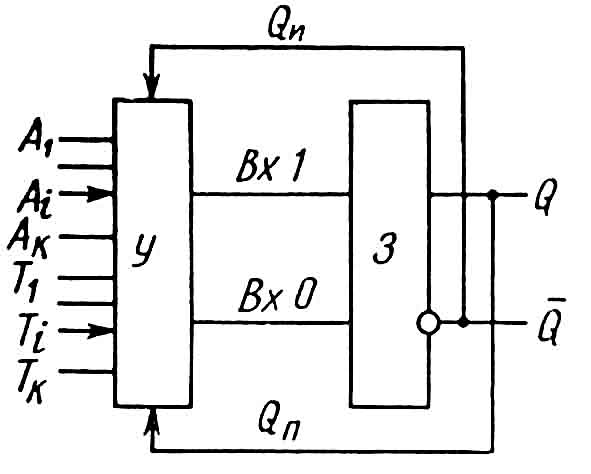

и запоминающей. На рис.

7.1 показана

схема триггера, где

![]() ,

,

![]() ,

...,

,

...,

![]() –информационные

статические входы;

–информационные

статические входы;

![]() – динамический информа-ционный вход;

– динамический информа-ционный вход;

![]() ,

,

![]() ,

...,

,

...,

![]() – тактовые статические входы (входы

синхронизации);

– тактовые статические входы (входы

синхронизации);

![]() – динамический

тактовый вход;

– динамический

тактовый вход;

![]() – входы собственно триггера (запоминающей

части), устанавливающие триггер в

состояние «1» (Bx1)

и состояние «0»

(Bx0).

Если триггер изменяет свое состояние

при изменении сигнала на тактовом

входе из «0» в

«1», то он

имеет прямой динамический вход, если

из

«1» в «0»,

то – инверсный динамический вход С;

Q,

– входы собственно триггера (запоминающей

части), устанавливающие триггер в

состояние «1» (Bx1)

и состояние «0»

(Bx0).

Если триггер изменяет свое состояние

при изменении сигнала на тактовом

входе из «0» в

«1», то он

имеет прямой динамический вход, если

из

«1» в «0»,

то – инверсный динамический вход С;

Q,

![]() – прямой

и инверсный выходы;

– прямой

и инверсный выходы;

![]() ,

,

![]() – обратные

связи с прямого и инверсного выходов

запоминающей части триггера на его

управляющую часть; У

– управляющая

часть (предназначена для реализации

входной логики и формирования сигналов);

З

–запоминающая

часть (собственно триггер, предназначенный

для хранения информации на триггере,

характеризует состояние триггера в

целом).

– обратные

связи с прямого и инверсного выходов

запоминающей части триггера на его

управляющую часть; У

– управляющая

часть (предназначена для реализации

входной логики и формирования сигналов);

З

–запоминающая

часть (собственно триггер, предназначенный

для хранения информации на триггере,

характеризует состояние триггера в

целом).

В частном случае в схеме триггера могут отсутствовать, например, тактовые входы или управляющая часть в целом.

П

Рис. 7.1

Примечание.

При необходимости к буквам допускается

добавлять цифры, например

![]() и т. д.

и т. д.

Существует большое разнообразие схем триггеров: RS, JK, RST и др. Указанное разнообразие обусловлено возможностью изменения структуры управляющей части.

По способу записи информации различают триггеры асинхронные и синхронные (тактируемые). В асинхронных триггерах запись информации осуществляется непосредственно с поступлением информационного сигнала на их вход. В синхронных триггерах, имеющих информационные и синхронизирующие входы, запись информации осуществляется только при подаче синхронизирующего импульса.

По

способу организации логических связей

различают триггеры с раздельной

установкой состояний «0» и

«1» (RS-триггеры);

со счетным входом (Т-триггеры); универсальные

триггеры с раздельной установкой

состояний «0» и

«1» (JK-триггеры);

с приемом информации по одному входу

(D-триггеры);

универсальные с управляемым приемом

информации по одному входу

(DV-триггеры),

комбинированные (RST-,

JKRS-,

DRS-триггеры)

и со сложной входной логикой.

По

способу организации логических связей

различают триггеры с раздельной

установкой состояний «0» и

«1» (RS-триггеры);

со счетным входом (Т-триггеры); универсальные

триггеры с раздельной установкой

состояний «0» и

«1» (JK-триггеры);

с приемом информации по одному входу

(D-триггеры);

универсальные с управляемым приемом

информации по одному входу

(DV-триггеры),

комбинированные (RST-,

JKRS-,

DRS-триггеры)

и со сложной входной логикой.

В настоящее время разработаны и используются различные триггеры в интегральном исполнении, построенные как на основе логических, так и других элементов. В данной работе исследуются триггеры, построенные на основе логических элементов.

Простейшей схемой триггера является схема, состоящая из двух элементов НЕ (рис. 7.2, а), где , , – информационные входы. 1, 2 – узлы, объединяющие информационные входы и сигналы обратной связи. С точки зрения требований логических построений схем, объединение сигналов в узлах 1, 2 некорректно. Поэтому схему, изображенную на рис. 7.2, а, следует представить в виде схемы, показанной на рис. 7.2, б. Так как сочетание элементов ИЛИ, НЕ является элементом Пирса, то, следовательно, схему на рис. 7.2, б можно представить так, как показано на рис. 7.2, в.

Таким образом, первым основным вариантом логической организации схемы триггера являются два элемента Пирса, объединенные по схеме, изображенной на рис. 7.2, в.

В соответствии с принципом двойственности схем ИЛИ, И триггер, построенный так, как показано на рис. 7.2, в, можно представить схемой, изображенной на рис. 7.2, г. Так как сочетание элементов И – НЕ является элементом Шеффера, то схему триггера, представленную на рис. 7.2, г, можно реализовать на основе элементов Шеффера (рис. 7.2, д).

Таким образом, вторым основным вариантом логической организации схемы триггера являются два элемента Шеффера, объединенные по схеме на рис. 7.2, д. Положения входов , триггера (рис. 7.2, д) взаимно противоположны соответствующим входам триггера (рис. 7.2, в). Соответственно третьим основным вариантом логической организации схемы триггера являются два элемента И–ИЛИ–НЕ, объединенные по схеме, показанной на рис. 7.2, е.

Существует большое разнообразие логических структур триггерных схем. Простейшая структура триггера содержит два логических элемента с инверсными выходами. Такой триггер имеет два информационных входа, предназначенных для установки его в состояние «0» и «1». Эти входы обозначают буквами R и S (Reset – сброс и Set–установка) соответственно. Такой триггер называют RS-триггером. Подключая на входы RS-триггера логические элементы, управляемые внешними сигналами и (или) сигналами обратной связи, можно получить другие более сложные триггеры. Наиболее употребительные сочетания RS-триггеров и входных логических элементов получили специальные названия. При этом тип входной логики обозначается одной или несколькими буквами, помещаемыми перед словом триггер. Так, D-триггер (Delay–задержка) имеет лишь один информационный вход – D-вход, DV-триггер – это D-триггер с добавлением управляющего V-входа Т-триггер (триггер со счетным входом, Toggle – кувыркаться) при поступлении каждого сигнала на счетный вход меняет свое состояние на противоположное, RST-триггер имеет входы R, S, T.

Синхронные триггеры – триггеры, входные информационные сигналы которых стробируются периодическими сигналами. Под стробированием сигналов понимается выделение из информационных сигналов той части, которая свободна от ложных сигналов. Процесс стробирования периодическими сигналами называется синхронизацией, а время, равное периоду следования синхронизирующих сигналов, – тактом. Синхронные триггеры могут быть однотактными, двухтактными, п-тактными (многотактными). Таким образом, в синхронных триггерах в отличие от асинхронных запись информации осуществляется только при подаче синхронизирующего импульса. При этом переключение триггера происходит либо одновременно с поступлением синхронизирующего сигнала, либо с задержкой после окончания действия синхросигнала. Достоинством синхронных триггеров является также возможность исключения эффекта состязаний (гонок) посредством стробирования.

Синхронные триггеры реализуются посредством использования асинхронных триггеров. При построении синхронных триггеров на основе асинхронных необходимо учитывать в уравнениях, описывающих работу синхронных триггеров, наличие сигнала синхронизации (С). Так, в уравнении синхронного RS-триггера вместо сигналов R и S необходимо использовать сочетание сигналов CR, CS. По способу синхронизации различают триггеры: синхронные со статическим управлением записью, синхронные двухступенчатые, синхронные динамическим управлением записью. В свою очередь, среди синхронных триггеров различают триггеры, срабатывающие по уровню (в момент прихода сигнала синхронизации), и триггеры с внутренней задержкой, срабатывающие после окончания сигнала синхронизации. Кроме того, синхронные триггеры делятся на однотактные и многотактные. К многотактным относятся такие триггеры, для управления работой которых требуется серия из п тактовых сигналов. Формирование нового состояния в них завершается с поступлением п-тактового сигнала. Тогда при п=2 получим двухтактный, при п=3 – трехтактный триггер и т. д. Синхронные триггеры получили большее распространение в современных ЭВМ, чем асинхронные.