- •Краткие правила по технике безопасности при проведении лабораторных работ в лаборатории.

- •Правила проведения занятий в лаборатории. Подготовка к работе.

- •Подготовка к лаборатории

- •Оформление отчёта:

- •Описание лабораторной установки.

- •Порядок подготовки к работе и включения стенда.

- •Система моделирования Electronics Workbench

- •Структура окна и система меню

- •Меню File

- •Меню Edit

- •Меню Circuit

- •Меню Analysis

- •Меню Window

- •Меню Help

- •Создание схем

- •Технология подготовки схем

- •Группа Favorites

- •Группа Sources

- •Группа Basic

- •Группа Diodes

- •Группа Transistors

- •Мультиметр

- •Функциональный генератор

- •Осциллограф

- •Измеритель ачх и фчх

- •Лабораторная работа №1.

- •Результаты измерений, проведенных на осциллографах с1-55, 6502

- •Органы управления и регулировки.

- •Осциллограф 2-х лучевой с1-55

- •Органы управления и регулировки. Передняя панель.

- •Осциллограф 2-х лучевой (Electronics Workbench)

- •Органы управления и регулировки.

- •Проведение измерений с помощью осциллографа.

- •1) Измерение постоянного напряжения.

- •2) Измерение синусоидального сигнала.

- •3) Измерение временных интервалов и амплитуды с помощью калибратора.

- •4) Измерение угла сдвига фаз.

- •5) Измерение длительности импульсов.

- •6) Режимы развертки.

- •7) Непрерывная развертка с синхронизацией исследуемым сигналом.

- •8) Синхронизация от внешнего источника.

- •9) Внешняя модуляции луча но яркости.

- •Структурная схема осциллографа

- •Выполнение работы.

- •Лабораторная работа № 2. Исследование полупроводникового диода.

- •Часть I.

- •Пример расчета

- •Пояснения к работе

- •Условно графические обозначения п/п диодов.

- •Лабораторная работа № 3 Исследование неуправляемых выпрямительных устройств

- •Контрольные вопросы:

- •Лабораторная работа №4 Изучение свойств усилителя при различных способах включения транзистора.

- •Лабораторная работа №5 Исследование усилительного каскада на биполярном транзисторе, включённом по схеме с общим эмиттером (оэ) в режиме класса а.

- •Входные и выходные характеристики транзисторов:

- •Лабораторная работа №6.

- •Лабораторная работа №7.

- •Лабораторная работа №8.

- •Лабораторная работа 9 исследование конъюнктура диодной логики

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания для самопроверки

- •Лабораторная работа 10 исследование дизъюнктора диодной логики

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания и порядок выполнения работы

- •Задания для самопроверки

- •Лабораторная работа 11

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Особенности принципиальной схемы

- •Задания и порядок выполнения работы

- •Задания для самопроверки

- •Лабораторная работа 12

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания для самопроверки

- •Лабораторная работа 13 исследование основного элемента транзисторно-транзисторной логики

- •Краткие сведения из теории Общие сведения

- •Логика работы

- •Задания для самопроверки

- •Лабораторная работа 14 исследование основного элемента эмиттерно-связанной логики

- •Краткие сведения из теории Общие сведения

- •Логика работы

- •Задания для самопроверки

- •Лабораторная работа 15 исследование триггерных схем

- •Краткие сведения из теории

- •Асинхронные триггеры

- •Асинхронный т-триггер

- •Задания для самопроверки

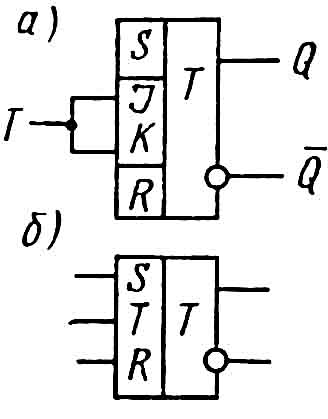

Асинхронный т-триггер

Т-триггер (триггер со счетным входом) – схема с двумя устойчивыми состояниями и одним входом Т, изменяющая свое состояние на противоположное всякий раз, кода на вход Т поступает управляющий (счетный) сигнал. Т-триггер строится на основе JK-триггера путем объединения входов J и K. На рис. 7.7, а показана логическая структура Т-триггера, а на рис. 7.7, б – его условное графическое обозначение. Логика работы Т-триггера определяется таблицей состояний (табл. 7.4).

Рис.

7.7.

Логическое уравнение работы Т-триггера записывается в виде

![]() (7.6)

(7.6)

и читается аналогично логическому уравнению работы JK-триггера. Уравнение (7.6) является уравнением сумматора по модулю 2, поэтому Т-триггер называется счетным триггером. На рис. 7.7, в приведена упрощенная временная диаграмма работы асинхронного Т-триггера, построенного на основе рассмотренного ранее двухступенчатого JK-триггера.

Асинхронный RST-триггер

R

Рис.

7.8.

Логическое уравнение работы RST-триггера записывается в виде

![]() ;

(7.7)

;

(7.7)

![]() (7.8)

(7.8)

Таблица 7.5

R

T

S

Q

0

0

0

0

1

0

0

0

1

1

1

0

0

0

RST-триггер сочетает в себе свойство RS- и Т-триггеров. Он аналогичен триггеру Т-типа и отличается от него только наличием двух установочных входов (R и S). Из табл. 7.5 следует, что если на счетном входе Т присутствуют сигналы 1, то триггер меняет свое состояние на противоположное, а из условия (7.8) – что наличие единичных входных сигналов одновременно на любых двух входах триггера запрещено, так как это вызывает его неопределенное состояние.

СИНХРОННЫЕ ТРИГГЕРЫ

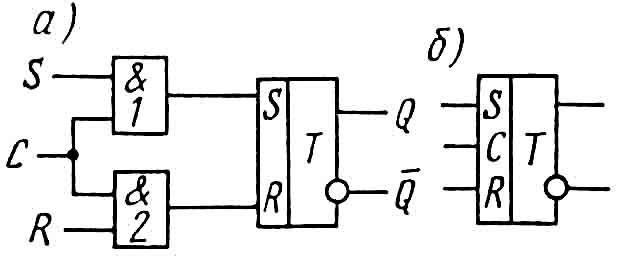

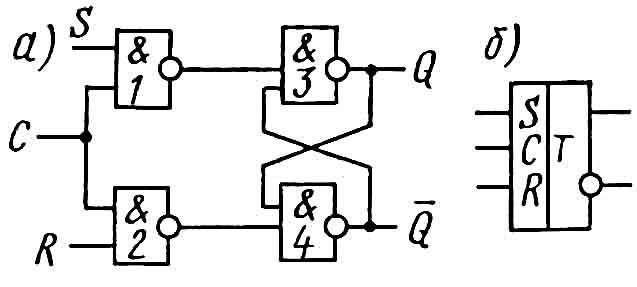

Синхронный RS-триггер со статическим управлением записью

На рис. 7.9, а приведена логическая схема, а на рис. 7.9, б – условное графическое обозначение синхронного RS-триггера. Особенностью RS-триггера является наличие двух конъюнкторов на входах. Синхронизирующий сигнал С в зависимости от разрешения по входам S или R проходит через конъюнкторы либо на вход R, либо на вход S, устанавливая триггер соответственно в состояние «0» или «1». Таким образом, информация, поступающая на информационные входы R и S, может быть передана на собственно триггер только при поступлении синхронизирующего сигнала С.

Закон функционирования синхронного RS-триггера представлен минимизированной таблицей состояний (табл. 7.6).

Рис. 7.9.

Логическое уравнение работы триггера записывается в виде

![]() ;

(7.9)

;

(7.9)

![]() .

(7.10)

.

(7.10)

Уравнение

(7.9) можно

прочитать следующим образом: «Единица

на выходе триггера будет тогда, когда

был сигнал установки единицы и сигнал

синхронизации

![]() или когда единица уже была на триггере

в предыдущий момент времени и не было

сигнала установки в нулевое состояние

в момент действия сигнала синхронизации

(

или когда единица уже была на триггере

в предыдущий момент времени и не было

сигнала установки в нулевое состояние

в момент действия сигнала синхронизации

(![]() )».

Условие

(7.10) определяет

запрет на одновременность наличия

сигналов на входах С,

R,

S,

так как в этом случае состояние триггера

будет неопределенным.

)».

Условие

(7.10) определяет

запрет на одновременность наличия

сигналов на входах С,

R,

S,

так как в этом случае состояние триггера

будет неопределенным.

На

рис. 7.10, а

приведена логическая схема, а на рис.

7.10, б

–

условное

графическое обозначение синхронного

RS-триггера

на элементах И–ИЛИ–НЕ, управляемого

положительными сигналами по входам С,

R,

S.

Если С=1,

S=1,

R=0,

то триггер переключается в устойчивое

состояние, при котором Q=1,

.

В этом случае открывается конъюнктор

![]() с выхода которого сигнал

с выхода которого сигнал

![]() проходит через дизъюнктор

проходит через дизъюнктор

![]() и после инверсии на выходе дизъюнктора

оказывается равным

.

и после инверсии на выходе дизъюнктора

оказывается равным

.

Рис.

7.11.

Затем

по цепи обратной связи он проходит через

конъюнктор

,

дизъюнктор

![]() и инвертор

и инвертор

![]() .

При этом на прямом выходе триггера

оказывается сигнал Q=1.

По окончании сигнала С,

т. е. при С=0,

устойчивое состояние триггера не

изменяется, так как конъюнктор

.

При этом на прямом выходе триггера

оказывается сигнал Q=1.

По окончании сигнала С,

т. е. при С=0,

устойчивое состояние триггера не

изменяется, так как конъюнктор

![]() будет открыт. Если С=1,

R=1,

S=0,

то триггер переключается в исходное

устойчивое состояние, когда Q=0,

.

будет открыт. Если С=1,

R=1,

S=0,

то триггер переключается в исходное

устойчивое состояние, когда Q=0,

.

На

рис. 7.11, а

показана логическая схема, а на рис.

7.11, б

–

условное

графическое обозначение синхронного

RS-триггера

на элементах И-НЕ, управляемого

положительными сигналами по входам С,

R,

S.

Если С=1,

S=1,

R=0,

то триггер переключается в устойчивое

состояние, при котором Q=1,

a

.

В этом случае сигнал. С=1

проходит через конъюнктор

инвертируется и переключает триггер,

т. е. Q=1.

Затем по цепи обратной связи открывается

конъюнктор

![]() и на выходе будет

.

Если С=1,

R=1,

S=0,

то триггер переключается в исходное

устойчивое состояние когда

,

.

и на выходе будет

.

Если С=1,

R=1,

S=0,

то триггер переключается в исходное

устойчивое состояние когда

,

.

На

рис. 7.12, а

показана логическая схема для исследования

синхронных

RS-триггеров

в динамическом режиме, а на рис.

7.12, б

–

временная

диаграмма, поясняющая ее работу (С

– сигналы синхронизации:

На

рис. 7.12, а

показана логическая схема для исследования

синхронных

RS-триггеров

в динамическом режиме, а на рис.

7.12, б

–

временная

диаграмма, поясняющая ее работу (С

– сигналы синхронизации:

![]() – сигналы синхронизации задержанные;

– сигналы синхронизации задержанные;

![]() – элемент задержки;

,

триггеры управления (в макете это

синхронные JK-триггеры));

Q,

–прямой и инверсный выходы триггеров;

S,

R

– установка

триггеров в состояния

«1» и «0»

соответственно. В данном макете

асинхронная установка триггеров

управления в состояние «0» осуществляется

подачей напряжения «земля» на вход

R.

При этом

на выходах триггеров Q=0,

a

.

Асинхронная установка триггеров в

состояние

«1»

осуществляется подачей напряжения +Е

зажима

«+» на вход

S.

– элемент задержки;

,

триггеры управления (в макете это

синхронные JK-триггеры));

Q,

–прямой и инверсный выходы триггеров;

S,

R

– установка

триггеров в состояния

«1» и «0»

соответственно. В данном макете

асинхронная установка триггеров

управления в состояние «0» осуществляется

подачей напряжения «земля» на вход

R.

При этом

на выходах триггеров Q=0,

a

.

Асинхронная установка триггеров в

состояние

«1»

осуществляется подачей напряжения +Е

зажима

«+» на вход

S.

Работа

исследуемого триггера в динамическом

режиме очевидна из временной диаграммы.

Сигналы на входы

S

и R

исследуемого синхронного триггера

подаются с выходов

![]() и

и

![]() первого триггера управления

.

первого триггера управления

.

Синхронный D-триггер

Синхронный D-триггер – схема с двумя устойчивыми положениями, с одним информационным входом D и входом синхронизации С, состояние которой в момент времени совпадает с кодом входного сигнала («1» или «0» на входе D, действующие в момент времени ).

На рис. 7.13, а приведена логическая схема синхронного D-триггера, а на рис. 7.13, б – его условное графическое обозначение. Логика работы синхронного D-триггера представлена таблицей состояния (табл. 7.7).

Логическое уравнение синхронного D-триггера записывается в виде

![]() .

(7.11)

.

(7.11)

Минимизированное логическое уравнение имеет вид

![]() .

(7.12)

.

(7.12)

Из табл. 7.7, а также из логических уравнений следует, что при С=1 в D-триггер всегда записывается и сохраняется та информация, которая была на входе D до прихода сигнала С.

Т

Таблица

7.

|

|

|

D |

C |

Q |

0 |

0 |

|

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

аким образом, состояние D-триггера на выходе в последующем интервале времени совпадает с входным сигналом в предыдущем интервале времени, т. е. с временем (имеет место «задержка» сигнала, поступающего на вход D). Поэтому синхронный D-триггер называется также триггером задержки. Рассмотрим логику работы D-триггера, приведенного на рис. 7.13, а. Если С=1 и D=1, то открывается конъюнктор и сигнал поступает на вход S триггера, переключая его в состояние «1», т. е. Q=1. Если С=1, a D=0, то открывается конъюнктор и сигнал поступает на вход R триггера, переключая его в состояние «0», т. е. Q=0.

На

рис. 7.13, в

приведена временная диаграмма,

поясняющая работу синхронного

D-триггера.

Из диаграммы следует, что в интервале

между синхронизирующими сигналами

триггер будет сохранять ту информацию,

которая присутствовала на входе

D

в момент окончания действия синхронизирующего

сигнала. В качестве синхронных

D-триггеров

можно использовать схемы синхронных

RS-триггеров,

заменив входы S

на входы

D,

а входы

R

– на

входы

![]() .

Такие

D-триггеры

называются синхронными

D-триггерами

с парафазными входами (требуется как

сигнал с входа

D,

так и его инверсия

).

.

Такие

D-триггеры

называются синхронными

D-триггерами

с парафазными входами (требуется как

сигнал с входа

D,

так и его инверсия

).

D-триггеры могут быть реализованы на элементах ИЛИ–НЕ, И–НЕ, И–ИЛИ–НЕ. На рис. 7.13, г приведена логическая схема D-триггера на элементах И–НЕ, управляемая положительными сигналами, поступающими на входы D, С. Если С=1 и D=1, то сигнал проходит через первый элемент, инвертируется и переключает триггер, устанавливая его в состояние Q=1. Если С=1, a D=0, то сигнал С=1 проходит через второй элемент, инвертируется и переключает триггер, устанавливая его в состояние =1, Q=0.

На рис. 7.13, д приведена схема синхронного D-триггера на элементах И–НЕ, И–ИЛИ–НЕ (триггера-защелки). Триггер переключается синхронизирующими сигналами отрицательной полярности.

Если

D=1

и приходит первый отрицательный

синхронизирующий сигнал

Если

D=1

и приходит первый отрицательный

синхронизирующий сигнал

![]() ,

то после его инвертирования на вход

конъюнктора

поступают сигналы С=1

и D=1.

Триггер при этом переключается,

устанавливаясь в состояние Q=1,

.

В промежутках между сигналами, когда

,

то после его инвертирования на вход

конъюнктора

поступают сигналы С=1

и D=1.

Триггер при этом переключается,

устанавливаясь в состояние Q=1,

.

В промежутках между сигналами, когда

![]() ,

состояние триггера устойчивое и не

изменяется, так как на входах

конъюнктора

действуют сигналы

,

состояние триггера устойчивое и не

изменяется, так как на входах

конъюнктора

действуют сигналы

![]() и

,

поэтому

,

а

.

Если

,

т. е. С=1,

a

D=0,

то

,

a

.

и

,

поэтому

,

а

.

Если

,

т. е. С=1,

a

D=0,

то

,

a

.

Находят

также применение однофазные

D-триггеры.

Особенностью их является наличие

одного информационного выхода Q.

Существуют две разновидности таких

триггеров: прямой и инверсный (с прямой

записью информации и с инверсной). Работа

прямого D-трпггера

соответствует табл.

7.7 и

логическому уравнению

(7.12). На рис.

7.13, е

приведена логическая схема инверсного

![]() -триггера

на элементах

НЕ, И–ИЛИ–НЕ. Логика работы инверсного

-триггера

заключается в следующем: если Q=1,

(отсутствуют синхронизирующие

сигналы), то с выхода конъюнктора

снимается сигнал «0» и

Q=1.

Тем самым подтверждается состояние

Q=1

на выходе триггера. Если D=1

и

(присутствует синхронизирующий сигнал),

то с выхода конъюнктора

снимается сигнал

«1» и

Q=0.

После

окончания синхронизирующего сигнала,

когда

и D=1,

с выхода конъюнктора

снимается сигнал

«1» и

.

Таким образом, состояние «0» на выходе

подтверждается. Если

D=0

и

(присутствует синхронизирующий сигнал),

то с выходов конъюнкторов

и

снимается сигнал «0» и

Q=1.

После окончания синхронизирующего

сигнала, когда

и D=0,

состояние триггера не изменяется, т. е.

Q=1.

-триггера

на элементах

НЕ, И–ИЛИ–НЕ. Логика работы инверсного

-триггера

заключается в следующем: если Q=1,

(отсутствуют синхронизирующие

сигналы), то с выхода конъюнктора

снимается сигнал «0» и

Q=1.

Тем самым подтверждается состояние

Q=1

на выходе триггера. Если D=1

и

(присутствует синхронизирующий сигнал),

то с выхода конъюнктора

снимается сигнал

«1» и

Q=0.

После

окончания синхронизирующего сигнала,

когда

и D=1,

с выхода конъюнктора

снимается сигнал

«1» и

.

Таким образом, состояние «0» на выходе

подтверждается. Если

D=0

и

(присутствует синхронизирующий сигнал),

то с выходов конъюнкторов

и

снимается сигнал «0» и

Q=1.

После окончания синхронизирующего

сигнала, когда

и D=0,

состояние триггера не изменяется, т. е.

Q=1.

Синхронный D-триггер на основе трех триггеров

На

рис.

7.13, ж

приведена логическая схема синхронного

D-триггера

на основе трех триггеров, на рис. 7.13, з

– его условное

графическое обозначение, на рис.

7.13, и

– временная

диаграмма работы. D-триггер

выполнен на шести элементах

![]() .

Элементы

,

образуют основной триггер. Элементы

.

Элементы

,

образуют основной триггер. Элементы

![]() – верхний и нижний коммутирующие

триггеры. В исходном состоянии D-триггер

находится в состоянии «0», т. е. Q=0,

,

– верхний и нижний коммутирующие

триггеры. В исходном состоянии D-триггер

находится в состоянии «0», т. е. Q=0,

,

![]() ,

,![]() .

Принимаем С=0,

D=0.

При этом

.

Принимаем С=0,

D=0.

При этом

![]() ,

,

![]() ,

,

![]() ,

,![]() .

.

Если

![]() ,

то

,

то

![]() ,

,

,

,

![]() .

Поступающий первый синхронизирующий

сигнал С=1

проходит через элемент

и переключает основной триггер в

состояние

1 (отрицательный

перепад с выхода в

действует на элемент

).

При этом

,

a

.

Второй синхронизирующий сигнал С=1

подтверждает состояние

«1» триггера.

.

Поступающий первый синхронизирующий

сигнал С=1

проходит через элемент

и переключает основной триггер в

состояние

1 (отрицательный

перепад с выхода в

действует на элемент

).

При этом

,

a

.

Второй синхронизирующий сигнал С=1

подтверждает состояние

«1» триггера.

Если D=0, то , , , (так как С=0). Третий синхронизирующий сигнал С=1 проходит через элемент и переключает основной триггер в состояние «0» (отрицательный перепад с выхода б действует на элемент ). При этом , a . Четвертый синхронизирующий сигнал подтверждает состояние «0» триггера. Начиная с пятого синхронизирующего сигнала триггер снова переключается в состояние «1». Рассматриваемый триггер может работать как RS-триггер в асинхронном режиме (управление по входам и ). Для организации счетного режима (D-триггер преобразуется в Т-триггер) инверсный выход необходимо присоединить к входу D (показано пунктиром). В этом случае триггер изменяет свое состояние всякий раз на противоположное при поступлении на вход С очередного синхронизирующего сигнала.

Исследование D-триггера в динамическом режиме. На рис. 7.13, к приведена логическая схема для исследования синхронных D-триггеров в динамическом режиме, а на рис. 7.13, л – временная диаграмма, поясняющая работу этой схемы.

Первоначально

триггеры схемы устанавливаются в

состояние «0» сигналом «Сброс».

При этом индикаторы

![]() не горят. Считаем, что управление

D-триггером

осуществляется от управляющего триггера

.

Тогда выход

не горят. Считаем, что управление

D-триггером

осуществляется от управляющего триггера

.

Тогда выход

![]() триггера

подключен на вход

D-триггера D.

Задержанный синхронизирующий сигнал

триггера

подключен на вход

D-триггера D.

Задержанный синхронизирующий сигнал

![]() подключаем на вход С

D-триггера.

Когда D=0,

то первый синхронизирующий сигнал

серии

проходит через элемент

(на втором входе элемента

–разрешение)

и подтверждает состояние «0» D-триггера.

Когда D=1

(на временной диаграмме триггер

в состоянии

«1», т.е.

подключаем на вход С

D-триггера.

Когда D=0,

то первый синхронизирующий сигнал

серии

проходит через элемент

(на втором входе элемента

–разрешение)

и подтверждает состояние «0» D-триггера.

Когда D=1

(на временной диаграмме триггер

в состоянии

«1», т.е.

![]() ),

второй синхронизирующий сигнал серии

проходит через элемент

и переключает

D-триггер

в состояние

«1», т. е.

.

Третий синхронизирующий сигнал серии

подтверждает состояние

«1» D-триггера.

Далее работа схемы очевидна по временной

диаграмме.

),

второй синхронизирующий сигнал серии

проходит через элемент

и переключает

D-триггер

в состояние

«1», т. е.

.

Третий синхронизирующий сигнал серии

подтверждает состояние

«1» D-триггера.

Далее работа схемы очевидна по временной

диаграмме.

Синхронный JK-триггер

Синхронный JK-триггер – схема с двумя устойчивыми состояниями, имеющая информационные входы J и К и вход синхронизации С, которая при одновременном поступлении сигналов на входы С, J, К осуществляет инверсию предыдущего состояния.

Н

Таблица

7.

|

|

||

С |

J |

S |

Q |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

|

а рис. 7.13, м (приведена логическая схема синхронного JK-триг-гера, а на рис. 7.13, н – его условное графическое обозначение. Логика работы синхронного JK-триггера представлена минимизированной таблицей состояний (табл. 7.8).

Логическое уравнение синхронного JK-триггера, составленное на основании табл. 7.8, записывается в виде

![]() (7.13)

(7.13)

Принцип работы синхронного JK-триггера аналогичен принципу работы асинхронного JK-триггера. С учетом предыдущего состояния триггера, т.е. Q=0 или Q=1, при поступлении синхронизирующего сигнала С и при наличии сигналов или K = 1 триггер через соответствующий конъюнктор устанавливается в состояние «1», если J=1, или в состояние «0», если К=1. Независимо от предыдущего состояния при одновременной подаче на входы сигналов С=J=K=1 триггер через одну из схем конъюнктора всегда переключается в противоположное состояние.

JK-триггер

может быть реализован на элементах

ИЛИ–НЕ, И–НЕ, И–ИЛИ–НЕ. На рис.

7.13, о

приведена логическая схема синхронного

двухступенчатого

JK-триггера

на элементах

И–НЕ с

запрещающими связями, на рис.

7.13, п

показано условное графическое

обозначение

JK-триггера,

а на рис.

7.13, р

– временная

диаграмма, поясняющая его работу.

Указанный триггер состоит из восьми

элементов. Элементы

,

образуют первый триггер для временного

хранения входной информации; элементы

,

– второй триггер, определяющий состояние

триггера в целом; элементы

,

являются ключами первого триггера,

а элементы

,

– ключами второго триггера. Особенность

схемы

JK-триггера –

запрещающие связи

и

,

входы

,

,

,

(внутренние асинхронные входы триггера);

обратные связи (с выходов

Q

и

на входы элементов

,

).

Принимаем, что в исходном состоянии

Q=0;

;

![]() ;

;

![]() .

Если J=1,

а К=0,

то синхронизирующий сигнал С=1

проходит через элемент

.

Если J=1,

а К=0,

то синхронизирующий сигнал С=1

проходит через элемент

![]() ,

инвертируется и устанавливает первый

триггер в состояние

.

Одновременно он запрещает посредством

,

на входах элементов

,

передачу информации на второй триггер

с первого. После окончания действия

синхронизирующего сигнала, т. е. когда

С=0,

на выходах элементов

,

появятся сигналы

«1»,

разрешающие проходить информации с

первого триггера. При этом сигнал

проходит через элемент

,

инвертируется и переключает второй

триггер, устанавливая его в состояние

Q=1.

Таким образом, сигнал J=1

при поступлении синхронизирующего

сигнала

,

инвертируется и устанавливает первый

триггер в состояние

.

Одновременно он запрещает посредством

,

на входах элементов

,

передачу информации на второй триггер

с первого. После окончания действия

синхронизирующего сигнала, т. е. когда

С=0,

на выходах элементов

,

появятся сигналы

«1»,

разрешающие проходить информации с

первого триггера. При этом сигнал

проходит через элемент

,

инвертируется и переключает второй

триггер, устанавливая его в состояние

Q=1.

Таким образом, сигнал J=1

при поступлении синхронизирующего

сигнала

![]() записывается

сначала в первый триггер, т. е.

,

а затем по заднему фронту сигнала С

переписывается во второй триггер

(рис.

7.13, р).

Если теперь

,

,

а

записывается

сначала в первый триггер, т. е.

,

а затем по заднему фронту сигнала С

переписывается во второй триггер

(рис.

7.13, р).

Если теперь

,

,

а

![]() ,

то, рассуждая аналогично, можно убедиться

в том, что сначала первый, а затем

второй триггеры переключатся в исходное

состояние, т. е.

,

Q=0.

В том случае, если сигналы на вход

триггера поступают одновременно, т.

е.

,

то, рассуждая аналогично, можно убедиться

в том, что сначала первый, а затем

второй триггеры переключатся в исходное

состояние, т. е.

,

Q=0.

В том случае, если сигналы на вход

триггера поступают одновременно, т.

е.

![]() ,

то сигнал

проходит либо через элемент

,

либо через элемент

(это зависит от сигнала обратной связи

с выхода триггера), переключая всегда

второй триггер в состояние, противоположное

предыдущему. Временная диаграмма,

показанная на рис. 7.13, р,

подтверждает логику работы синхронною

JK-трнггера. Направление стрелок на

диаграмме

показывает последовательность прохождения

сигналов в схеме и воздействия их на

соответствующие элементы.

,

то сигнал

проходит либо через элемент

,

либо через элемент

(это зависит от сигнала обратной связи

с выхода триггера), переключая всегда

второй триггер в состояние, противоположное

предыдущему. Временная диаграмма,

показанная на рис. 7.13, р,

подтверждает логику работы синхронною

JK-трнггера. Направление стрелок на

диаграмме

показывает последовательность прохождения

сигналов в схеме и воздействия их на

соответствующие элементы.

Исследование работоспособности синхронного JK-триггера в динамическом режиме осуществляется аналогично исследованию работоспособности синхронного RS-триггера. Для этого необходимо использовать логическую схему и временную диаграмму, приведенные на рис. 7.12, а, б.

Синхронный двухступенчатый триггер

Синхронный двухступенчатый триггер – триггер с двухступенчатым запоминанием информации; как правило, он выполняется на основе тактируемых триггеров по способу М–S. В соответствии с этим способом триггер выполняется на двух триггерах М (Master – основной) и S (Slave –вспомогательный). М-триггер принимает входную информацию, а S-триггер фиксирует состояние триггера в целом. При этом оба триггера могут быть либо однотипными, например RS- или D-триггеры, либо различными.

Управляющая связь между М-триггером и S-триггером осуществляется двумя синхросериями, посредством запрещающего инвертора, разнополярным управлением, запрещающими связями.

Рассмотрим некоторые двухступенчатые триггеры.

Двухступенчатый

RS-трштер с

двумя синхросериями. На рис. 7.14,

а

показана логическая схема двухступенчатого

RS-триггера, а

на рис.

7.14, б

– его

условное графическое обозначение.

Сигналы серии

![]() сдвинуты относительно сигналов серии

сдвинуты относительно сигналов серии

![]() на половину периода. Если

на половину периода. Если

![]() ,

a

,

a

![]() ,

то первый сигнал серии

,

то первый сигнал серии

![]() проходит через конъюнктор

на вход

S,

М-триггера, переключая его в состояние

«1», т. е.

Затем при подаче первого сигнала серии

проходит через конъюнктор

на вход

S,

М-триггера, переключая его в состояние

«1», т. е.

Затем при подаче первого сигнала серии

![]() открывается

конъюнктор

и информация с М-триггера (

)

переписывается в

S-триггер.

Если

открывается

конъюнктор

и информация с М-триггера (

)

переписывается в

S-триггер.

Если

![]() ,

,

![]() ,

то, рассуждая аналогично, можно

проследить, что первый, а затем второй

триггеры установятся в состояние

«0», т. е.

;

.

,

то, рассуждая аналогично, можно

проследить, что первый, а затем второй

триггеры установятся в состояние

«0», т. е.

;

.

На рис. 7.14, в приведена логическая схема двухступенчатого RS-триггера на элементах И–НЕ, управляемая двумя синхросериями положительной полярности. Принцип работы указанной схемы аналогичен принципу работы схемы, рассмотренной выше.

На

рис. 7.14, г

приведена логическая схема двухступенчатого

Т-триггера с управлением между

ступенями посредством запрещающего

инвертора, а на рис. 7.14,

д – его

условное графическое обозначение.

Указанная схема может быть реализована

на элементах И – НЕ, ИЛИ – НЕ, И – ИЛИ –

НЕ. Особенность схемы состоит в том, что

между М- и

S-триггерами

включается инвертор, обеспечивающий

однотактный режим и осуществляющий

блокировку перезаписи информации в

S-триггер

во время записи информации в М-триггер.

Роль информационных сигналов по входам

R

и S

S-триггера выполняют

сигналы с выходов

![]() и

и

![]() М-триггера. Роль информационных

сигналов по входам

R

и

S М-триггера

выполняют сигналы обратной связи с

выходов

Q

и

S-триггера.

При этом каждый счетный сигнал обеспечивает

перевод М-триггера в состояние,

противоположное состоянию

S-триггера,

а после окончания действия синхронизирующего

сигнала

S-триггер

принимает состояние М-триггера.

Практически реализация такого триггера

на элементах И–НЕ сводится к включению

между шинами

и

элемента И–НЕ и подаче только

синхронизирующих сигналов серии

.

М-триггера. Роль информационных

сигналов по входам

R

и

S М-триггера

выполняют сигналы обратной связи с

выходов

Q

и

S-триггера.

При этом каждый счетный сигнал обеспечивает

перевод М-триггера в состояние,

противоположное состоянию

S-триггера,

а после окончания действия синхронизирующего

сигнала

S-триггер

принимает состояние М-триггера.

Практически реализация такого триггера

на элементах И–НЕ сводится к включению

между шинами

и

элемента И–НЕ и подаче только

синхронизирующих сигналов серии

.

Определим

параметры, характеризующие быстродействие

двухступенчатого Т-триггера. Так как

указанный триггер выполнен на основе

синхронных

RS-триггеров,

то, следовательно, длительность сигналов

синхронизации

![]() .

Минимально допустимый период поступления

счетных сигналов должен быть не меньше

суммарной средней задержки распространения

сигнала основного и вспомогательного

триггеров, т. е.

.

Минимально допустимый период поступления

счетных сигналов должен быть не меньше

суммарной средней задержки распространения

сигнала основного и вспомогательного

триггеров, т. е.

![]() .

Так как средняя задержка распространения

RS-триггера

равна

.

Так как средняя задержка распространения

RS-триггера

равна

![]() ,

то

,

то

![]() ,

где

,

где

![]() –максимальная частота сигналов,

поступающих на вход С.

–максимальная частота сигналов,

поступающих на вход С.

На

рис.

7.14, е

приведена логическая схема синхронного

двухступенчатого

D-триггера

с разнополярным управлением между

ступенями, а на рис. 7.14,

ж

– его

условное графическое обозначение.

Двухступенчатый триггер выполнен на

разнотипных триггерах. Основной

триггер

– D-триггер,

вспомогательный

– RS-триггер.

Кроме того, основной триггер

– с прямым

управлением, вспомогательный

– с инверсным

управлением. Блокировка перезаписи

информации из основного триггера в

вспомогательный обеспечивается наличием

инверсии на входе С

вспомогательного триггера. После

окончания синхронизирующего сигнала

на входе С

информация с основного триггера

переписывается в вспомогательный

триггер. Реализация данного триггера

возможна на элементах И–НЕ, ИЛИ–НЕ,

И–ИЛИ–НЕ. Схема синхронного

двухступенчатого

JK-триггера

с запрещающими связями была рассмотрена

ранее. Логическая схема такого триггера

приведена на рис.

7.13, о,

а его условное графическое обозначение

– на рис.

7.13, п.

Следует также добавить, что двухступенчатый

JK-триггер

относится к универсальным триггерам,

позволяющим реализовать триггеры других

типов. На рис.

7.15 приведены

примеры, подтверждающие сказанное

[здесь а –

TV-триггер

и Т-триггер

(при

![]() );

б – D-триггер;

в –

DV-триггер;

г

– RS-триггер].

);

б – D-триггер;

в –

DV-триггер;

г

– RS-триггер].

Таким образом, рассмотрены все основные схемы синхронных триггеров с двухступенчатым запоминанием информации и все виды управляющих связей между ступенями.

АДАНИЯ И ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Асинхронные триггеры

Задание 1. Исследовать логику работы асинхронного RS-триггера с инверсными входами на элементах И–НЕ (см. рис. 7.4, а–г). Порядок выполнения задания следующий:

1) собрать схему триггера на элементах И–НЕ;

2) подключить индикатор состояния на выход Q;

3) подать на входы S и R напряжение с тумблерного регистра;

4) исследовать логику работы триггера согласно табл. 7.2, задавая значения «1» и «0» тумблерного регистра («1»= =3,6 В; «0»= =0,3 В).

Синхронные триггеры

Задание 2. Исследовать логику работы синхронного RS-триггера с прямыми входами на элементах И–ИЛИ–НЕ в статистическом режиме (см. рис. 7.9 и 7.10). Порядок выполнения задания следующий:

1) собрать схему RS-триггера на элементах И–ИЛИ–НЕ согласно рис. 7.10, а;

2) подключить индикатор состояния на выход Q;

3) установить триггер в состояние «0»;

4) подать на входы С, S, R напряжение = 0,3 В с тумблерного регистра;

5) исследовать логику работы триггера согласно табл. 7.6, задавая значения «1» и «0» с тумблерного регистра («l»= =3,6В, «0» = = 0,3В).