- •Краткие правила по технике безопасности при проведении лабораторных работ в лаборатории.

- •Правила проведения занятий в лаборатории. Подготовка к работе.

- •Подготовка к лаборатории

- •Оформление отчёта:

- •Описание лабораторной установки.

- •Порядок подготовки к работе и включения стенда.

- •Система моделирования Electronics Workbench

- •Структура окна и система меню

- •Меню File

- •Меню Edit

- •Меню Circuit

- •Меню Analysis

- •Меню Window

- •Меню Help

- •Создание схем

- •Технология подготовки схем

- •Группа Favorites

- •Группа Sources

- •Группа Basic

- •Группа Diodes

- •Группа Transistors

- •Мультиметр

- •Функциональный генератор

- •Осциллограф

- •Измеритель ачх и фчх

- •Лабораторная работа №1.

- •Результаты измерений, проведенных на осциллографах с1-55, 6502

- •Органы управления и регулировки.

- •Осциллограф 2-х лучевой с1-55

- •Органы управления и регулировки. Передняя панель.

- •Осциллограф 2-х лучевой (Electronics Workbench)

- •Органы управления и регулировки.

- •Проведение измерений с помощью осциллографа.

- •1) Измерение постоянного напряжения.

- •2) Измерение синусоидального сигнала.

- •3) Измерение временных интервалов и амплитуды с помощью калибратора.

- •4) Измерение угла сдвига фаз.

- •5) Измерение длительности импульсов.

- •6) Режимы развертки.

- •7) Непрерывная развертка с синхронизацией исследуемым сигналом.

- •8) Синхронизация от внешнего источника.

- •9) Внешняя модуляции луча но яркости.

- •Структурная схема осциллографа

- •Выполнение работы.

- •Лабораторная работа № 2. Исследование полупроводникового диода.

- •Часть I.

- •Пример расчета

- •Пояснения к работе

- •Условно графические обозначения п/п диодов.

- •Лабораторная работа № 3 Исследование неуправляемых выпрямительных устройств

- •Контрольные вопросы:

- •Лабораторная работа №4 Изучение свойств усилителя при различных способах включения транзистора.

- •Лабораторная работа №5 Исследование усилительного каскада на биполярном транзисторе, включённом по схеме с общим эмиттером (оэ) в режиме класса а.

- •Входные и выходные характеристики транзисторов:

- •Лабораторная работа №6.

- •Лабораторная работа №7.

- •Лабораторная работа №8.

- •Лабораторная работа 9 исследование конъюнктура диодной логики

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания для самопроверки

- •Лабораторная работа 10 исследование дизъюнктора диодной логики

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания и порядок выполнения работы

- •Задания для самопроверки

- •Лабораторная работа 11

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Особенности принципиальной схемы

- •Задания и порядок выполнения работы

- •Задания для самопроверки

- •Лабораторная работа 12

- •Краткие сведения из теории Логика работы

- •Особенности принципиальной схемы

- •Задания для самопроверки

- •Лабораторная работа 13 исследование основного элемента транзисторно-транзисторной логики

- •Краткие сведения из теории Общие сведения

- •Логика работы

- •Задания для самопроверки

- •Лабораторная работа 14 исследование основного элемента эмиттерно-связанной логики

- •Краткие сведения из теории Общие сведения

- •Логика работы

- •Задания для самопроверки

- •Лабораторная работа 15 исследование триггерных схем

- •Краткие сведения из теории

- •Асинхронные триггеры

- •Асинхронный т-триггер

- •Задания для самопроверки

Асинхронные триггеры

Асинхронный RS-триггер на элементах ИЛИ—НЕ с прямыми входами со статическим управлением записью

Этот триггер изменяет свое состояние под воздействием прямых значений входных сигналов (положительных) и называется RS-триггером с прямыми входами. На рис. 7.3, а приведена логическая структура триггера, а на рис. 7.3, б – его условное обозначение.

RS-триггер – схема с двумя устойчивыми состояниями, имеющая два информационных входа: S и R. При S=1 и R=0 триггер устанавливается в состояние «1», т. е. Q=1, при R=1 и S=0 триггер устанавливается в состояние «0», т. е. Q=0.

Логика

работы

RS-триггера

(закон функционирования) представляется

таблицей

состояний

или истинности

(табл.

7.1). Здесь

![]() и

и

![]() – последовательные моменты времени;

момент времени

наступает

тогда, когда сигналы на выходе триггера

под воздействием входных сигналов

принимают значения, соответствующие

последующему состоянию;

– последовательные моменты времени;

момент времени

наступает

тогда, когда сигналы на выходе триггера

под воздействием входных сигналов

принимают значения, соответствующие

последующему состоянию;

![]() – хранение состояния триггера; н/о

– состояние триггера неопределенно

(это состояние триггера характеризуется

тем, что в процессе действия входных

сигналов, равных

«1», выходные

сигналы оказываются одинаковыми, т.

е.

– хранение состояния триггера; н/о

– состояние триггера неопределенно

(это состояние триггера характеризуется

тем, что в процессе действия входных

сигналов, равных

«1», выходные

сигналы оказываются одинаковыми, т.

е.

![]() или

или

![]() ,

а после окончания действия входных

сигналов триггер может оказаться в

состоянии Q=1

или Q=0

с равной вероятностью, поэтому комбинация

входных сигналов RS=1

должна быть исключена).

,

а после окончания действия входных

сигналов триггер может оказаться в

состоянии Q=1

или Q=0

с равной вероятностью, поэтому комбинация

входных сигналов RS=1

должна быть исключена).

Логическое

уравнение работы

RS-триггера

по табл.

7.1 записывается

в виде

Логическое

уравнение работы

RS-триггера

по табл.

7.1 записывается

в виде

![]() ;

(7.1)

;

(7.1)

![]() (7.2)

(7.2)

и

характеризует состояние входов и выхода

триггера в момент времени

![]() (до его срабатывания) и в момент времени

(после его срабатывания). Уравнение

(7.1) можно

прочитать так: «Единица на выходе

триггера будет в том случае, если был

сигнал установки

«1» (первое

слагаемое, т. е.

S=1)

или если триггер находился в состоянии

«1» в

предыдущий момент времени, т. е.

(до его срабатывания) и в момент времени

(после его срабатывания). Уравнение

(7.1) можно

прочитать так: «Единица на выходе

триггера будет в том случае, если был

сигнал установки

«1» (первое

слагаемое, т. е.

S=1)

или если триггер находился в состоянии

«1» в

предыдущий момент времени, т. е.

![]() ,

и отсутствовал сигнал установки триггера

в состоянии «0», т. е. R=0

(второе слагаемое

,

и отсутствовал сигнал установки триггера

в состоянии «0», т. е. R=0

(второе слагаемое

![]() )».

Выражение

(7.2) определяет

обязательное условие работоспособности

триггера: «Одновременное поступление

сигналов «1»

на входы запрещено». В уравнении

(7.1) знак

«+»

соответствует дизъюнкции, т. е. логическому

сложению, а знак

«•» конъюнкции,

т. е. логическому умножению.

)».

Выражение

(7.2) определяет

обязательное условие работоспособности

триггера: «Одновременное поступление

сигналов «1»

на входы запрещено». В уравнении

(7.1) знак

«+»

соответствует дизъюнкции, т. е. логическому

сложению, а знак

«•» конъюнкции,

т. е. логическому умножению.

Н

Таблица 7.1

R

S

Q

0

0

0

1

1

1

0

0

1

1

н/о

![]()

![]()

![]() ).

Считаем, что все задержки одинаковые.

).

Считаем, что все задержки одинаковые.

RS-триггер

реализован на двух элементах ИЛИ–НЕ.

Схема, показанная на рис.

7.3, в,

соответствует логической структуре

изображенной на рис.

7.3, а.

Принимаем, что в начальном состоянии

транзистор

![]() закрыт, а транзистор

открыт. Тогда транзистор

открыт, а транзистор

закрыт, а транзистор

открыт. Тогда транзистор

открыт, а транзистор

![]() закрыт. Считаем, что «0» соответствует

напряжению

закрыт. Считаем, что «0» соответствует

напряжению

![]() ,

а

«1» – напряжению

(

,

а

«1» – напряжению

(![]() .

Указанное состояние

– устойчивое.

В соответствии с временной диаграммой

работы сигнал S

в виде перепада от

к

поступает на вход

S

и с некоторой задержкой

отпирает транзистор

который переключается (

соответствует времени перехода триггера

из состояния

«1» в

состояние «0»). При этом на выходе

будет напряжение

.

Сигнал с выхода

в виде

отрицательного перепада от

к

поступает на вход

1,

затем отпирает транзистор

,

который переключается с некоторой

задержкой

(

соответствует времени перехода

триггера из состояния «0» в

«1», т. е.

времени

.

Указанное состояние

– устойчивое.

В соответствии с временной диаграммой

работы сигнал S

в виде перепада от

к

поступает на вход

S

и с некоторой задержкой

отпирает транзистор

который переключается (

соответствует времени перехода триггера

из состояния

«1» в

состояние «0»). При этом на выходе

будет напряжение

.

Сигнал с выхода

в виде

отрицательного перепада от

к

поступает на вход

1,

затем отпирает транзистор

,

который переключается с некоторой

задержкой

(

соответствует времени перехода

триггера из состояния «0» в

«1», т. е.

времени

![]() ).

При этом на выходе

Q

будет напряжение

.

Указанное состояние триггера –

устойчивое.

Далее, рассуждая аналогично, видим, что

в соответствии с временной диаграммой

работы в какой-то момент времени сигнал

R

в виде положительного перепада поступает

на вход R

и с некоторой задержкой

отпирает транзистор

,

который переключается. При этом на

выходе

Q

будет

напряжение

.

Сигнал с выхода

Q

в виде отрицательного перепада поступает

на вход

3,

запирает транзистор

,

который переключается с некоторой

задержкой

.

При этом на выходе

будет напряжение

.

).

При этом на выходе

Q

будет напряжение

.

Указанное состояние триггера –

устойчивое.

Далее, рассуждая аналогично, видим, что

в соответствии с временной диаграммой

работы в какой-то момент времени сигнал

R

в виде положительного перепада поступает

на вход R

и с некоторой задержкой

отпирает транзистор

,

который переключается. При этом на

выходе

Q

будет

напряжение

.

Сигнал с выхода

Q

в виде отрицательного перепада поступает

на вход

3,

запирает транзистор

,

который переключается с некоторой

задержкой

.

При этом на выходе

будет напряжение

.

И

Рис.

7.4.

![]() и

и![]() ,

когда на обоих выходах триггера

,

когда на обоих выходах триггера

![]() )

– явление «риск»;

4) существуют

определенные требования к длительности

сигналов по входам S

и R.

Из временной диаграммы (рис.

7.3, г)

следует, что

)

– явление «риск»;

4) существуют

определенные требования к длительности

сигналов по входам S

и R.

Из временной диаграммы (рис.

7.3, г)

следует, что

![]() .

Иногда на практике для надежного

переключения триггера длительность

входного сигнала увеличивают на величину

,

т. е.

.

Иногда на практике для надежного

переключения триггера длительность

входного сигнала увеличивают на величину

,

т. е.

![]() ;

5)

максимальная частота и рабочая частота

переключения триггера соответственно

равны

;

5)

максимальная частота и рабочая частота

переключения триггера соответственно

равны

![]() ;

;

![]() ;

6) ряд основных параметров

триггера определяются параметрами

логических элементов, на которых

реализован триггер.

;

6) ряд основных параметров

триггера определяются параметрами

логических элементов, на которых

реализован триггер.

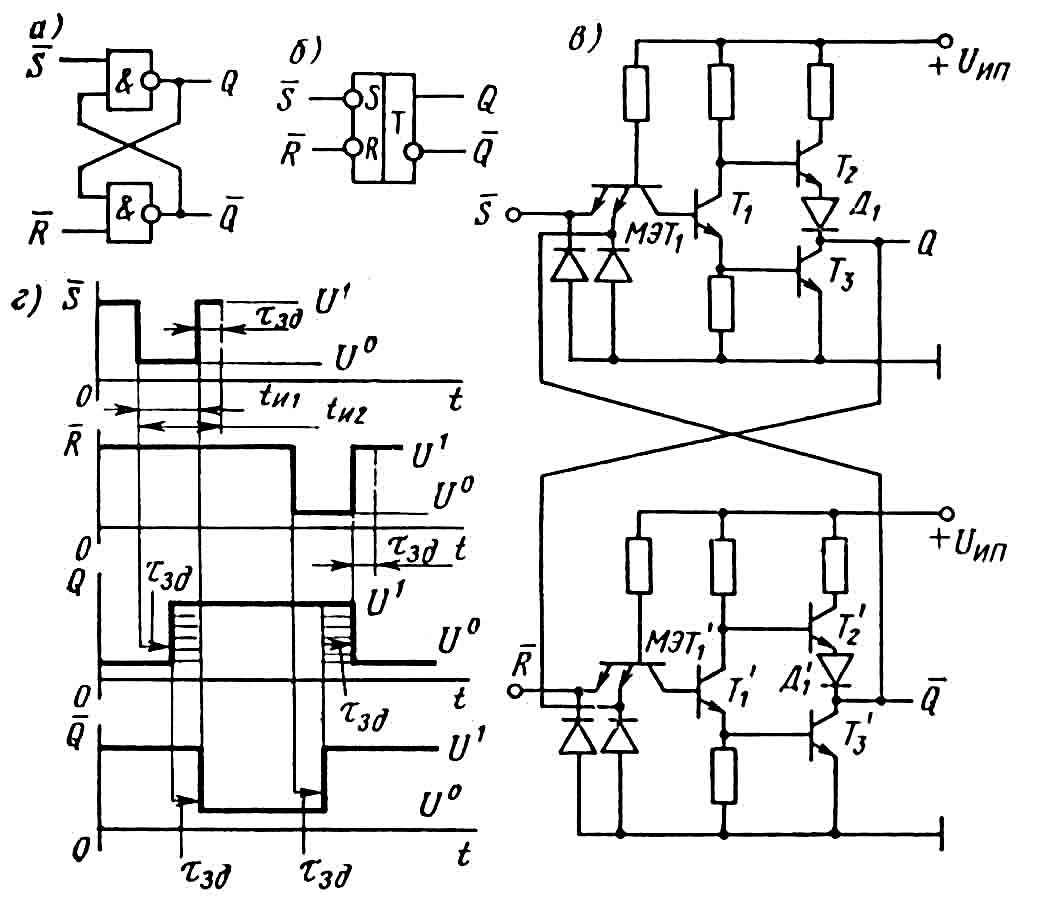

Асинхронный RS-триггер на элементах И – НЕ

с инверсными входами

На рис. 7.4, а приведена логическая структура RS-триггера, а на рис. 7.4, б – его условное графическое изображение. Такой триггер переключается (изменяет свое состояние на выходе) при воздействии на его входы инверсных входных сигналов (здесь инверсия рассматривается по отношению к положительным входным сигналам применительно к триггеру на элементах ИЛИ – НЕ). Следует заметить, что в данном триггере положения входов R и S взаимно противоположны соответствующим входам R и S триггера на элементах ИЛИ – НЕ (см. рис. 7.3, а и 7.4, а). Эта особенность учитывается как на логических, так и на принципиальных электрических схемах триггера, но не учитывается при условном обозначении (см. рис. 7.3, б и 7.4, б). Логика работы данного триггера представлена таблицей состояний или истинности (табл. 7.2).

Логическое уравнение триггера на элементах И–НЕ, составленное по табл. 7.2, записывается в виде

![]() ;

(7.3)

;

(7.3)

![]() .

(7.4)

.

(7.4)

Уравнение

(7.3) можно

прочитать следующим образом: «Единица

на выходе триггера будет в том случае,

если на выходе S

был сигнал «установка единицы» (первое

слагаемое) или если единица была уже в

предыдущий момент времени и отсутствовал

сигнал «установка триггера в нулевое

состояние», т. е.

![]() ».

».

Уравнение

(7.4) определяет

обязательное условие работоспособности

триггера: «Одновременное присутствие

сигналов переключения на входах

![]() и

и

![]() запрещено».

запрещено».

Т

Таблица

7.2

Q

0

1

1

1

0

0

1

1

0

0

н/о

На

рис.

7.4, в

приведена принципиальная схема триггера

на элементах И–НЕ

серии

155, а на рис.

7.4, г

– временная

диаграмма переключения триггера,

поясняющая его работу. Считаем, что все

задержки переключения одинаковые, т.

е.

![]() .

.

Пусть

RS-триггер

реализован на двух элементах И–НЕ.

Схема на рис.

7.4, в

соответствует логической структуре,

показанной на рис.

7.4, а.

Принимаем, что в начальном состоянии

верхний элемент включен, т. е. транзистор

открыт, а нижний элемент выключен,

т. е. транзистор

.

закрыт (на входах

и

напряжение

).

При этом на выходе Q

будет напряжение

,

а на выходе

– напряжение

![]() .

Указанное состояние –устойчивое. В

соответствии с временной диаграммой

работы триггера (рис.

7.4, г)

сигнал в виде отрицательного перепада

от

и

поступает

на вход

и с некоторой задержкой

переключает верхний элемент. При этом

.

Указанное состояние –устойчивое. В

соответствии с временной диаграммой

работы триггера (рис.

7.4, г)

сигнал в виде отрицательного перепада

от

и

поступает

на вход

и с некоторой задержкой

переключает верхний элемент. При этом

![]() открывается,

,

закрываются

и на выходе

Q

оказывается напряжение

.

Транзистор

и диод

при этом открываются. Верхний элемент

в этом случае выключается (если

закрыт,

то

считается,

что элемент выключен, если же

открыт, то элемент включен). Сигнал с

выхода

Q

в виде положительного перепада от

к

поступает на вход нижнего элемента и

переключает его с некоторой задержкой

.

При этом

открывается,

,

закрываются

и на выходе

Q

оказывается напряжение

.

Транзистор

и диод

при этом открываются. Верхний элемент

в этом случае выключается (если

закрыт,

то

считается,

что элемент выключен, если же

открыт, то элемент включен). Сигнал с

выхода

Q

в виде положительного перепада от

к

поступает на вход нижнего элемента и

переключает его с некоторой задержкой

.

При этом

![]() закрывается,

закрывается,

![]() ,

,

![]() открываются

и на выходе

оказывается напряжение

(транзистор

открываются

и на выходе

оказывается напряжение

(транзистор

![]() и диод

и диод

![]() при этом закрываются). Нижний элемент

в этом случае включается. Указанное

состояние триггера

– устойчивое.

Далее, рассуждая аналогично, видим

следующее. В соответствии с временной

диаграммой работы триггера (рис.

7.4, г)

в некоторый момент времени сигнал

в виде отрицательного перепада поступает

на вход

и с некоторой задержкой

переключает нижний элемент. При этом

отпирается,

,

закрываются и на выходе

оказывается

напряжение

(транзистор

и диод

при этом открыты). Нижний элемент в этом

случае выключается. Сигнал с выхода

в виде

положительного перепада от

к

поступает

на вход верхнего элемента и переключает

его с некоторой задержкой

.

При этом

закрывается,

,

открываются и на выходе

Q

оказывается напряжение

(транзистор

и диод

)

при этом закрываются). Верхний элемент

в этом случае включается. Указанное

состояние триггера

– устойчивое.

при этом закрываются). Нижний элемент

в этом случае включается. Указанное

состояние триггера

– устойчивое.

Далее, рассуждая аналогично, видим

следующее. В соответствии с временной

диаграммой работы триггера (рис.

7.4, г)

в некоторый момент времени сигнал

в виде отрицательного перепада поступает

на вход

и с некоторой задержкой

переключает нижний элемент. При этом

отпирается,

,

закрываются и на выходе

оказывается

напряжение

(транзистор

и диод

при этом открыты). Нижний элемент в этом

случае выключается. Сигнал с выхода

в виде

положительного перепада от

к

поступает

на вход верхнего элемента и переключает

его с некоторой задержкой

.

При этом

закрывается,

,

открываются и на выходе

Q

оказывается напряжение

(транзистор

и диод

)

при этом закрываются). Верхний элемент

в этом случае включается. Указанное

состояние триггера

– устойчивое.

Таким

образом, анализ переключения триггера

по входам

и

рассмотрен. Выводы из анализа работы

триггера, выполненного на элементах

И–НЕ, аналогичны выводам, сделанным из

анализа работы триггера на элементах

ИЛИ–НЕ, т. е.:

1) сигналы,

поступающие по входам

и

и переключающие триггер, – отрицательные

и соответствуют напряжению

(перепад от

к

);

2)

триггер переключается последовательно;

3) существует

интервал времени, когда на обоих

выходах триггера имеется одинаковая

информация (на рис.

7.4, г

показаны заштрихованные области, когда

на обоих выходах триггера

![]() ),

–явление «риск»;

4) существуют

определенные требования к длительности

сигналов по входам

и

:

),

–явление «риск»;

4) существуют

определенные требования к длительности

сигналов по входам

и

:

![]() ;

;

5)

максимальная частота

;

;

5)

максимальная частота

![]() ;

рабочая частота

;

6) ряд

основных параметров триггера определяются

параметрами логических элементов,

на которых реализован триггер.

;

рабочая частота

;

6) ряд

основных параметров триггера определяются

параметрами логических элементов,

на которых реализован триггер.

Асинхронный RS-триггер на элементах И—ИЛИ—НЕ с прямыми входами

На рис. 7.5, а приведена логическая структура асинхронного RS-триггера с прямыми входами, а на рис. 7.5, б – его условное графическое обозначение. Указанный триггер имеет одинаковую с триггером ИЛИ–НЕ таблицу состояний, полярность входных сигналов, логическое уравнение, обозначение.

Асинхронный RS-триггер с инверсными входами на элементах И — ИЛИ — НЕ

На

рис.

7.5, в

показана логическая структура асинхронного

RS-триггера

с инверсными входами, а на рис.

7.5, г

– его

условное графическое обозначение.

Указанный триггер имеет одинаковую с

триггером на элементах И–НЕ таблицу

состояний, логическое уравнение,

полярность входных сигналов, обозначение.

На рис.

7.5, д

приведена

принципиальная электрическая схема

основного логического элемента

И–ИЛИ–НЕ ТТЛ, а на рис.

7.5, е

– его условное

графическое обозначение. На основе

данного элемента могут быть реализованы

триггеры, логические структуры которых

показаны на рис.

7.5, а,

в.

На

рис.

7.5, в

показана логическая структура асинхронного

RS-триггера

с инверсными входами, а на рис.

7.5, г

– его

условное графическое обозначение.

Указанный триггер имеет одинаковую с

триггером на элементах И–НЕ таблицу

состояний, логическое уравнение,

полярность входных сигналов, обозначение.

На рис.

7.5, д

приведена

принципиальная электрическая схема

основного логического элемента

И–ИЛИ–НЕ ТТЛ, а на рис.

7.5, е

– его условное

графическое обозначение. На основе

данного элемента могут быть реализованы

триггеры, логические структуры которых

показаны на рис.

7.5, а,

в.

А

Таблица

7.3

J

K

Q

0

0

1

0

1

0

1

0

1

1

![]()

JK-триггер – схема с двумя устойчивыми состояниями, которая при одновременном поступлении сигналов на входы осуществляет инверсию предыдущего состояния, имеет два информационных входа: J и К. На рис. 7.6, а приведена логическая структура JK-триггера, а на рис. 7.6, б – его условное графическое обозначение. Логика работы JK-триггера определяется таблицей состояний, минимизированный вид которой представлен табл. 7.3.

Здесь

– изменение

состояния триггера на противоположное.

Из таблицы видно, что при

![]() имеет место

имеет место

![]() ,

а в остальных случаях

JK-триггер

функционирует как

RS-триггер. При

этом вход

J

эквивалентен входу

S,

а вход К

– входу

R.

,

а в остальных случаях

JK-триггер

функционирует как

RS-триггер. При

этом вход

J

эквивалентен входу

S,

а вход К

– входу

R.

Логическое уравнение работы JK-триггера, составленное на основании таблицы состояний, записывается в виде

![]() .

(7.5)

.

(7.5)

Уравнение (7.5) можно прочитать следующим образом: «Единица на выходе триггера будет в том случае, если был сигнал установки единицы и предыдущее состояние триггера соответствовало нулю (на инверсном выходе при этом логическая единица) или если единица была уже в предыдущий момент времени и отсутствовал сигнал установки триггера в нулевое состояние».

Рассмотрим

логику работы

JK-триггера

по схеме, показанной на рис.

7.6, а,

где

Рассмотрим

логику работы

JK-триггера

по схеме, показанной на рис.

7.6, а,

где

![]() ,

–

внутренние установочные входы для

установки триггера в состояние

«1» и

состояние «0» соответственно:

,

–

внутренние установочные входы для

установки триггера в состояние

«1» и

состояние «0» соответственно:

![]() – элементы задержки, применяемые для

обеспечения надежности работы

триггера (элементами задержек могут

служить логические элементы или

дополнительный триггер). Считаем, что

в начальный момент времени триггер

находится в состоянии «0», т. е.

– элементы задержки, применяемые для

обеспечения надежности работы

триггера (элементами задержек могут

служить логические элементы или

дополнительный триггер). Считаем, что

в начальный момент времени триггер

находится в состоянии «0», т. е.

![]()

![]() .

(Установка в «О» обеспечивается сигналом

Уст. «0» по входу

.

При этом на входе

1

конъюнктора

.

(Установка в «О» обеспечивается сигналом

Уст. «0» по входу

.

При этом на входе

1

конъюнктора

![]() имеет место разрешение, а на входе

2

конъюнктора

имеет место разрешение, а на входе

2

конъюнктора

![]() –запрет. Если

–запрет. Если

![]() ,

то сигнал проходит через конъюнктор

,

задержку

,

то сигнал проходит через конъюнктор

,

задержку

![]() на вход S

триггера, переключая его в состояние

«1», т. е.

Q=1,

на вход S

триггера, переключая его в состояние

«1», т. е.

Q=1,

![]() .

Если после переключения триггера, через

определенное время приходит сигнал

.

Если после переключения триггера, через

определенное время приходит сигнал

![]() ,

то через конъюнктор

,

,

то через конъюнктор

,

![]() он поступает на вход

R

и

переключает триггер в состояние «0», т.

е.

он поступает на вход

R

и

переключает триггер в состояние «0», т.

е.

![]() .

Таким образом, общий принцип работы

JK-триггера

можно сформулировать в следующем виде:

при поступлении на вход

J

или К

сигнала

триггер

через соответствующий конъюнктор

установится в единичное (если

)

или нулевое (если

)

состояния. При одновременной подаче

на входы

J

и К

сигналов

«1» триггер

через одну из схем конъюнктора всегда

переключается в противоположное

состояние.

.

Таким образом, общий принцип работы

JK-триггера

можно сформулировать в следующем виде:

при поступлении на вход

J

или К

сигнала

триггер

через соответствующий конъюнктор

установится в единичное (если

)

или нулевое (если

)

состояния. При одновременной подаче

на входы

J

и К

сигналов

«1» триггер

через одну из схем конъюнктора всегда

переключается в противоположное

состояние.

К достоинствам JK-триггера относится то, что он не имеет запрещенных входных комбинаций (в отличие от RS-триггера), является универсальным, т. е. может выполнять функции других триггеров, в том числе RS-, D-, Т-триггеров и др. На рис. 7.6, в показана логическая схема асинхронного JK-триггера на элементах И–НЕ. Это триггер двухступенчатый, с запрещающими связями. В данном триггере роль элемента задержек выполняет дополнительный триггер.

Триггер

(рис.

7.6, в)

состоит из восьми элементов И–НЕ.

Элементы

![]() ,

,

![]() образуют первый триггер для временного

хранения входной информации, а элементы

образуют первый триггер для временного

хранения входной информации, а элементы

![]() ,

,

![]() – второй триггер, определяющий

состояние триггера в целом. Элементы

– второй триггер, определяющий

состояние триггера в целом. Элементы

![]() ,

,

![]() являются ключами первого триггера, а

элементы

являются ключами первого триггера, а

элементы

![]() ,

,

![]() – ключами

второго триггера. Особенностью схемы

является: запрещающие связи

– ключами

второго триггера. Особенностью схемы

является: запрещающие связи

![]() ,

,

![]() входы

входы

![]() ,

,

![]() ;

;

![]() ,

,

![]() – внутренние установочные входы

триггера, обратные связи с выходов Q

и

на входы элементов,

,

.

Принимаем, что в исходном состоянии

– внутренние установочные входы

триггера, обратные связи с выходов Q

и

на входы элементов,

,

.

Принимаем, что в исходном состоянии

![]() ,

,

,

,

![]() ,

,

![]() .

Если J=1,

а K=0,

то

сигнал от

J

проходит через

и устанавливает первый триггер

сигналом «0» в состояние

.

Если J=1,

а K=0,

то

сигнал от

J

проходит через

и устанавливает первый триггер

сигналом «0» в состояние

![]() ,

одновременно запрещая передачу

информации на второй триггер с первого

триггера посредством запрещающей связи

,

действующей на входах элементов

,

.

После окончания действий сигнала но

входу

,

одновременно запрещая передачу

информации на второй триггер с первого

триггера посредством запрещающей связи

,

действующей на входах элементов

,

.

После окончания действий сигнала но

входу

![]() запрет на входах этих элементов снимается

(на связи

был сигнал

разрешения) и информация с первою

триггера (в данном случае с

)

через

сигналом «0» запишет

«1» во второй

триггер. Таким образом, сигнал

записывается в основной триггер, т. е.

запрет на входах этих элементов снимается

(на связи

был сигнал

разрешения) и информация с первою

триггера (в данном случае с

)

через

сигналом «0» запишет

«1» во второй

триггер. Таким образом, сигнал

записывается в основной триггер, т. е.

![]() ,

.

,

.

Если теперь K=1, а J=0, то, рассуждая аналогично, можно убедиться, что триггер переключится в исходное состояние. В общем случае JK-триггер работает в соответствии со сформулированным алгоритмом.