- •1. Радиоэл-ка как обл-ть науки и техники. Осн напр-я соврем радиоэ-ки;

- •4. Активные компоненты радиоэлектроники. Полупроводниковые электронные приборы. Интегральные микросхемы;

- •6. Собственная электропроводность полупроводниковых материалов.

- •7. Типы электрических переходов. Равновесное состояние p-n перехода. Контактная разность потенциалов.

- •8. Прямое смещение p-n перехода.

- •9. Вольтамперная характеристика (вах) p-n перехода. Основные свойства p-n перехода.

- •10Устройство и классификация полупроводниковых диодов. Система условных обозначений диодов;

- •11.Выпрямительные диоды и стабилитроныВыпрямительные диоды

- •12.Варикапы и диоды с барьером Шоттки

- •13.Импульсные диоды и диоды с накоплением заряда (днз) Импульсные диоды этот диод, имеющий малую длительность перех проц-в и предназн для работы в импульсных устройствах.

- •Параметры импульсных диодов

- •Диоды с накоплением заряда

- •14.Туннельные и обращенные диоды

- •15. Определение, устройство и классификация биполярных транзисторов. Система обозначений транзисторов;

- •19. Режимы работы и схемы включения биполярного транзистора

- •20. Принцип действия транзистора

- •Токи в транзисторе ток эмиттера имеет две составляющие: электронную и дырочную

- •21. Формальная модель биполярного транзистора. Система h-параметров биполярного транзистора

- •22. Статические вольтамперные характеристики биполярного транзистора. Влияние температуры на вах биполярного транзистора

- •23. Дифференциальные параметры биполярного транзистора. Определение h-параметров транзистора по статическим вах

- •Определение h–параметров по статическим характеристикам

- •24.Моделирование биполярного транзистора в режиме большого сигнала;

- •25.Малосигнальная модель биполярного транзистора;

- •26 Частотные свойства биполярного транзисторов

- •27 Физические параметры биполярного транзистора. Эквивалентные схемы замещения биполярного транзистора.

- •28.Основные параметры биполярного транзистора;

- •29. Классификация сигналов. Гармонический анализ сигналов

- •30. Спектральный анализ периодических сигналов. Комплексная форма ряда Фурье

- •31. Спектральный анализ непериодических сигналов

- •32. Амплитудно-модулированные сигналы

- •33. Частотно-модулированные сигналы

- •34. Фазомодулированные сигналы

- •35. Случайные сигналы

- •36. Моментные функции второго порядка;

- •37)Спектральный анализ случайных сигналов. Помехи

- •38. Характеристики линейных цепей. Комплексный коэффициент передачи;

- •39. Амплитудно-частотная характеристика.

- •40. Переходная характеристика;

- •41. Импульсная характеристика;

- •42. Методы исследования линейных электрических цепей;

- •43. Классификация аналоговых электронных устройств.

- •Классификация аналоговых электронных устройств

- •44. Основные параметры аналоговых электронных устройств;

- •45. Основные характеристики аналоговых электронных устройств;

- •46. Классификация усилительных устройств;

- •47. Понятие рабочей точки;

- •48. Способы задания рабочей точки;

- •49. Способы стабилизации рабочей точки;

- •50. Основные режимы работы усилительных каскадов;

- •51. Обратные связи в усилительных каскадах;

- •52. Усилительный каскад по схеме с общим эмиттером;

- •Эквивалентная схема усилительного каскада в диапазоне средних частот

- •53. Усилительный каскад по схеме с общей базой;

- •54. Усилительный каскакаскад по схеме с общим коллектором;

- •55.Усилительный каскад с ои

- •56.Усилительный каскад с общим стоком (истоковый повторитель)

- •57. Двухтактный усилительный каскад

- •58. Резонансный усилитель

- •59. Усилители постоянного тока (упт)

- •60.Дифференц усил каскад

- •61. Операционные усилители

- •62. Понятие автоколебат с-мы. Принцип возникновения колебаний.

- •63. Основные теории процессов в автогенераторе;(без линейной теории)

- •64. Основные схемы lc-генераторов;

- •65. Трехточечные схемы генераторов. Кварцевые генераторы;

- •67. Режимы работы автогенератора. Автоген-ры с автоматич смещением.

- •1 .10.1. Однокаскадная схема rc-генератора

- •1.10.2. Двухкаскадная схема -генератора rc

- •69. Модуляция электрических сигналов;

- •70. Амплитудные модуляторы;

- •71. Частотные модуляторы;

- •72. Фазовые модуляторы;

- •73. Детектирование электрических сигналов;

- •74. Амплитудные детекторы

- •Основные хар-ки и параметры амплитуд. Детектора(из инета).

- •75. Фазовые детекторы;

- •76. Частотные детекторы

- •77. Электронные ключевые схемы. Электронные ключи на биполярных транзисторах;

- •78. Способы повышения быстродействия ключей на биполярных транзисторах;

- •79. Электронные ключи на полевых транзисторах

- •80. Алгебра логики и ее основные законы(дописать)

- •81. Диодно-транзисторная логика (дтл);

- •82. Транзисторно-транзисторная логика (ттл);

- •83. Эмиттерно-связанная логика (эсл);

- •84. Интегральная инжекционная логика.

- •86. Основные параметры цифровых интегральных схем;

- •87. Система обозначений цифровых интегральных схем;

- •88. Триггеры.

- •Параметры триггеров

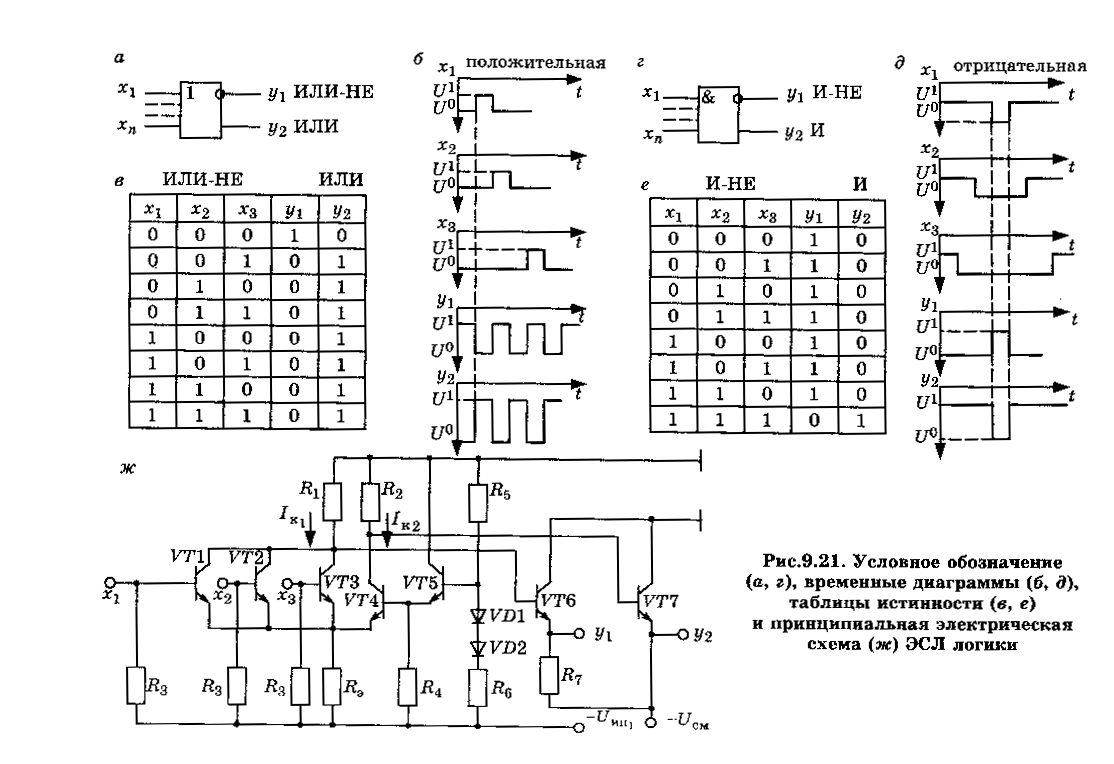

83. Эмиттерно-связанная логика (эсл);

Цифровые микросхемы ЭСЛ составляют схемы на переключателях тока с объединенными эмиттерами, обладающие по сравнению с другими типами цифровых схем наибольшим быстродействием и большой потребляемой мощностью.

В зависимости от сп-ба кодирования входной инф-и ("1" и "0") одна и та же схема может реализовать ф-ии ИЛИ–НЕ, ИЛИ для положительной логики, либо ф-ии И–НЕ, И для отрицательной логики.

Рассмотрим принцип работы схемы для положительной логики (ф-я ИЛИ-НЕ)

Если

на все

логические входы подается напряжение

низкого уровня,

соответств-ее логич нулю, то тр-ры

VТ1–VТ3

закрываются, а тр-р VТ4

открывается, так как напряж-е на его

базе становится выше, чем на базах

входных тр-ров. Через открытый тр-р

протекает ток

![]() ,

значение которого задается Rэ,

и создает падение напряж-я на резисторе

R2.

Потенциал коллектора тр-ра VТ4

при этом пониж-ся и подается на вход

эмиттерного повторителя, собранного

на тр-ре VТ7.

На выходе эмиттерного повторителя

получается низкий уровень напряж-я,

соответствующий логич-му нулю.

,

значение которого задается Rэ,

и создает падение напряж-я на резисторе

R2.

Потенциал коллектора тр-ра VТ4

при этом пониж-ся и подается на вход

эмиттерного повторителя, собранного

на тр-ре VТ7.

На выходе эмиттерного повторителя

получается низкий уровень напряж-я,

соответствующий логич-му нулю.

В

это же время через R1

левой ветви токового ключа протекает

небольшой обратный ток

![]() .

Потенциал коллектора тр-ра VТ3

повыш-ся и поступает на базу эмиттерного

повторителя тр-ра VТ6.

На выходе

тр-ра VT6

имеем большой потенциал, логич-ю

единицу, при

этом выполняется логич операция ИЛИ–НЕ.

.

Потенциал коллектора тр-ра VТ3

повыш-ся и поступает на базу эмиттерного

повторителя тр-ра VТ6.

На выходе

тр-ра VT6

имеем большой потенциал, логич-ю

единицу, при

этом выполняется логич операция ИЛИ–НЕ.

Предпол-м,

что на один

из входов

(вход 1) подается напряж-е

логич единицы,

а на остальных входах действует логич

нуль. Под действием вх-го сигнала тр-р

VТ1

отрывается, через коллекторную и

эмиттерную цепь протекают большие токи

и Iэ.

Ток Iэ

создает падение напряж-я на сопрот-и

резистора Rэ,

которое резко уменьш-т напряж-е

![]() ,

тр-р VТ4

закрывается. Перепады напряжений

коллекторных цепей тр-ров VТ1,

VТ4

подаются на входы соответств-х эмиттерных

повторителей. Т обр по выходу тр-ра VТ6

выполняется логич операция ИЛИ–НЕ, а

по выходу тр-ра VТ7 –

логич операция ИЛИ. Воздействие вх-го

сигнала приводит к переключ-ю тока

эмиттера Iэ,

который проходит в завис-ти от амплитуды

вх-го сигнала то через левую, то через

правую ветви, и при этом на выходе

создаются низкий и высокий уровни

напряж-я одновременно.

,

тр-р VТ4

закрывается. Перепады напряжений

коллекторных цепей тр-ров VТ1,

VТ4

подаются на входы соответств-х эмиттерных

повторителей. Т обр по выходу тр-ра VТ6

выполняется логич операция ИЛИ–НЕ, а

по выходу тр-ра VТ7 –

логич операция ИЛИ. Воздействие вх-го

сигнала приводит к переключ-ю тока

эмиттера Iэ,

который проходит в завис-ти от амплитуды

вх-го сигнала то через левую, то через

правую ветви, и при этом на выходе

создаются низкий и высокий уровни

напряж-я одновременно.

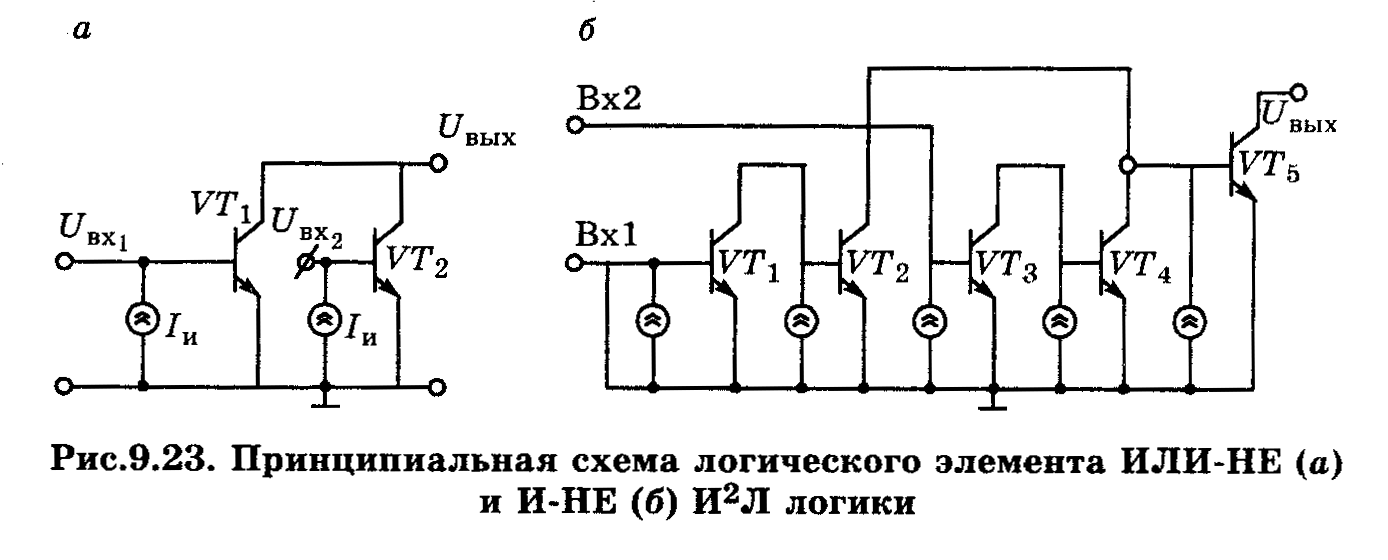

84. Интегральная инжекционная логика.

Основой элементов интегральной инжекционной логики является ключ, представляющий собой транзистор с инжекционным питанием.

Принцип работы схемы следующий.

Если хотя бы на один из входов схемы подать сигнал логической единицы, то ток от генератора тока Iи потечет в базу транзистора, транзистор открывается и переходит в режим насыщения. Выходное напряжение соответствует логическому нулю.

Если на обоих входах действуют сигналы логического нуля, т.е. входы закорочены, токи Iи не будут проходить в базу транзисторов, а потекут во входные цепи. Транзисторы VТ1, VТ2 будут закрыты, их выходное напряжение соответствует логической единице.

Таким образом параллельное соединение нескольких ключей образует логический элемент ИЛИ–НЕ.

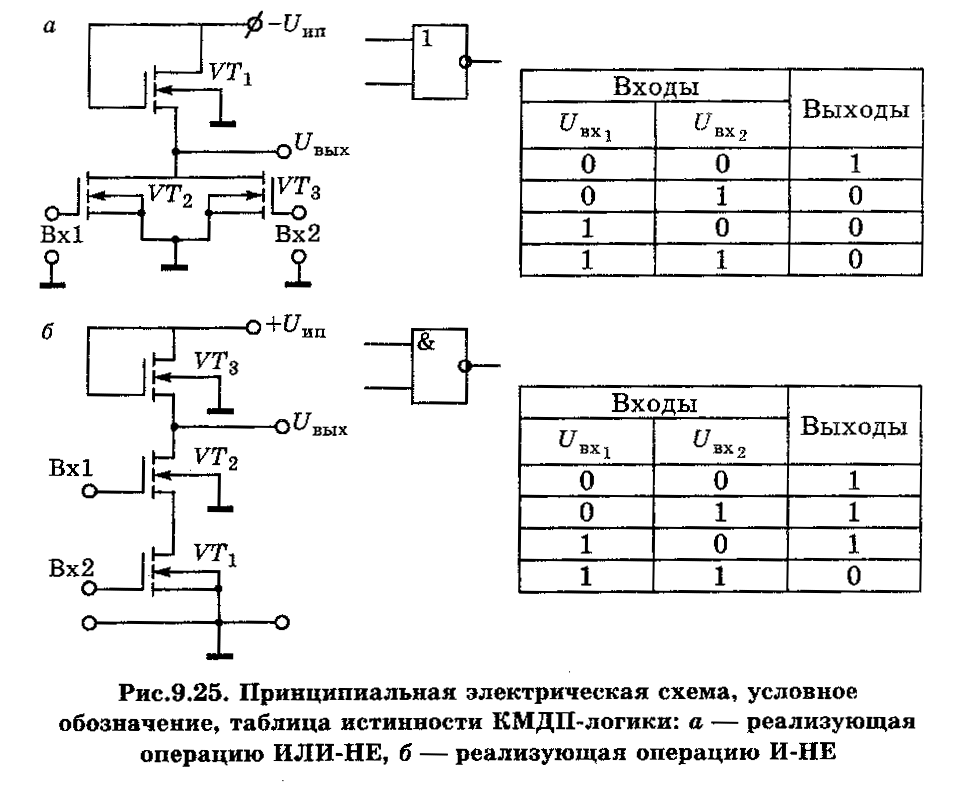

№85. Логические элементы на МДП-транзисторах

Практическое применение при разработке интегральных логических схем получили полевые транзисторы с МДП структурой и индуцированным каналом n– или p–типов. Наибольшее распространение получили две разновидности логических схем:

1. МДП-логика с нагрузочным транзистором.

2. Логика на комплементарных транзисторах.

Особенностью интегральных микросхем на МДП-транзисторах является возможность реализации любых логических функций с помощью только МДП-транзисторов.

Кроме того МДП-транзисторы имеют следующие достоинства:

– возможность использования транзистора в качестве нагрузки, что обеспечивает высокую однородность интегральных схем;

– высокая помехоустойчивость (2…6 В) по сравнению с 0,6 В для биполярных транзисторов;

– малая мощность рассеяния в статическом режиме, особенно при использовании в схеме транзисторов разного типа проводимости канала;

– используется один источник питания, что обеспечивает простоту схемы;

– устойчивость к нейтронной составляющей радиационного воздействия.

К недостаткам МДП-транзисторов следует отнести:

– большое пороговое напряжение;

– высокое напряжение питания;

– относительно невысокое быстродействие;

– малая крутизна, что снижает нагрузочную способность элементов по току и ухудшает отношение скорости переключения к мощности рассеяния.

Схемы на МДП-транзисторах с каналом p-типа имеют малую стоимость и более технологичны, имеют время прохождения сигнала в 8…10 раз меньше, чем схемы на транзисторах с каналом n–типа. По быстродействию схемы на МДП-транзисторах с каналом n–типа не уступают ТТЛ схемам, обеспечивая меньшую мощность рассеяния и более высокую плотность размещения компонентов, чем ТТЛ схемы.

Логические интегральные микросхемы на МДП-транзисторах бывают следующих типов: статические, динамические и квазистатические. Элементной базой для построения таких схем являются простейшие логические элементы, реализующие логические функции И–НЕ (схемы типа ЛА), ИЛИ–НЕ (схемы типа ЛЕ), И (схемы типа ЛИ), НЕ (схемы типа ЛН) и комбинированные (схемы типа ЛП, ЛС). Использование базовых элементов позволяет построить цифровое устройство с любым алгоритмом функционирования. В логических схемах получили распространение схемы статического типа.

Типовые схемы МДП-логики с нагрузочным транзистором, реализующие логические функции ИЛИ–НЕ и И–НЕ, показаны на рис. 9.25. В этих двух схемах транзисторы VТ1 и VТ2 выполняют роль ключевых элементов. Транзисторы VТ3 выполняют роль нагрузки. Ключевые транзисторы можно соединять последовательно (рис. 9.25,б) и параллельно (рис. 9.25,а). Параллельное соединение нескольких ключевых транзисторов ограничено снижением уровня логического нуля на выходе схемы за счет падения напряжения на нагрузке от суммарного тока утечки всех ключевых МДП–транзисторов. Поскольку ток утечки мал и составляет порядка 10-10 А, то число параллельно включенных транзисторов может достигать 10 и более.

При последовательном соединении в цепь между нагрузкой и землей включают несколько МДП-транзисторов. При этом исток нижнего МДП-транзистора подключается к земле, его сток – к истоку вышестоящего и т.д. Протекание тока через нагрузку к земле может происходить только, если открыты все ключевые транзисторы. Обычно число последовательно соединяемых транзисторов не более трех. Это связано с тем, что с увеличением числа последовательно соединенных транзисторов повышается уровень логического нуля на выходе схемы, ибо суммарное сопротивление открытых ключевых транзисторов возрастает. Последовательное включение требует применения МДП-транзисторов с более высокой крутизной характеристик, чем при параллельном включении. Последовательное включение транзисторов усложняет топологию и уменьшает степень интеграции, ухудшается быстродействие, но позволяет создавать логические микросхемы, обладающие большей гибкостью, чем микросхемы на биполярных транзисторах.

Реализация функции ИЛИ–НЕ осуществляется схемой, представленной на рис. 9.25,а, там же представлено условное обозначение и таблица истинности.

При подаче на один из входов положительного сигнала логической единицы соответствующий логический (ключевой) транзистор открывается. Если одновременно на все входы подается логическая единица, то все логические транзисторы открыты. Выходное напряжение схемы равно падению напряжения на открытых логических транзисторах и близко к нулю. Если на входах отсутствует сигнал, т.е. действует логический нуль, то логические транзисторы закрыты, выходное напряжение приближается по величине к источнику питания.

Последовательное включение транзисторов позволяет реализовать логическую операцию И–НЕ (рис. 9.25,б). При одновременной подаче положительных сигналов логической единицы на все входы, все МДП-транзисторы открываются, и на выходе схемы – логический нуль.

Достоинством логики этого типа является простота схем, применение транзисторов одного типа проводимости, высокое входное сопротивление порядка 1012 Ом, высокая нагрузочная способность (n = 10…20), технологичность в изготовлении. Недостатком логики данного типа является низкое быстродействие, обусловленное влиянием паразитной емкости.

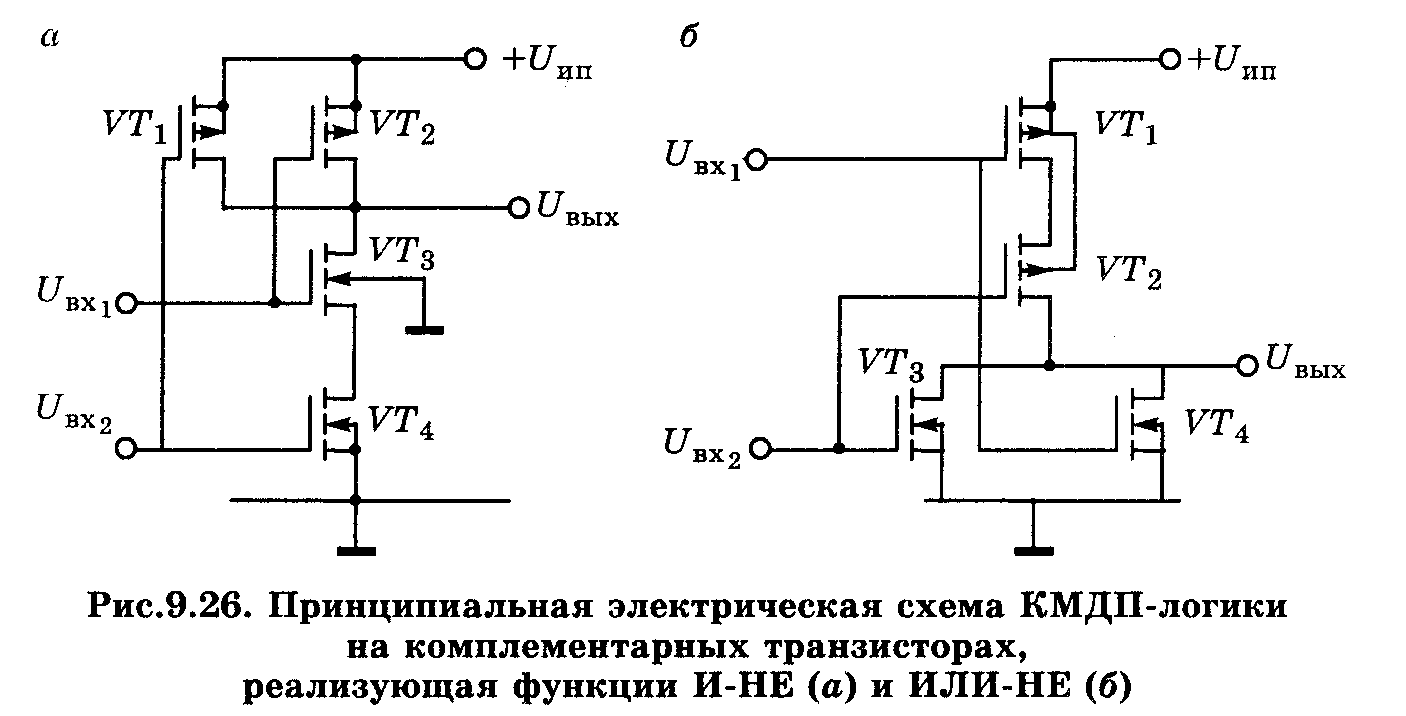

Наиболее перспективными являются логические схемы, выполненные на комплементарных МДП-транзисторах (КМДП). Комбинируя различные включения этих транзисторов можно получить заданную логическую функцию. Если транзистор с каналом n–типа непосредственно подключен к шине "земля", а транзистор с каналом p–типа – к источнику питания, то логическая схема работает в режиме положительной логики. На рис. 9.26,а и б представлены схемы КМДП-логики, реализующие логические операции И–НЕ и ИЛИ–НЕ.

Реализация логической функции И–НЕ осуществляется последовательным соединением МДП-транзисторов с каналом n–типа и параллельным соединением МДП-транзисторов с каналом p–типа, которые открыты при напряжениях затворов, близких к нулю. Предположим, что на вход 1 (рис. 9.26,а) подается сигнал логического нуля, транзистор VТ3 закрыт, а транзистор VТ2 открыт и выходное напряжение близко к напряжению источника питания. Если на все входы подается сигнал логической единицы, то транзисторы VТ3 и VТ4 открыты, а транзисторы VТ1 и VТ2 закрыты. Выходное напряжение стремится к потенциалу земли – (логический нуль).

Для построения схемы ИЛИ–НЕ требуется последовательное включение МДП-транзисторов с каналом p–типа и параллельное включение транзисторов с каналом n–типа (положительная логика) рис. 9.26,б.

Схема работает так же, как и предыдущая. Когда на всех входах действует высокий потенциал логической единицы, транзисторы VТ3 и VТ4 открываются, а p–канальные транзисторы закрываются. Выходное напряжение определяется падением напряжения на открытых транзисторах и соответствует логическому нулю. Если на один из входов подается сигнал логической единицы, то этот n–канальный транзистор открывается, и выходное напряжение определяется этим открытым транзистором.

Микросхемы на КМДП транзисторах потребляют очень малую мощность при сравнительно высоком быстродействии.

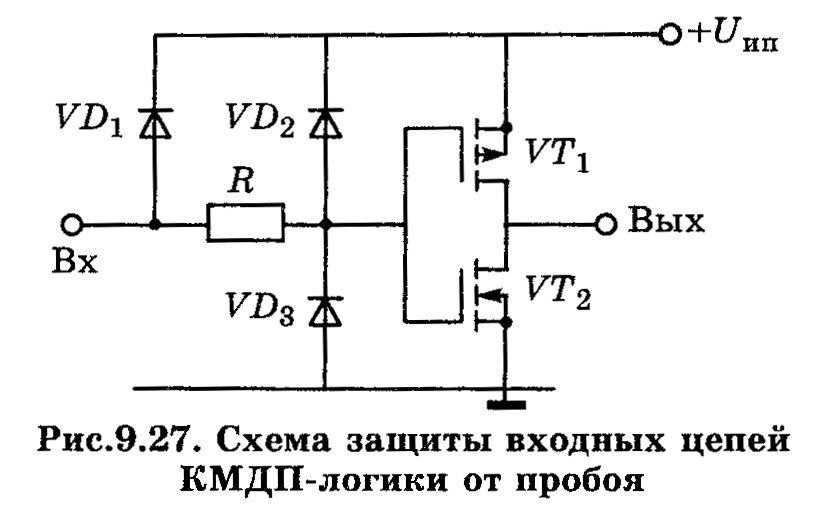

З атвор

транзистора МДП и подложка, разделенные

слоем диэлектрика, образуют конденсатор.

Емкость конденсатора невелика, а

сопротивление утечки очень велико, что

способствует накоплению статических

зарядов. Электрическая прочность

тонкого слоя диэлектрика составляет

порядка 150…200 В. Статический заряд

малой энергии, попав на затвор, может

произвести пробой диэлектрика. Для

защиты транзистора от пробоя каждый

вход современных микросхем КМДП-логики

снабжается защитной цепью (рис. 9.27).

атвор

транзистора МДП и подложка, разделенные

слоем диэлектрика, образуют конденсатор.

Емкость конденсатора невелика, а

сопротивление утечки очень велико, что

способствует накоплению статических

зарядов. Электрическая прочность

тонкого слоя диэлектрика составляет

порядка 150…200 В. Статический заряд

малой энергии, попав на затвор, может

произвести пробой диэлектрика. Для

защиты транзистора от пробоя каждый

вход современных микросхем КМДП-логики

снабжается защитной цепью (рис. 9.27).

Подложки каждого из транзисторов соединены с их истоками, что предотвращает открывание p–n переходов. Затворы в обоих транзисторах объединены, и на них подается входной сигнал. Особенностью схемы защиты является наличие защитных VD1–VD3 диодов, шунтирующих затворы входных транзисторов и препятствующих пробою диэлектрика под затвором от действия электростатического заряда. Защитные диоды смещаются в обратном направлении. Резистор R1 (0,2…2 кОм) совместно с барьерными емкостями диодов VD2 и VDЗ образуют интегрирующую цепь, это уменьшает скорость нарастания напряжения на затворе, при котором диоды VD2, VD3 успевают открыться.

Если входное напряжение Uвх подается от источника с малым внутренним сопротивлением и амплитудой больше Uип, то через VD1 будет протекать большой прямой ток. Поэтому при использовании таких схем рекомендуется включать напряжение питания раньше входного сигнала, а при выключении – наоборот.

В тех узлах, где по необходимости на входы поступают напряжения Uвх>Uип, следует в цепь входа включать резисторы, ограничивающие входной ток на уровне 1…2 мА.

На неиспользованные входы КМДП-логики подают постоянный потенциал (+Uип или 0 в зависимости от функции элемента) или объединяют их с другими, задействованными входами.